Manufacture method for flip-chip and bare chip assembly

A manufacturing method and bare chip technology, applied in the direction of electrical components, electrical solid devices, semiconductor devices, etc., to achieve the effect of mitigating potential damage, precise electroplating position, and strengthening protection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the object, technical solution and advantages of the present invention clearer, various embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. However, those of ordinary skill in the art can understand that, in each implementation manner of the present invention, many technical details are provided for readers to better understand the present application. However, even without these technical details and various changes and modifications based on the following implementation modes, the technical solution claimed in each claim of the present application can be realized.

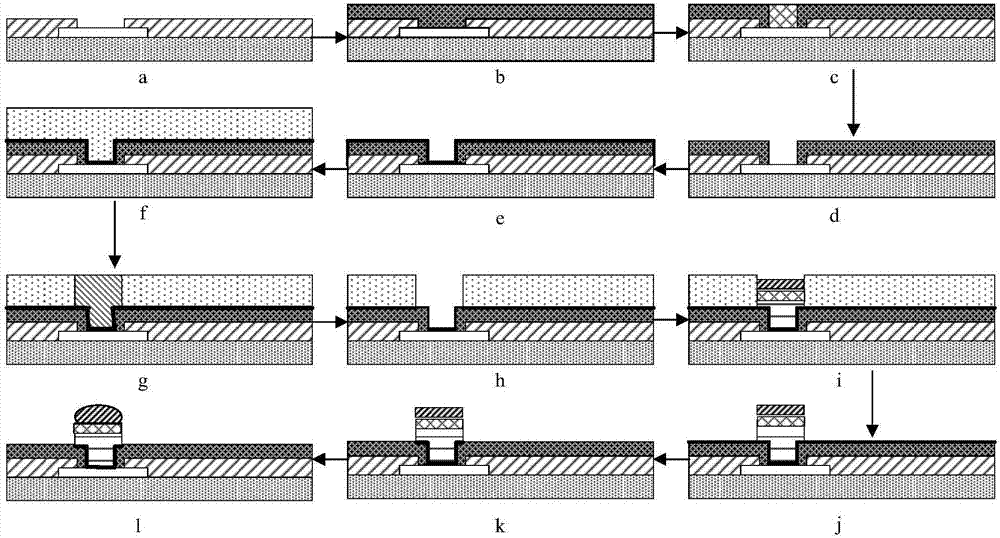

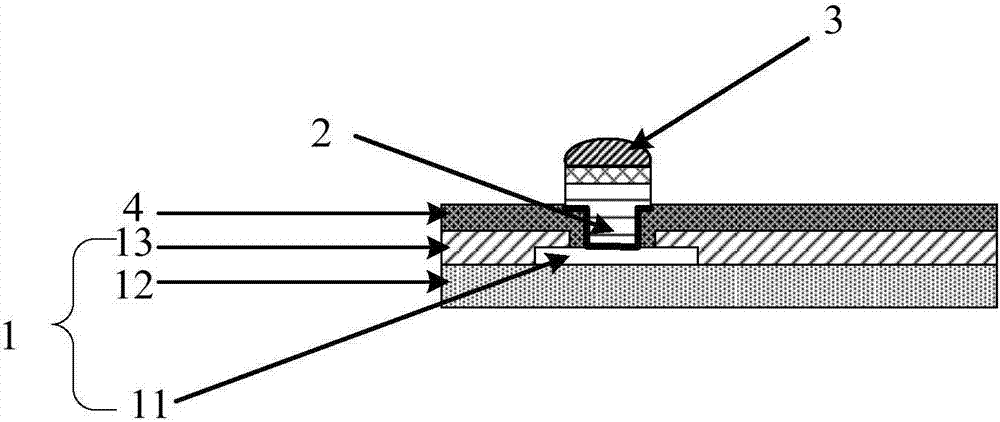

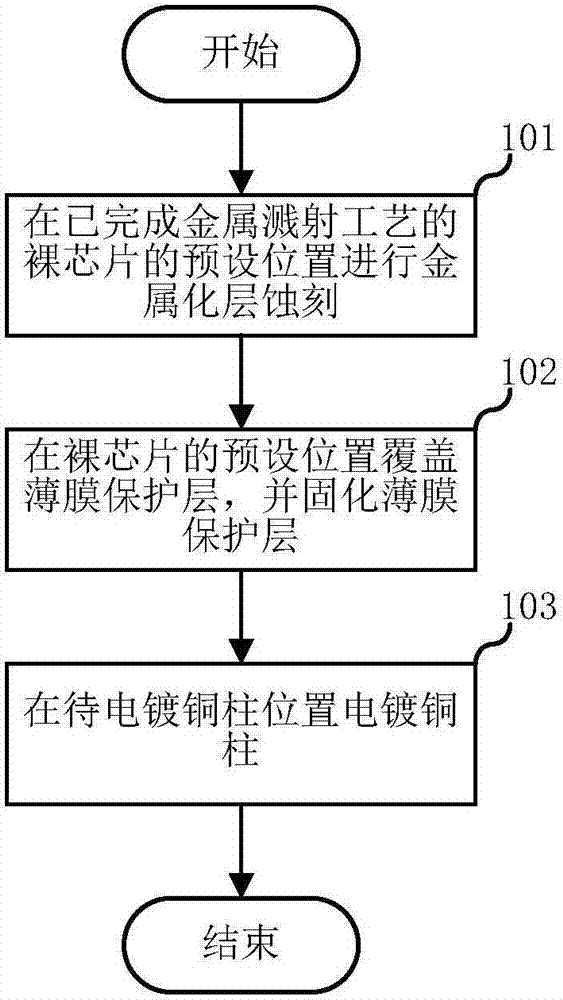

[0021] The first embodiment of the present invention relates to a flow chart of a method for manufacturing a flip chip, the specific process is as follows image 3 shown. In this embodiment, for ease of understanding, it is also combined with Figure 4(a) to Figure 4(m) The structural schematic diagrams of the bare chip co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More