Multiple-way switching PUF (physical unclonable function) circuit and serial number output circuit

A switching circuit and multi-channel switching technology, used in the protection of internal/peripheral computer components, etc., can solve the problems of unsatisfactory chip reliability uniqueness, increase system security, and low commercial possibility, and achieve uniqueness and reliability. The ideal value of the performance index, avoiding large errors, and reducing the risk of tape-out

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

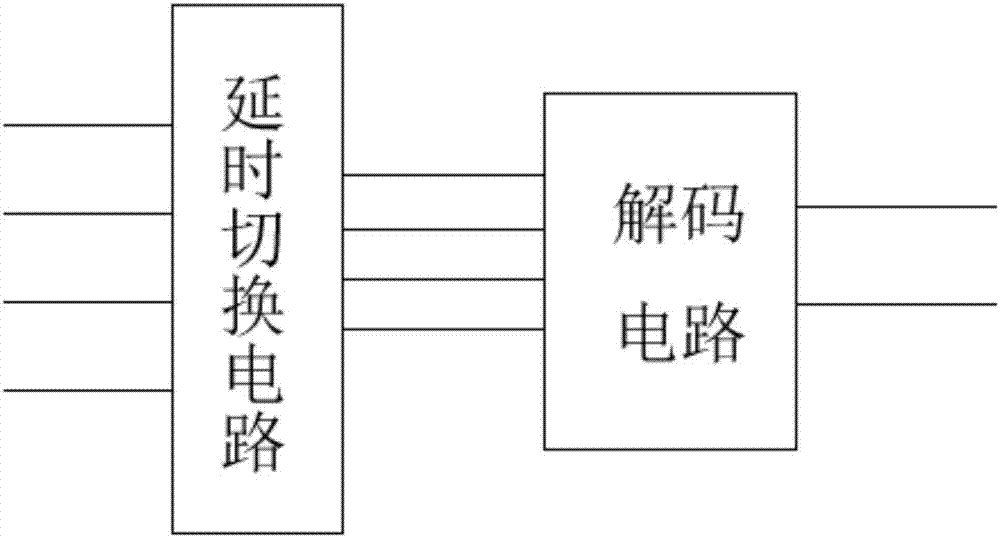

[0057] This embodiment describes in detail the structure and principle of a multiplexable PUF circuit provided by the present invention, see figure 1 , is a schematic diagram of the connection of the PUF circuit. The input and output terminals in the figure are only used to illustrate the connection relationship between the delay switching circuit and the decoding circuit. The specific number of input terminals and output terminals is not subject to the figure. PUF The circuit mainly includes:

[0058] Delay switching circuit, the delay switching circuit has a key input terminal, multiple signal input terminals and multiple signal output terminals, the key input terminal corresponds to the input of a two-digit key, and multiple signal input terminals are connected to the same external pulse signal , the delay switching circuit selects the same pulse signal input from different signal input terminals, converts the pulse signal into delayed signals of different rates, and output...

Embodiment 2

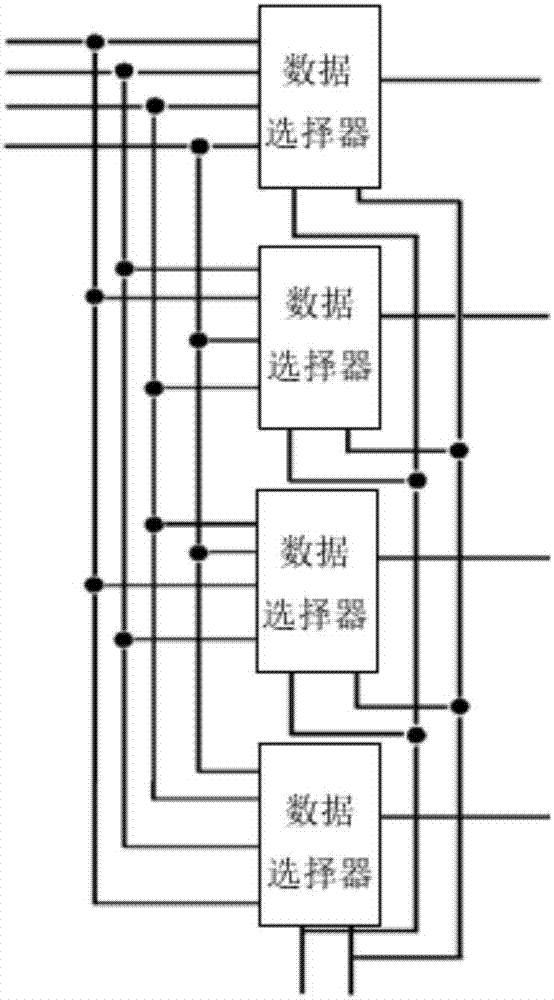

[0064] This embodiment is based on the content recorded in Embodiment 1, and describes in detail the PUF circuit that uses four data selectors to realize 4 delay paths. The larger errors generated during the process are dispersed inside the circuit, thereby improving randomness, reliability, and uniqueness.

[0065] The connection relationship between the delay switching circuit and the decoding circuit has been stated in detail in Embodiment 1. On the basis of Embodiment 1, the delay switching circuit in the present embodiment selects four 4 to 1 data selectors to form, see Figure 4 , in addition, the principles of data selectors such as 2-to-1, 8-to-1, and 16-to-1 are similar, and details are not described here. For the convenience of explanation, the four data selectors are respectively named as the first data selector, the second data selector, the third data selector and the fourth data selector from top to bottom. The data input terminals of each data selector Accordin...

Embodiment 3

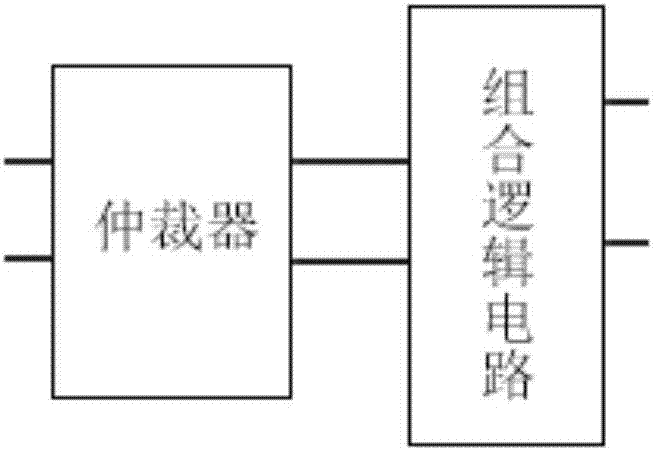

[0077] In order to further increase the randomness of the PUF circuit in the present invention, on the basis of Embodiment 1 and Embodiment 2, the signal input terminals and signal output terminals of n delay switching circuits can be connected in series sequentially, such as Figure 8 As shown, each delay switching circuit corresponds to the 2-bit input of the key, and n series delay switching circuits support the input of 2n-bit keys. It should be noted that the input key needs to follow the delay switching circuit. The connection sequence is from left to right, and from the lowest bit to the highest bit of the key, one unit per two bits is input to the key input terminal of the corresponding delay switching circuit.

[0078] The specific structures of the delay switching circuit and the decoding circuit in this embodiment have been specifically stated in Embodiment 1 and Embodiment 2, and will not be repeated here. Compared with embodiment 1 and embodiment 2, embodiment 3 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More