Transistor forming method

A technology of transistors and body regions, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems that the breakdown voltage of LDMOS transistors needs to be further improved, and achieve size reduction, control capability, and conductance reduction. The effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] It can be seen from the background art that the breakdown voltage of the LDMOS transistor in the prior art needs to be further improved. The reason for the process analysis problem of forming LDMOS transistors in combination with the existing technology:

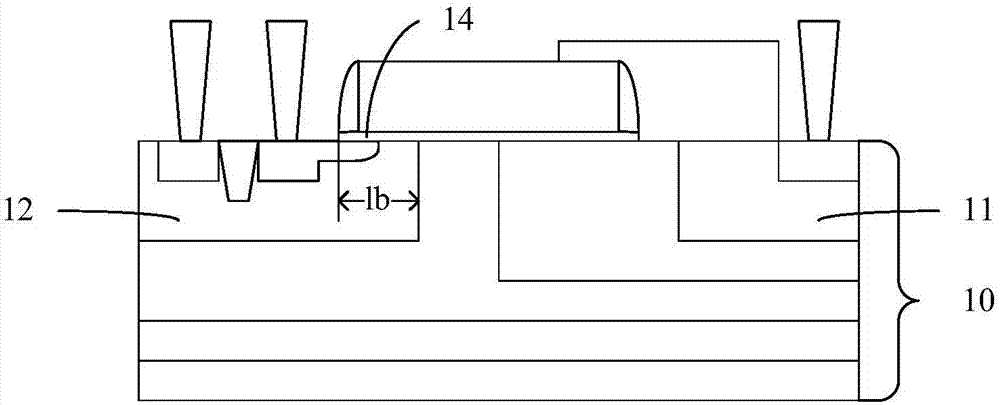

[0032] refer to figure 1 , shows a schematic cross-sectional structure of an LDMOS transistor.

[0033] like figure 1 As shown, the LDMOS transistor includes a substrate 10; an N-type drift region 11 and a P-type body region 12 with a certain interval in the substrate 10; a gate structure 14 on the substrate 10, and the gate structure 14 is located in a part The P-type body region 12 , part of the N-type drift region 11 and the substrate 10 between the P-type body region 12 and the N-type drift region 11 .

[0034] When forming the LDMOS transistor, the gate structure 14 is formed by an etching process after the N-type drift region 11 and the P-type body region 12 . Therefore, in order to ensure that the gate stru...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More