A system and method for increasing the data transmission rate of a vector network analyzer

A vector network analysis, data transmission rate technology, applied in transmission systems, electrical digital data processing, instruments, etc., can solve the problems of reduced bus effective bandwidth, slow data transmission rate, complicated system hardware connection, etc., to improve the data transmission rate. and efficiency, improving robustness and cost-effectiveness, and reducing manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

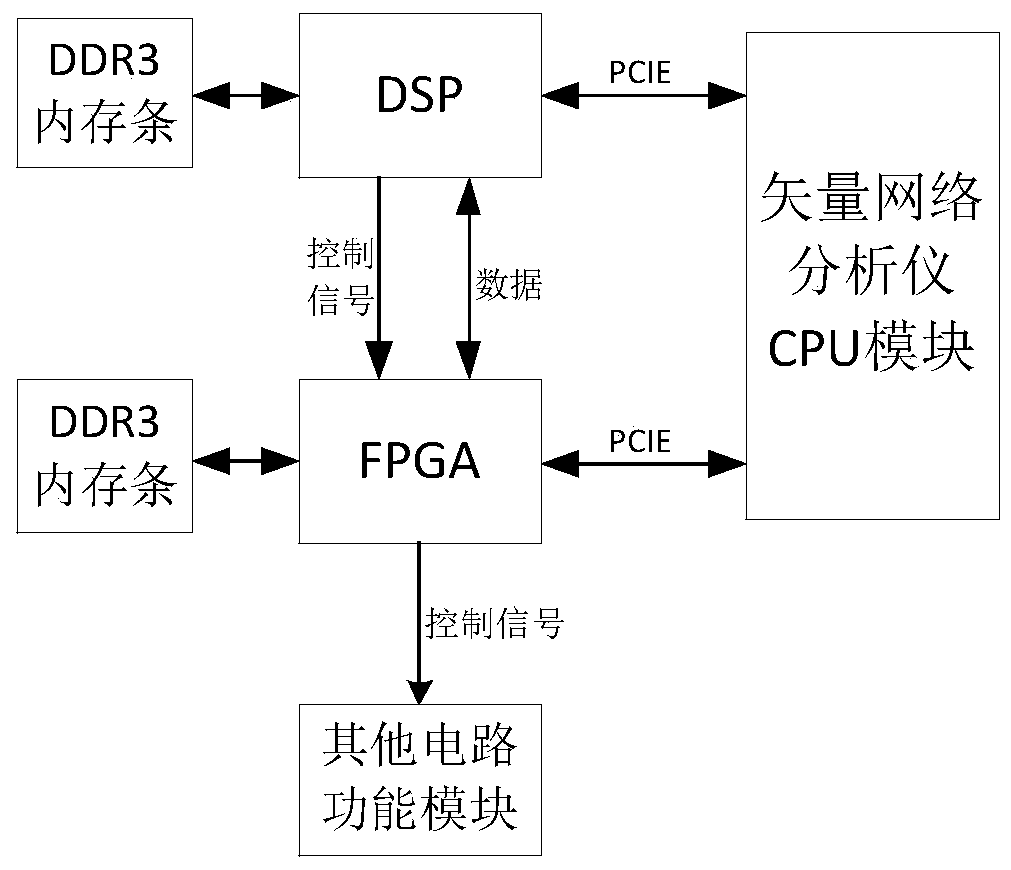

[0045] The invention discloses a system for improving the data transmission rate of a vector network analyzer, such as figure 1 shown, including:

[0046] CPU module, DSP module and FPGA module. The CPU module of the vector network analyzer is connected to the DSP module and the FPGA module respectively through two independent PCIE bus links.

[0047] The PCIE bus of the present invention adopts the popular point-to-point topology in the industry at present. Compared with the shared parallel architecture of the PCI bus and earlier computer buses, each device on the PCIE bus is connected to the root system by a separate serial link ( Host), without requesting bandwidth from the entire bus, can increase the data transfer rate to a very high frequency, reaching the high bandwidth that PCI cannot provide.

[0048] The DSP module and the FPGA mod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More