ldmos device with esd protection function and its layout

An ESD protection and device technology, applied in the direction of semiconductor devices, electrical solid devices, electrical components, etc., can solve problems such as false opening, poor electrostatic discharge capability, device or chip burnout, etc., to avoid latch-up effect, improve holding voltage, The effect of high electrostatic discharge capability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

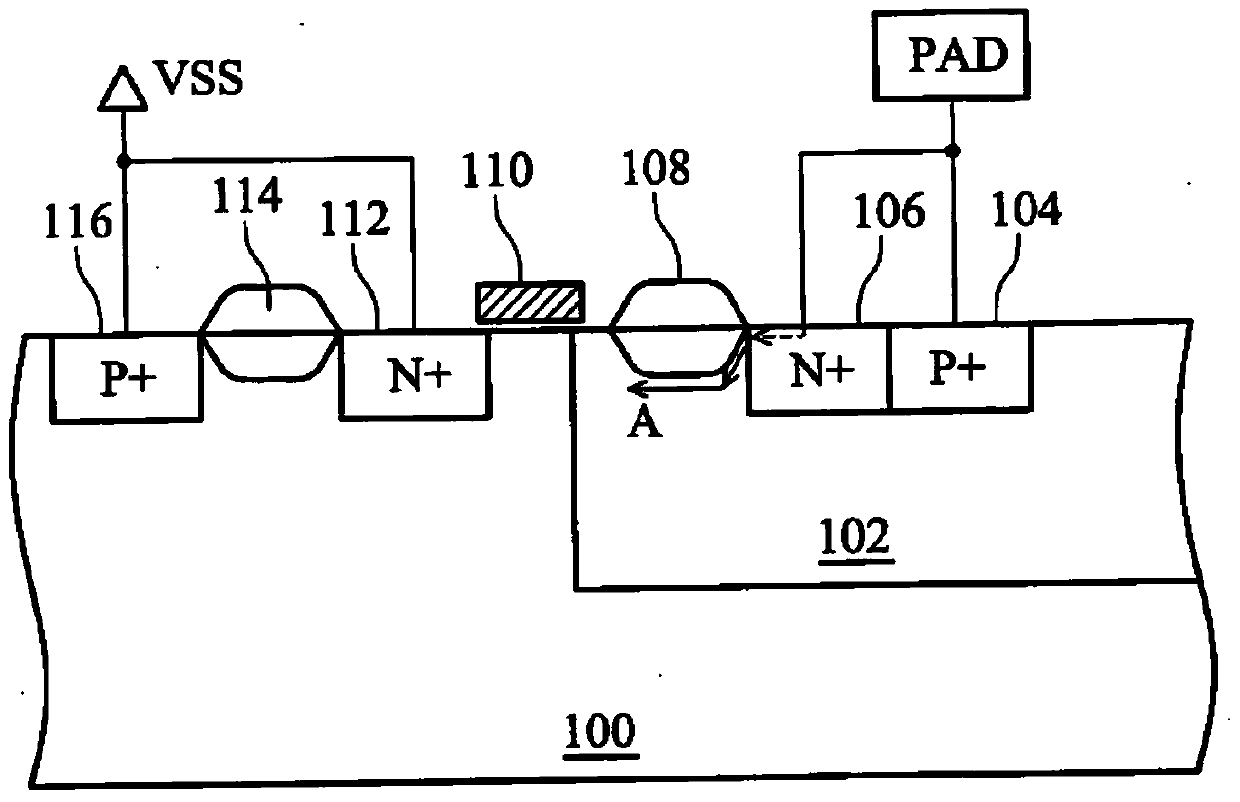

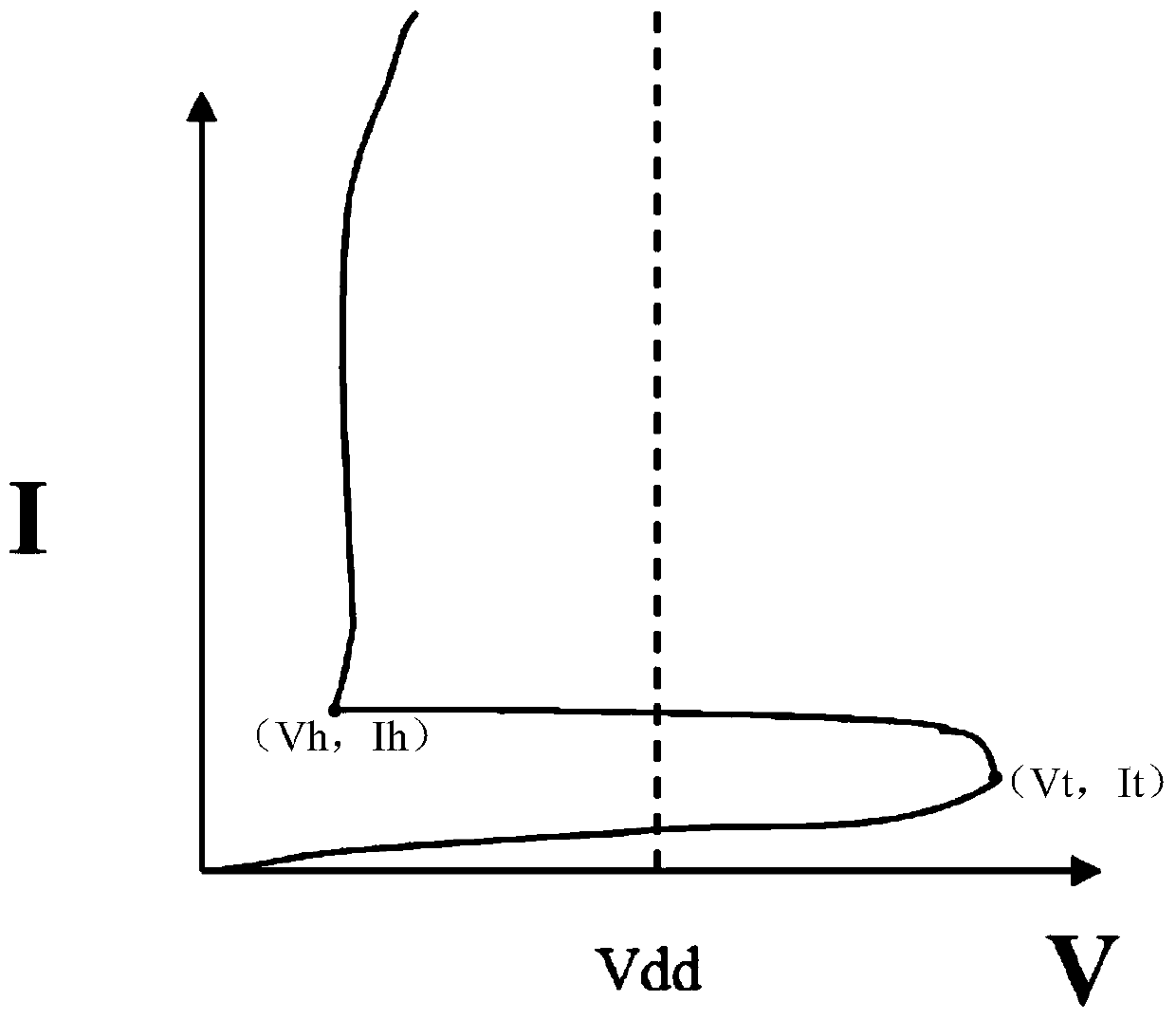

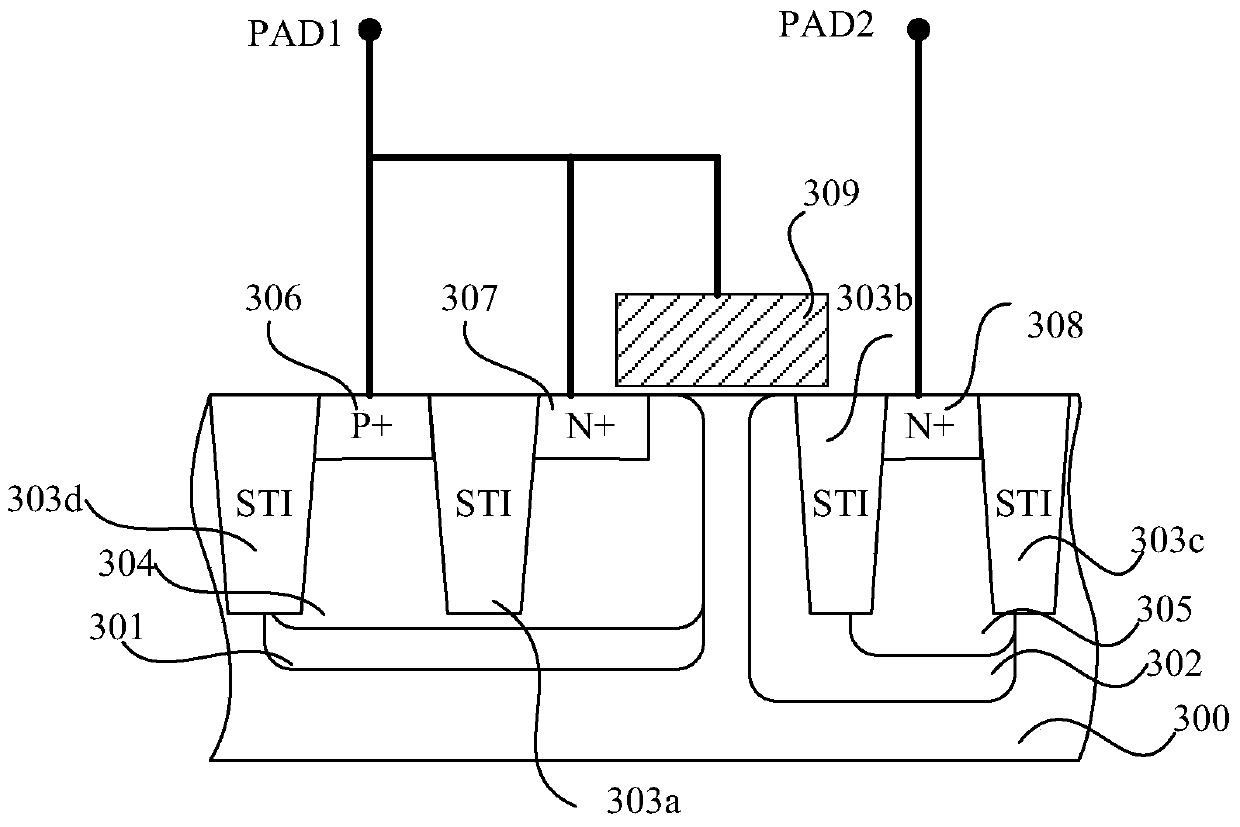

[0032] Please refer to Figure 3A The present invention proposes an LDMOS device with ESD protection function, comprising a P-type substrate 300 with a first deep P well 301 and a deep N well 302 arranged laterally; the surface of the first deep P well 301 is laterally arranged with The first P+ implant region 306 and the first N+ implant region 307, the first P+ implant region 306 and the first N+ implant region 307 are isolated by the first isolation structure 303a, and the first N+ implant region 307 is used as the LDMOS device The first source region (source); the surface of the deep N well 302 is provided with a second N+ implantation region 308, and the second N+ implantation region 308 is used as the drain region (drain) of the LDMOS device, passing through the first N+ implantation region 307 The second isolation structure 303b is isolated. Wherein, a first P well implantation region 304 having a shallower depth than the first deep P well 301 is provided in the first ...

Embodiment 2

[0052] Please refer to Figure 3B , the present embodiment provides an LDMOS device with ESD protection function, including a P-type substrate 300 provided with a first deep P well 301a, a deep N well 302 and a second deep P well 301b in sequence along the lateral direction; the first A first P+ implantation region 306a and a first N+ implantation region 307a are arranged laterally on the surface of the deep P well 301a, and the first P+ implantation region 306a and the first N+ implantation region 307a are separated by a first isolation structure 303a, and the first An N+ implantation region 307a is used as the first source region (source) of the LDMOS device; the surface of the deep N well 302 is provided with a second N+ implantation region 308, and the second N+ implantation region 308 is used as the drain region (drain) of the LDMOS device, and The first N+ implantation region 307a is isolated by the third isolation structure 303b, the surface of the second deep P well 30...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More