A fin field-effect transistor and a manufacturing method thereof

A technology of field effect transistors and manufacturing methods, which is applied in the field of fin field effect transistors, can solve the problems of small size, difficult application of fin field effect transistors, and inability of fin field effect transistors to withstand excessive voltage, so as to avoid crossover pressure effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

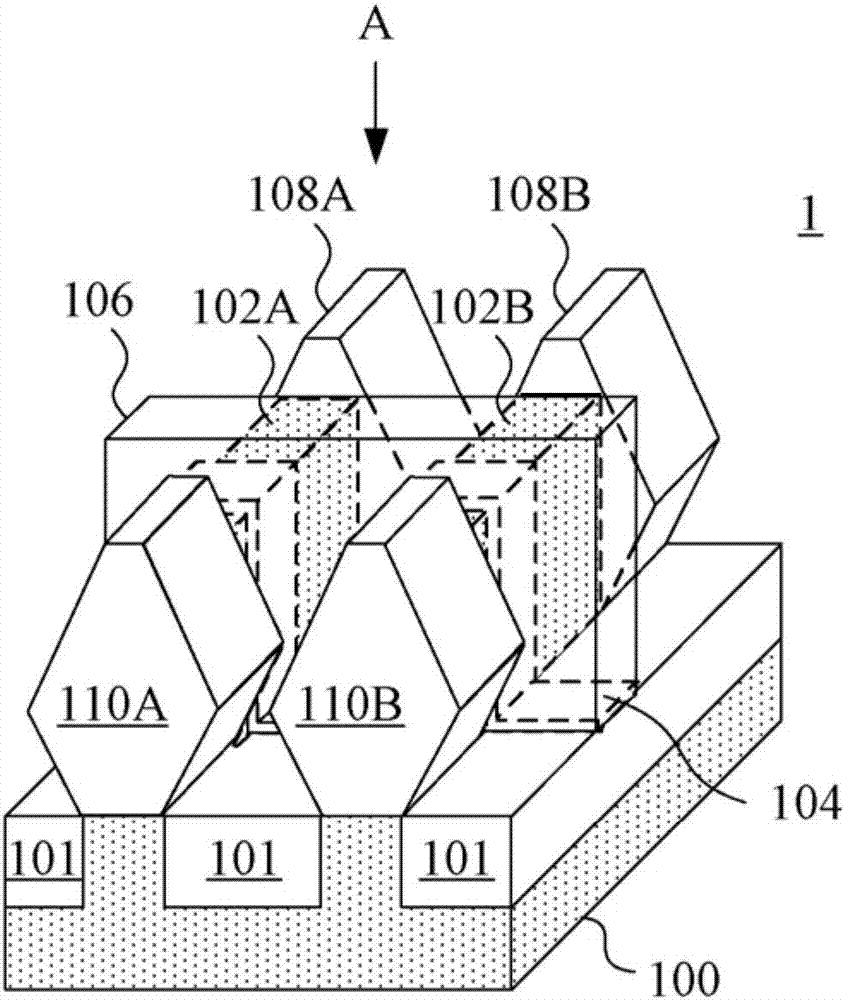

[0032] Please also refer to Figure 1A and Figure 1B . Figure 1A It is a three-dimensional view of a fin field effect transistor 1 in an embodiment of the present invention. Figure 1B In one embodiment of the present invention, Figure 1A The top view of the fin field effect transistor 1 along the direction A.

[0033] The FinFET 1 includes: a semiconductor substrate 100 , fin structures 102A, 102B, a gate dielectric layer 104 , a gate electrode structure 106 , drain structures 108A, 108B, and source structures 110A, 110B. It should be noted that, since the gate dielectric layer 104 is covered by the gate electrode structure 106, the Figure 1A and Figure 1B , the gate dielectric layer 104 is shown by a dotted line.

[0034] In one embodiment, the semiconductor substrate 100 is, for example, but not limited to a silicon substrate. The semiconductor substrate 100 includes a plurality of insulating regions 101 . The isolation region 101 includes structures such as, but n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com