Wafer-level chip packaging structure and preparation method thereof

A wafer-level chip and packaging structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems affecting the performance of packaged chips, low-k dielectric layer cracks, etc., to prevent damage and ensure performance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

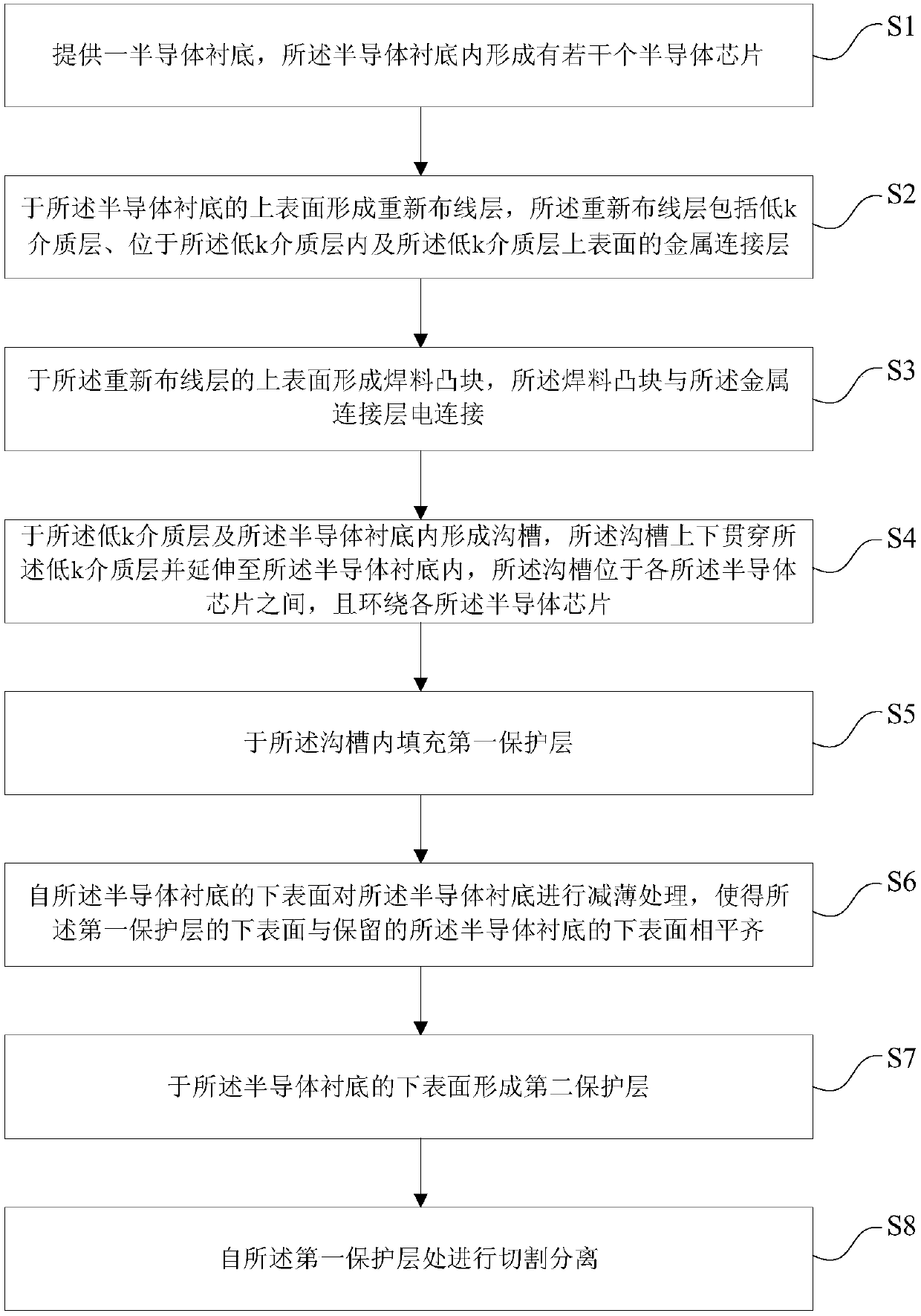

[0061] see figure 1 , the present invention provides a method for preparing a wafer-level chip packaging structure, the method for preparing the wafer-level chip packaging structure includes the following steps:

[0062] 1) providing a semiconductor substrate, in which several semiconductor chips are formed;

[0063] 2) forming a rewiring layer on the upper surface of the semiconductor substrate, the rewiring layer including a low-k dielectric layer, a metal connection layer located in the low-k dielectric layer and on the upper surface of the low-k dielectric layer;

[0064] 3) forming solder bumps on the upper surface of the rewiring layer, the solder bumps are electrically connected to the metal connection layer;

[0065] 4) forming trenches in the low-k dielectric layer and the semiconductor substrate, the trenches penetrate the low-k dielectric layer up and down and extend into the semiconductor substrate, and the trenches are located in each of the between and surroundin...

Embodiment 2

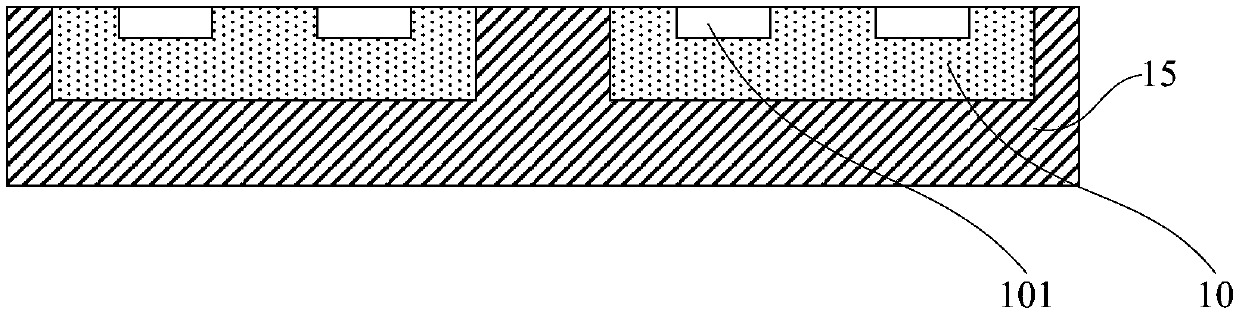

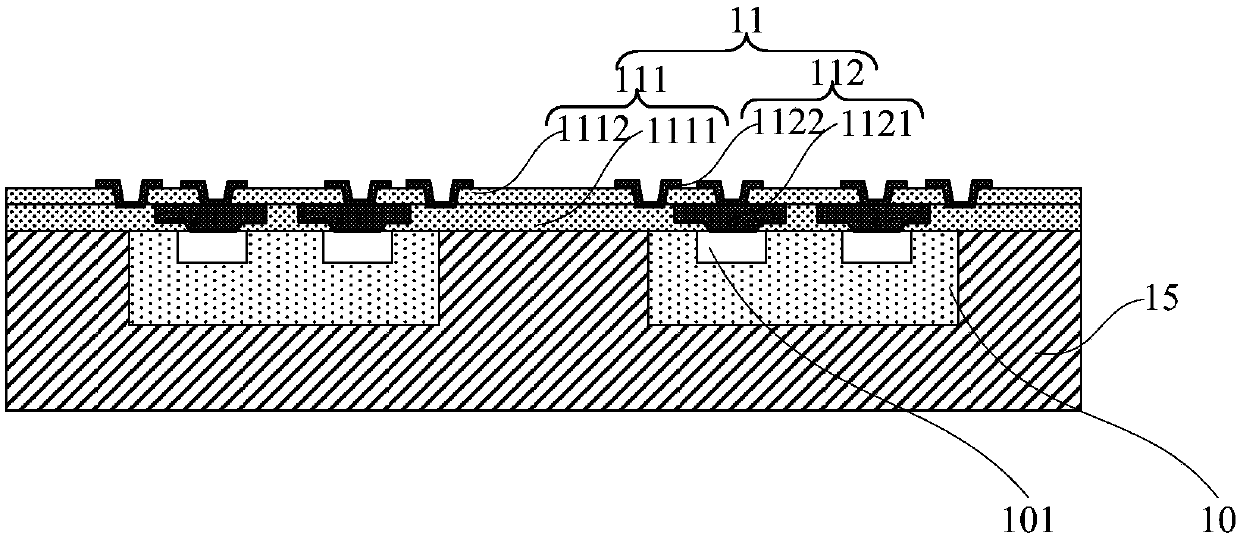

[0113] Please combine Figure 2 to Figure 10 read on Figure 11 , this embodiment also provides a wafer-level chip packaging structure, the wafer-level chip packaging structure includes: a semiconductor chip 10; a rewiring layer 11, the rewiring layer 11 includes a low-k dielectric layer 111, located The metal connection layer 112 in the low-k dielectric layer 111 and on the upper surface of the low-k dielectric layer 111; the low-k dielectric layer 111 is located on the front side of the semiconductor chip 10, and the metal connection layer 112 is connected to the semiconductor chip 10 electrical connection; solder bump 12, the solder bump 12 is located on the upper surface of the rewiring layer 11, and is electrically connected to the metal connection layer 112; the first protective layer 13, the first protective layer 13 Located on the periphery of the semiconductor chip and the rewiring layer 11 of the 10, and plastic-encapsulate the side of the semiconductor chip 10 and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More