Chip scale package diode component with ultra-low forward voltage and manufacture method

A technology of diode components and packaged diodes, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, and electric solid-state devices, etc., which can solve the problems of high forward voltage, high cost, and long manufacturing process, etc. The effect of stabilizing resistance and electrical characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0077] For ease of description, the following embodiments are all based on N-type substrates or silicon wafers. The present invention provides a method for manufacturing a grain-sized packaged diode element with ultra-low forward voltage. The first embodiment includes the following step:

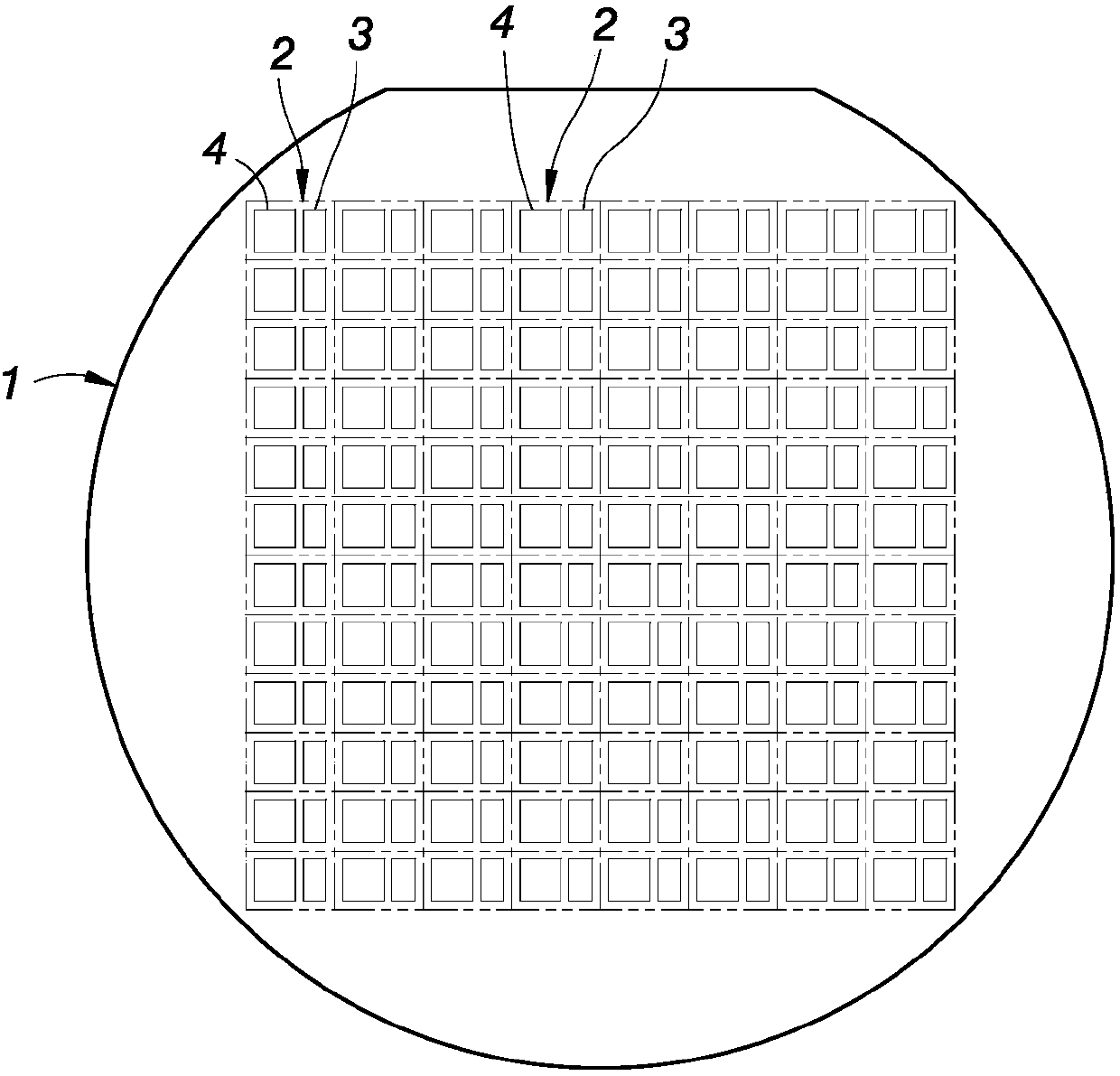

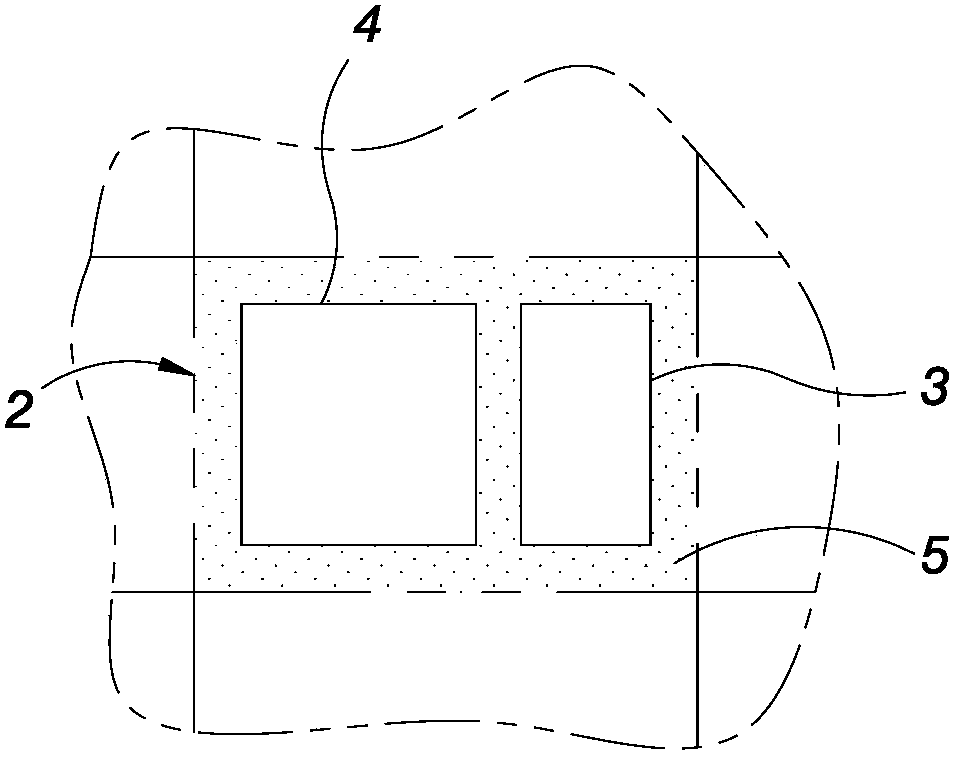

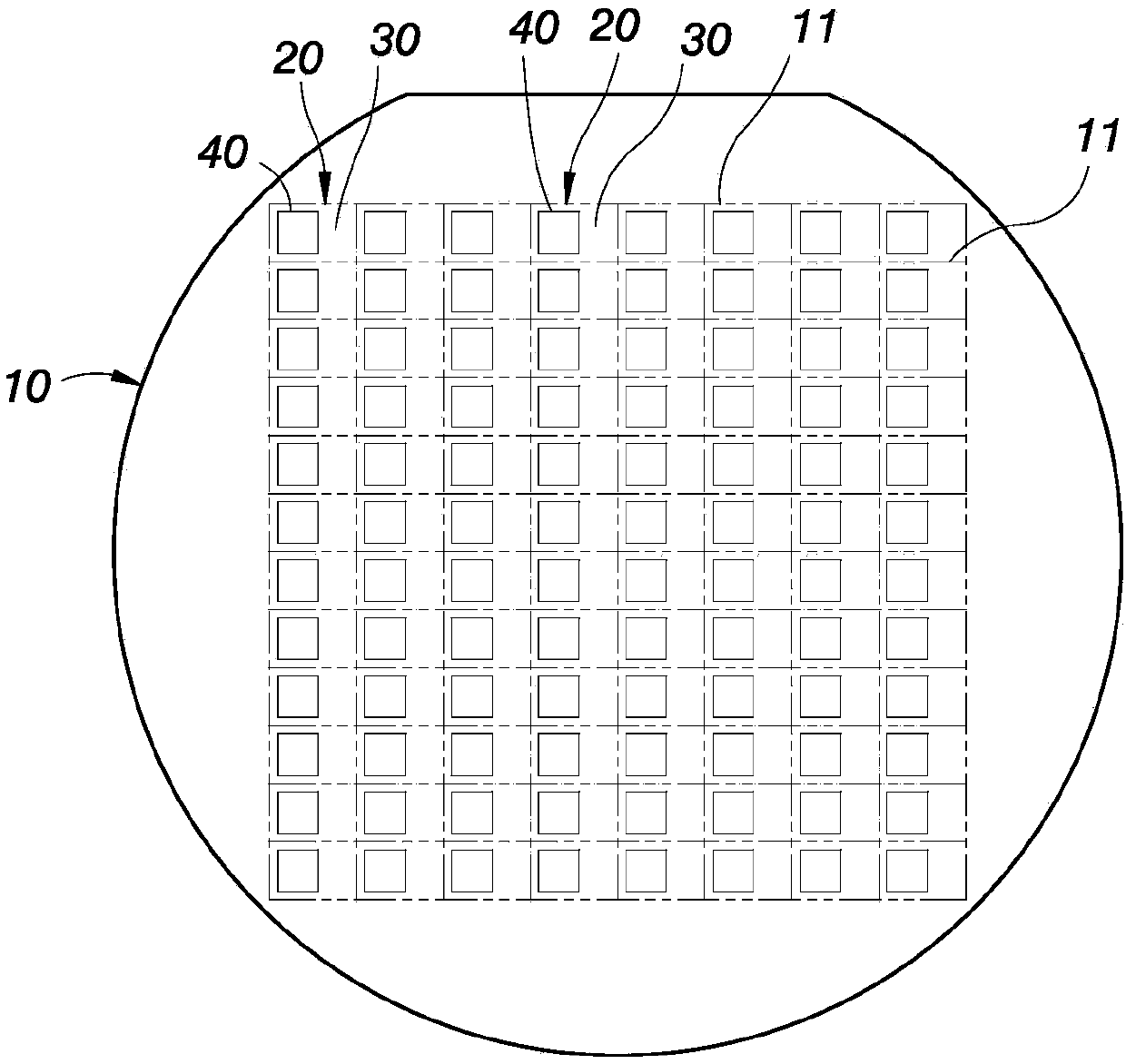

[0078] The first step: if image 3 As shown, on the front side of a substrate 10, it is divided into a plurality of diode element regions 20 according to the required size of the diode element, and a cutting line 11 is reserved on the periphery of each diode element region 20, and in each diode element region 20 The first electrode region 30 and the second electrode region 40 are arranged in the inner periphery of the diode element region 20 ; all the positions of the diode element region 20 other than the second electrode region 40 are used as the first electrode region 30 .

[0079] The second step: if Figure 4 As shown, on the position where the second electrode region 40 of each diode...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More