Patents

Literature

44results about How to "Does not affect electrical characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

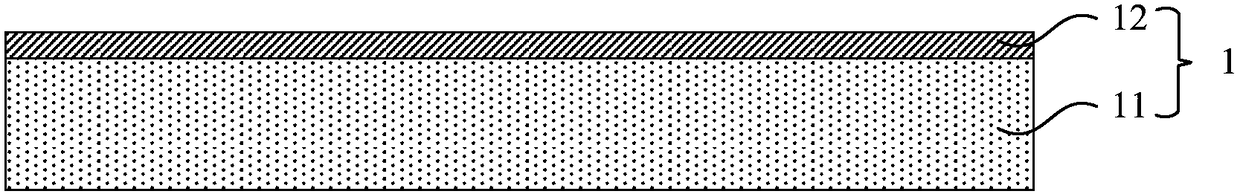

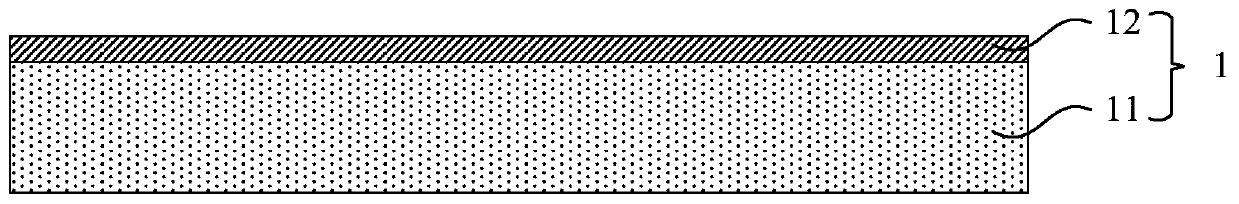

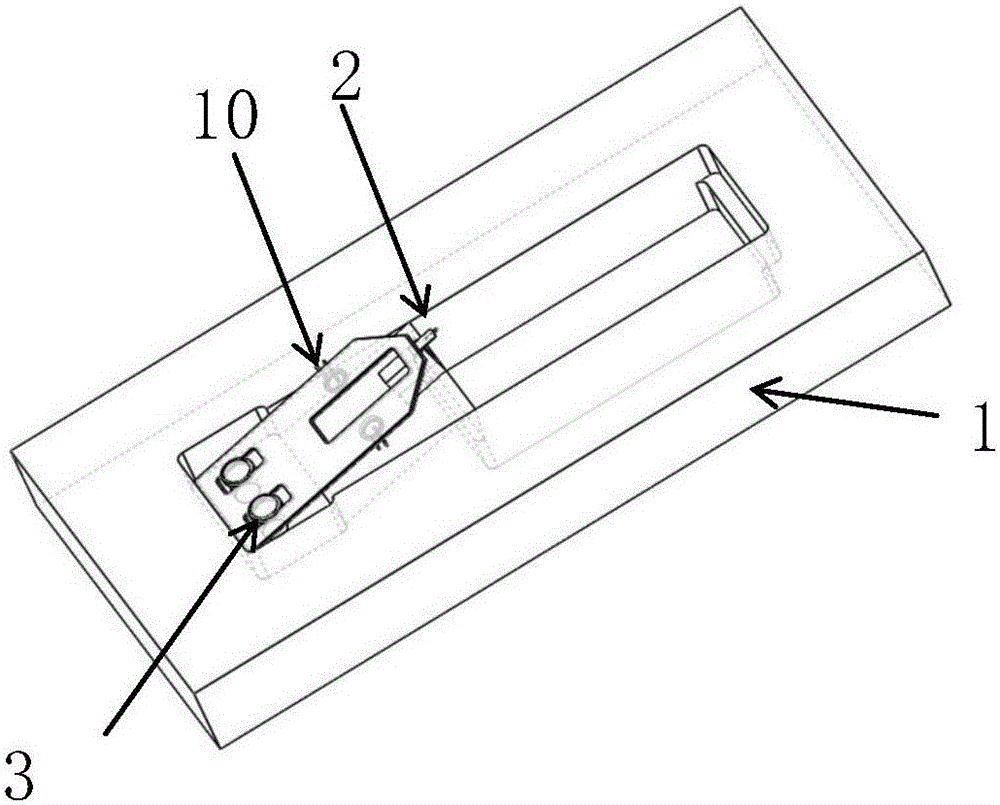

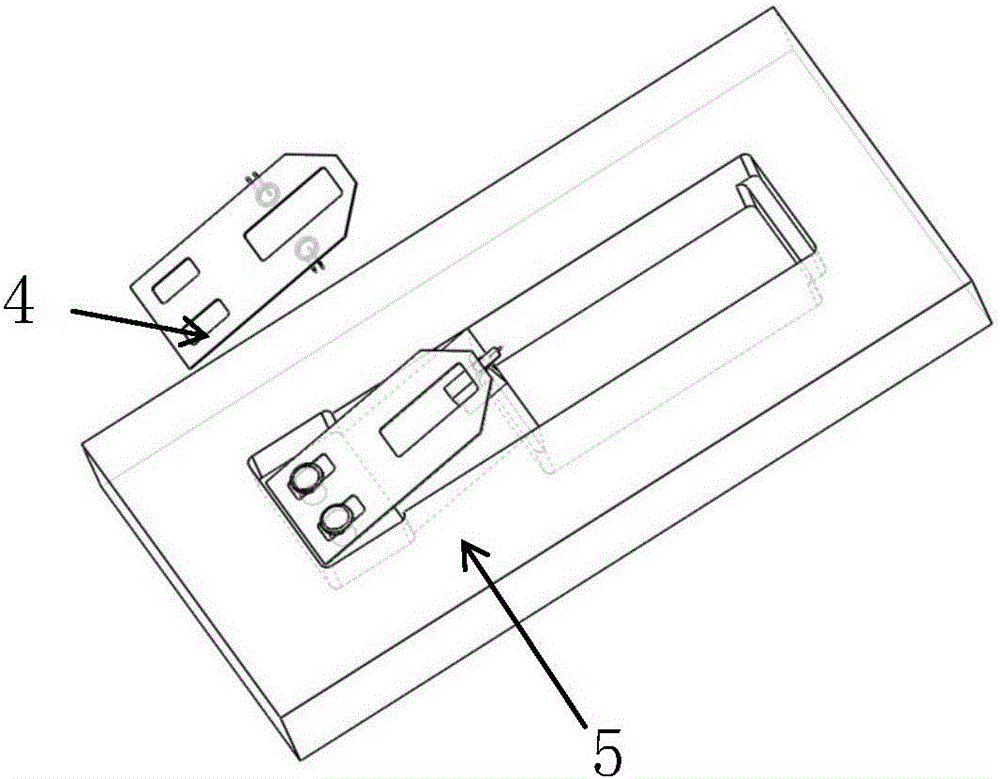

Method for manufacturing flexible display and substrate for manufacturing flexible display

ActiveCN102769109AEasy to manufactureQuality improvementFinal product manufactureSolid-state devicesDisplay deviceFlexible display

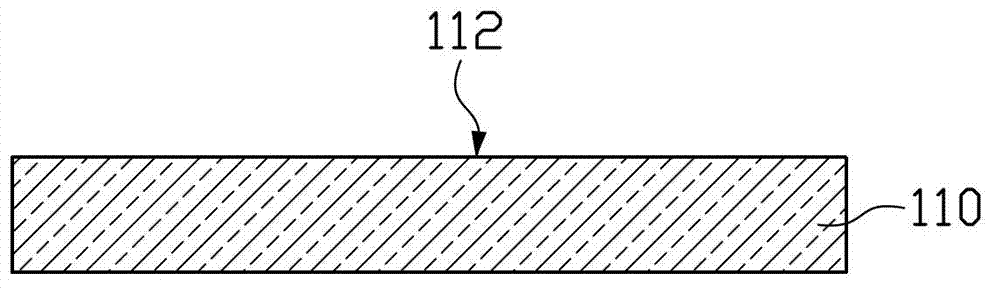

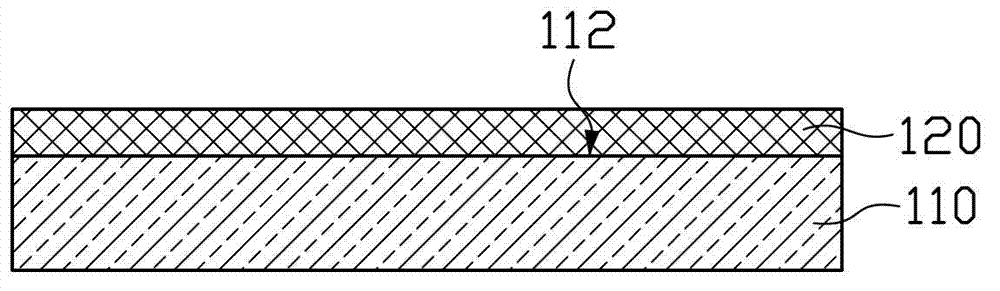

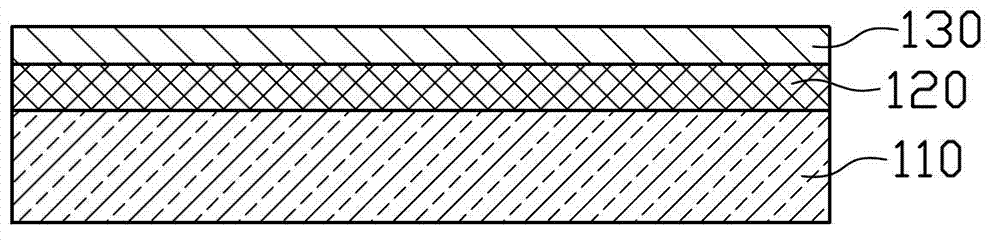

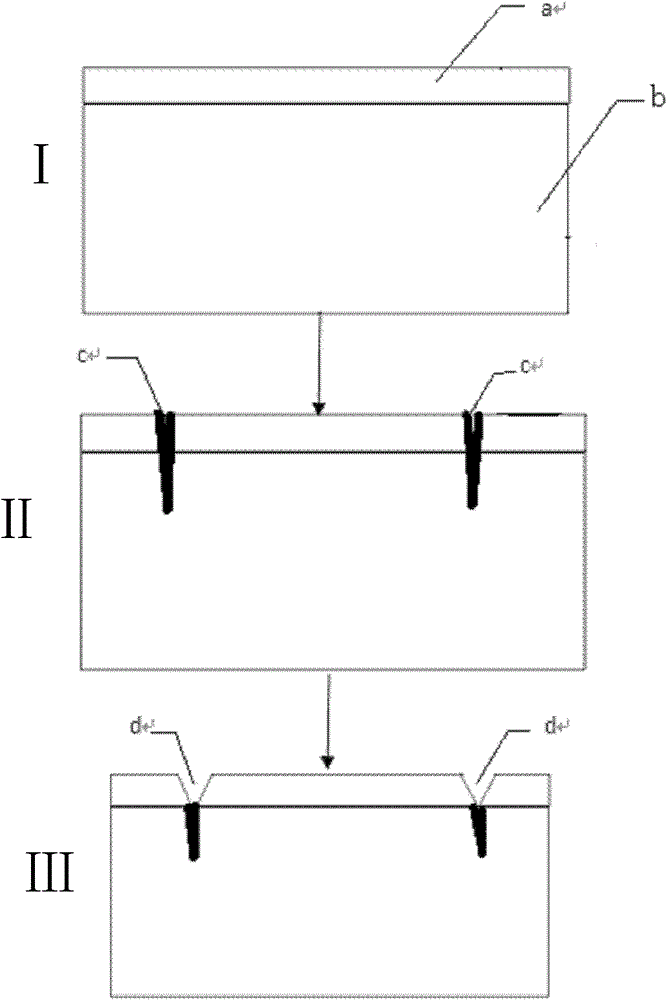

The invention discloses a method for manufacturing a flexible display. The method comprises the following steps of: forming a silicon sacrificial layer on a rigid substrate, and attaching a flexible substrate to the silicon sacrificial layer through an adhesive layer; manufacturing a display element layer on the flexible substrate; and etching the silicon sacrificial layer under normal temperature conditions by utilizing fluorine-containing corrosive gas so as to gasify the silicon sacrificial layer, so that the flexible substrate is separated from the rigid substrate. The method for manufacturing the flexible display is simple in process, the problems of unclean stripping and stripping damage can be effectively solved, and manufacture of a high-quality flexible display is facilitated. The invention also relates to a substrate for manufacturing the flexible display.

Owner:HISENSE VISUAL TECH CO LTD

Cutting method of LED chip

InactiveCN104347760AAvoid ablationDoes not affect electrical characteristicsSemiconductor/solid-state device manufacturingFine working devicesEngineeringLaser cutting

The invention discloses a cutting method of an LED chip. The method comprises drawing scratches by use of laser on the back surface of the chip and performing saw cutting by use of a diamond saw blade knife, wherein the saw blade knife is an isosceles inverted triangle with a symmetrical left portion and right portion, and the included angle between a knife side surface and a horizontal line is 30 DEG to 60 DEG. The method further comprises performing overturning and film reversing on the back-cut chip and cutting the front surface of the chip along grooves to form crystal grains by use of a splinter knife. According to the invention, the problems of backside collapse, burr and the like by use of a conventional saw blade process are solved, the problem of ablation brought by laser cutting is avoided, and the method is simple to operate and easy to realize.

Owner:LATTICE POWER (JIANGXI) CORP

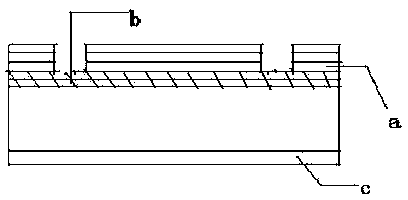

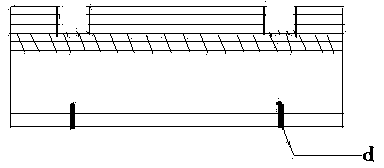

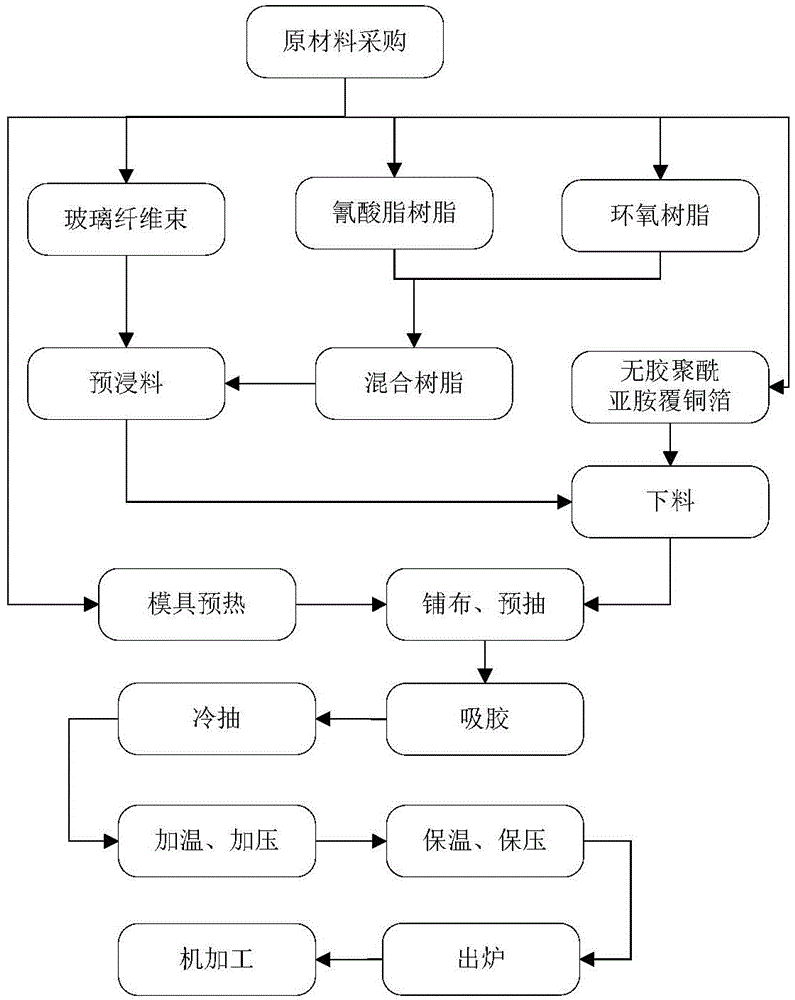

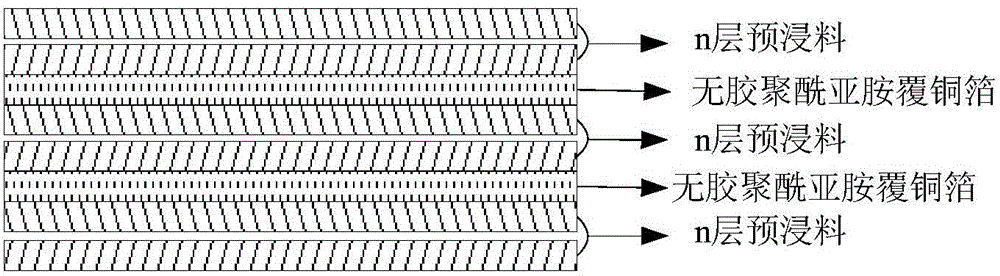

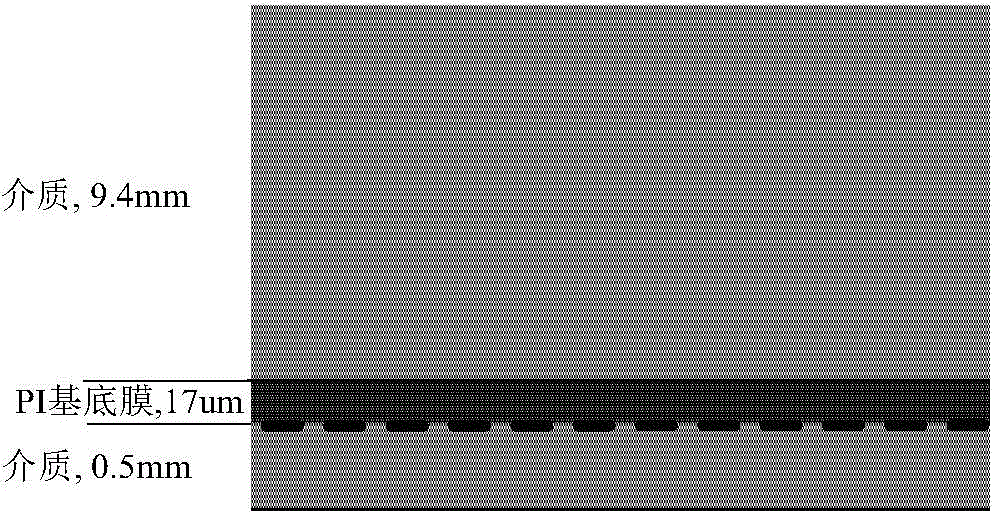

Preparation method of interlayer frequency selective surface composite material

ActiveCN104934721AMechanical strength is not affectedDoes not affect electrical characteristicsAntenna adaptation in movable bodiesRadiating element housingsEpoxyGlass fiber

The invention provides a preparation method of an interlayer frequency selective surface composite material, comprising 12 steps. The technical scheme comprises: manufacturing frequency selective surface films; and adding the thin films among prepreg layers of glass fibre cloth and epoxy resin to be laminated together. The method obtains conspicuous hiding effects under the condition of not changing the profile design of an original aircraft radome, and has no reverse impact on the electrical characteristics of an original radar system and the mechanical strength of a radome; a frequency selective surface bandpass radome is practical and feasible to solve the technical problem of invisibility of a radar antenna system.

Owner:EAGLES MEN AERONAUTIC SCI & TECH GRP

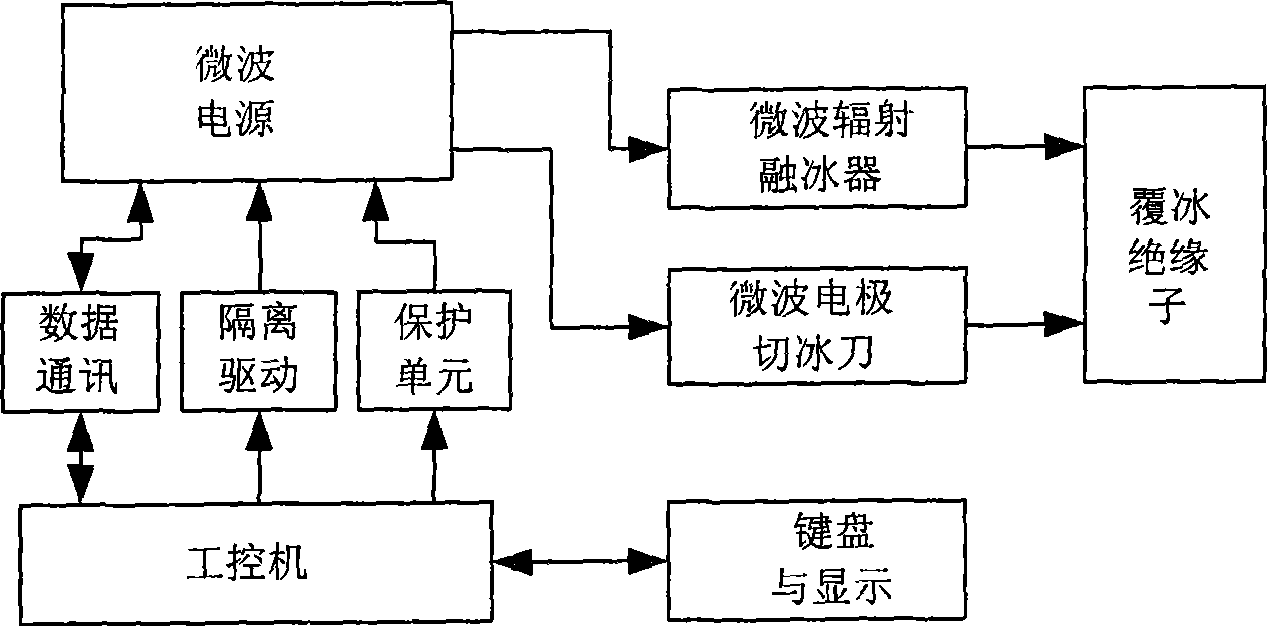

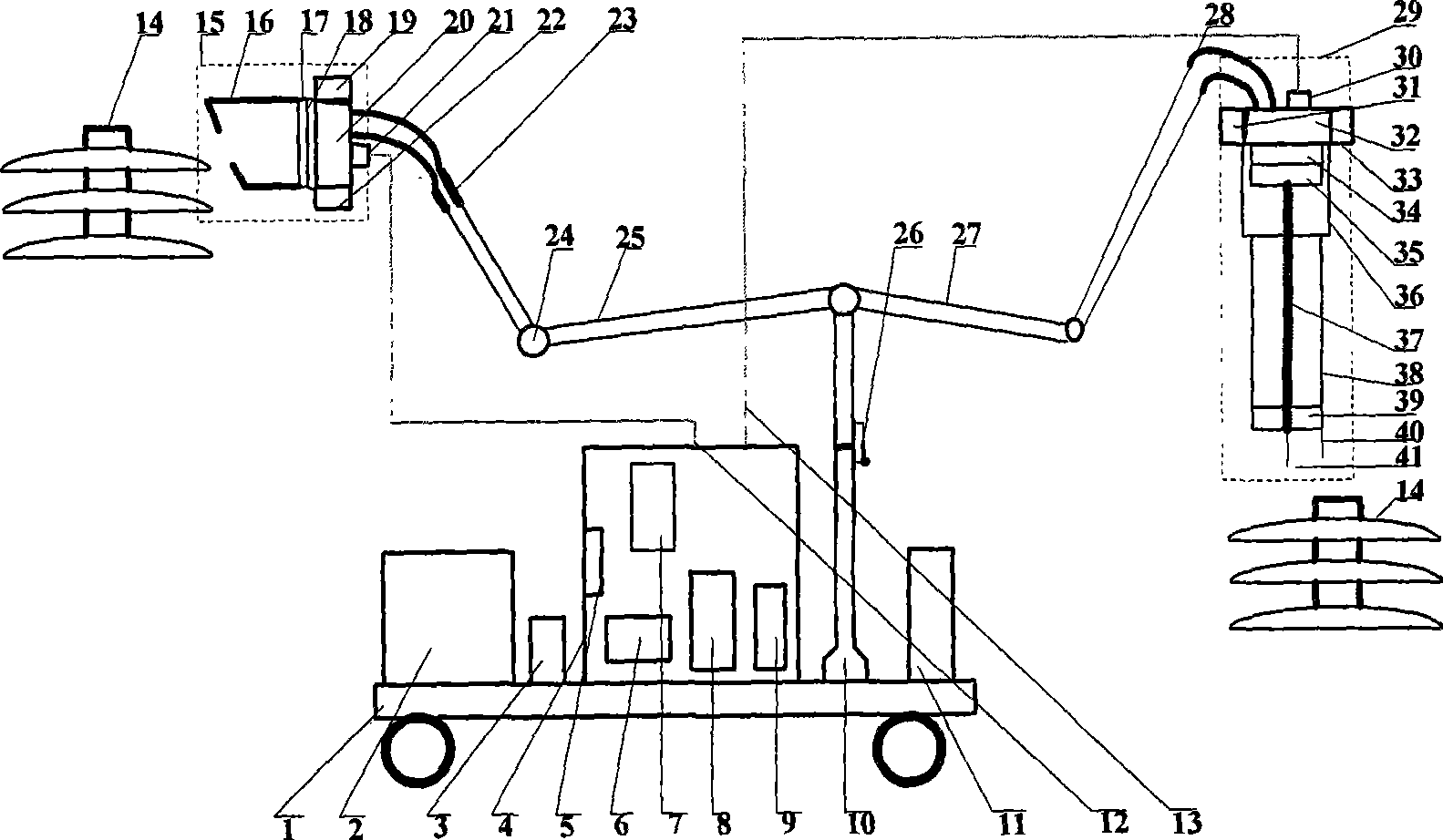

Microwave de-icing apparatus and de-icing method for electric power facilities

InactiveCN101478136AAchieve coolingStrong coagulationOverhead installationMagnetronsRadiationMicrowave

Owner:INST OF ELECTRICAL ENG CHINESE ACAD OF SCI +1

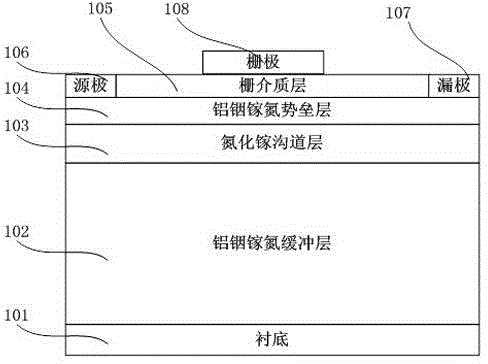

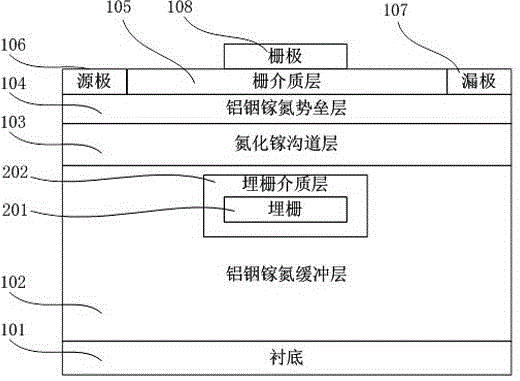

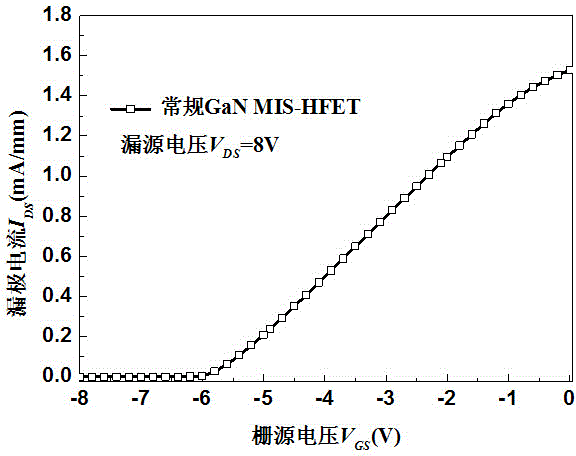

GaN-based enhancement/depletion mode heterojunction field effect transistor with buried gate structure

ActiveCN104167445AAdjustable Threshold VoltageAchieve normal workSemiconductor devicesGate dielectricOhmic contact

The invention discloses a GaN-based enhancement / depletion mode heterojunction field effect transistor with a buried gate structure. The GaN-based enhancement / depletion mode heterojunction field effect transistor is mainly composed of a substrate, an AlInGaN buffer layer, a buried gate, a buried gate dielectric layer, a GaN channel layer, an AlInGaN barrier layer, a gate dielectric layer, a source electrode, a drain electrode and a gate electrode from bottom to top, wherein the source electrode and the drain electrode are arranged on the AlInGaN barrier layer, and the gate electrode is arranged on the gate dielectric layer. The source electrode and the drain electrode are in ohmic contact with the AlInGaN barrier layer, and the source electrode and the gate dielectric layer are in Schottky contact. The buried gate dielectric layer and the buried gate are both placed in the AlInGaN buffer layer, and the buried gate is placed in the buried dielectric layer. Through independent bias arrangement of the buried gate, according to the different bias arrangement of the buried gate, the threshold voltage of devices is adjusted; when the buried gate is in a negative bias state, two-dimensional electron gas in the AlInGaN barrier layer is exhausted by the buried gate, and the devices are made to achieve enhancement mode work; when the buried gate is in a zero bias state or a positive bias state, the two-dimensional electron gas exists in the AlInGaN barrier layer, and the devices are made to achieve depletion mode work.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

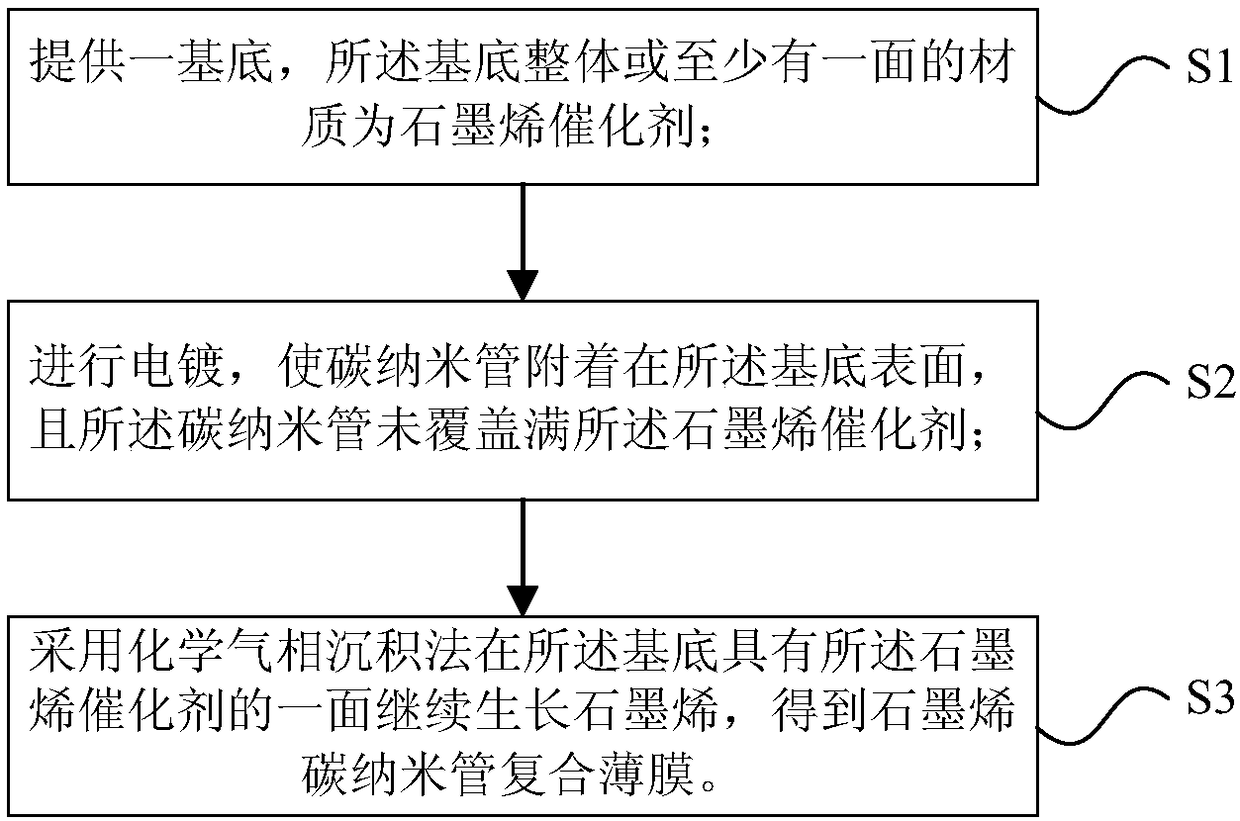

Graphene carbon nano tube composite film and preparation method and application thereof

ActiveCN108070891AGood thermal conductivityGood heat transfer performanceElectrolytic inorganic material coatingSemiconductor/solid-state device detailsCvd grapheneCarbon nanotube

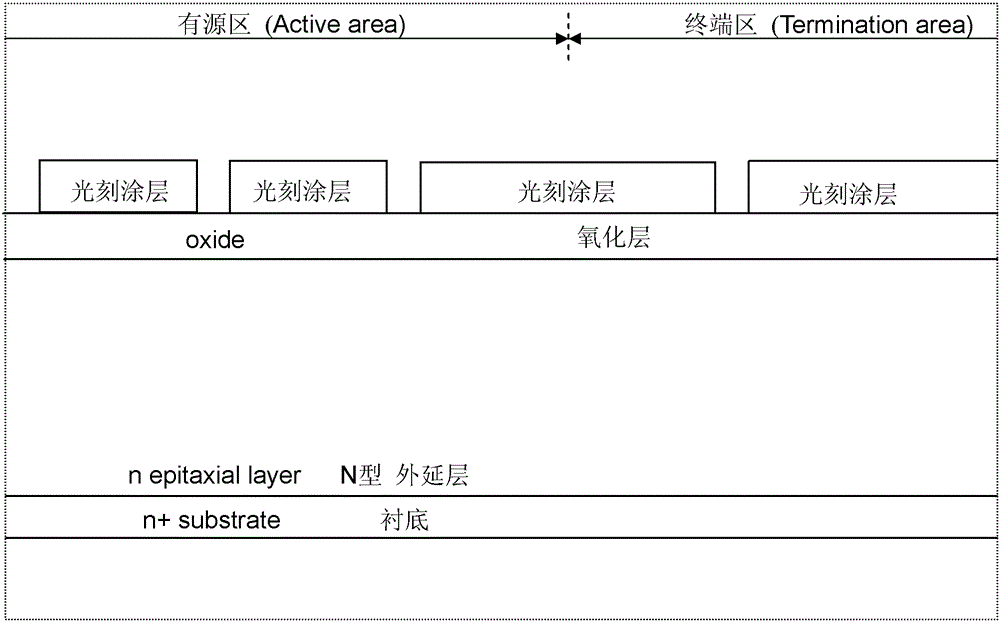

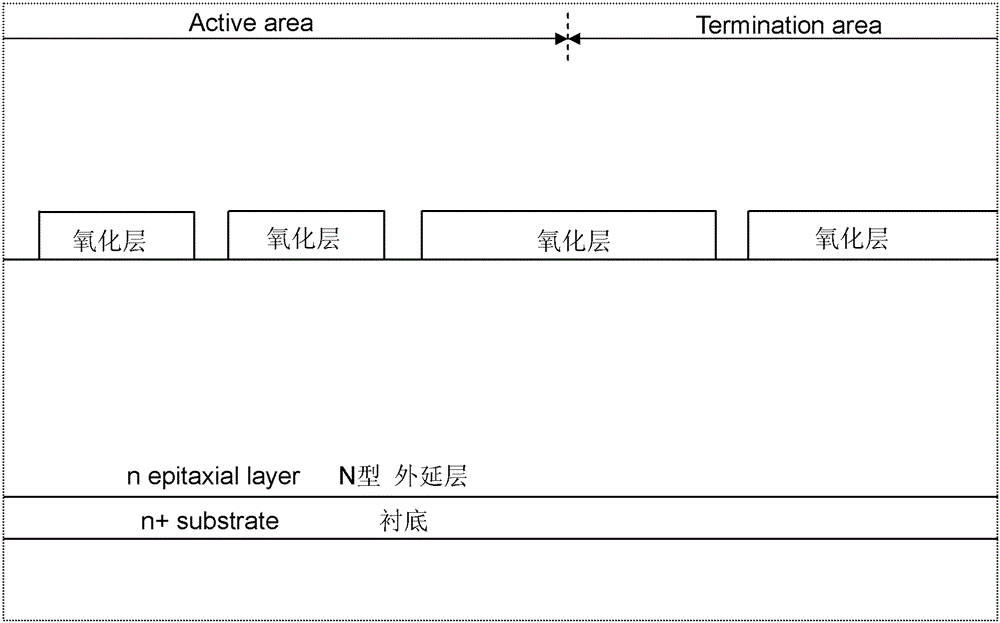

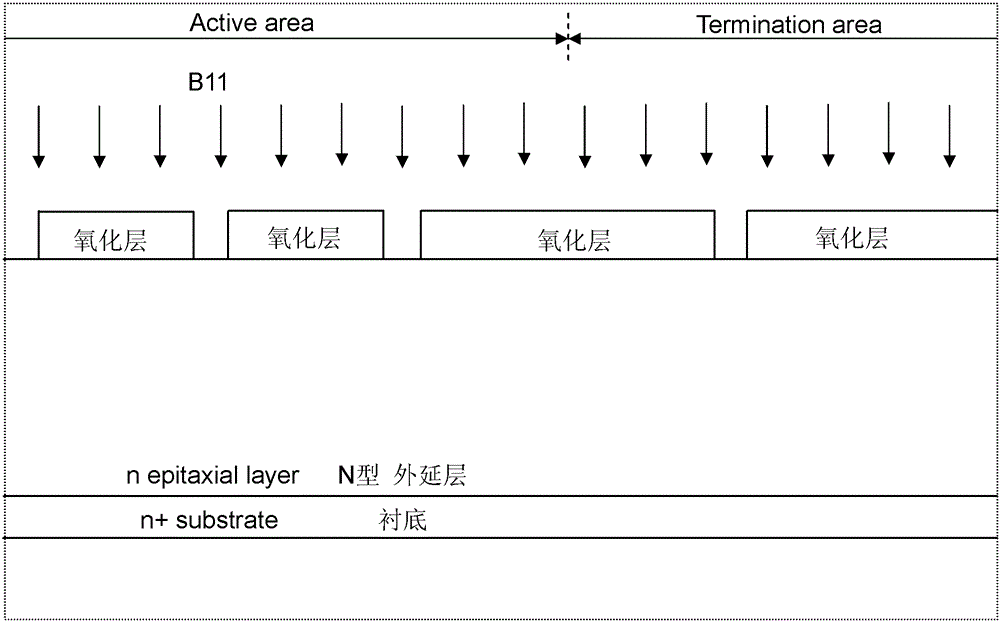

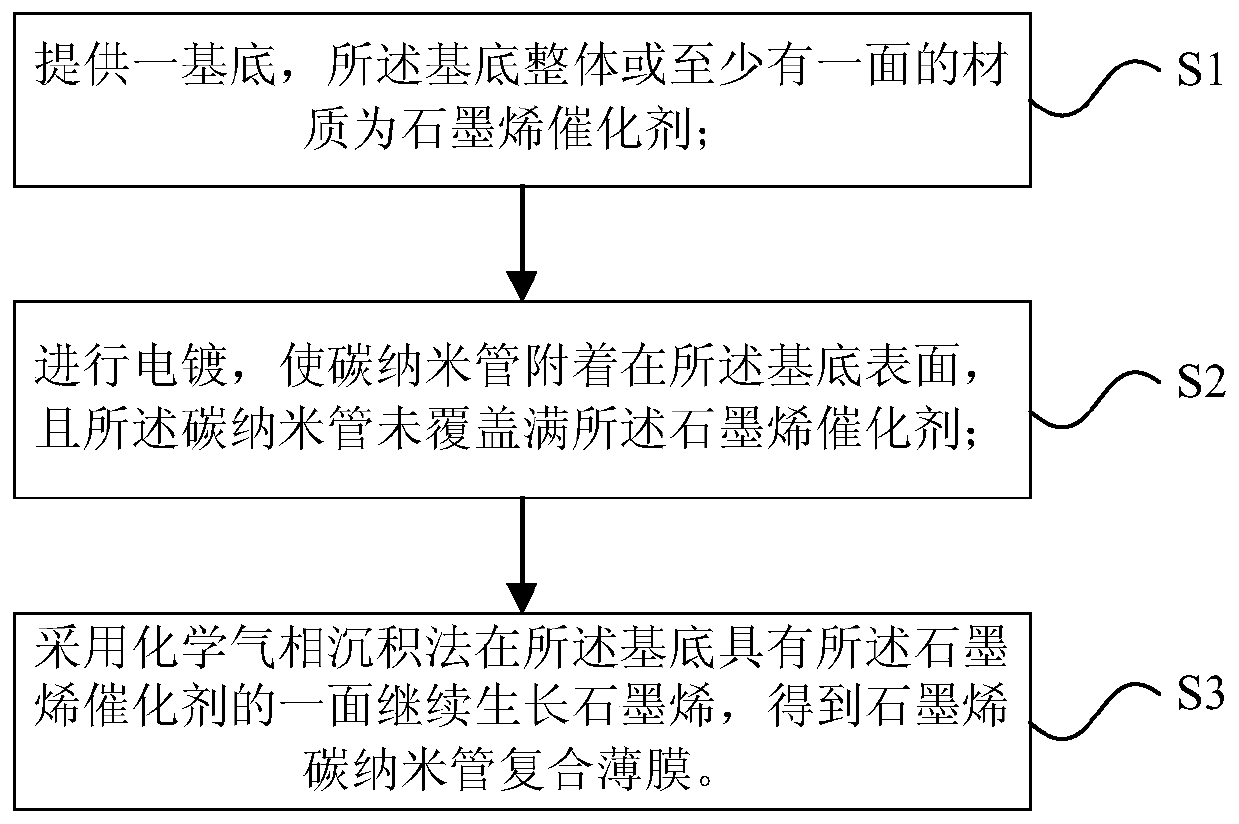

The invention provides a graphene carbon nano tube composite film and a preparation method and application thereof. The preparation method comprises the following steps that S1, a substrate is provided, and the whole or at least one face of the substrate is made of a graphene catalyst; S2, electroplating is conducted, thus, a carbon nano tube is attached to the surface of the substrate, and the graphene catalyst is not fully covered with the carbon nano tube; and S3, graphene continues to grow on the face, containing the graphene catalyst, of the substrate through a chemical gas phase method,and the graphene carbon nano tube composite film is obtained. The graphene carbon nano tube composite film and the preparation method and application thereof have the characteristic of being simple intechnology, the graphene carbon nano tube composite film obtained through the non-transferring self growing technology is good in quality, and contact and attaching between the composite film and thecatalyzing substrate are good.

Owner:SHANGHAI UNIV +1

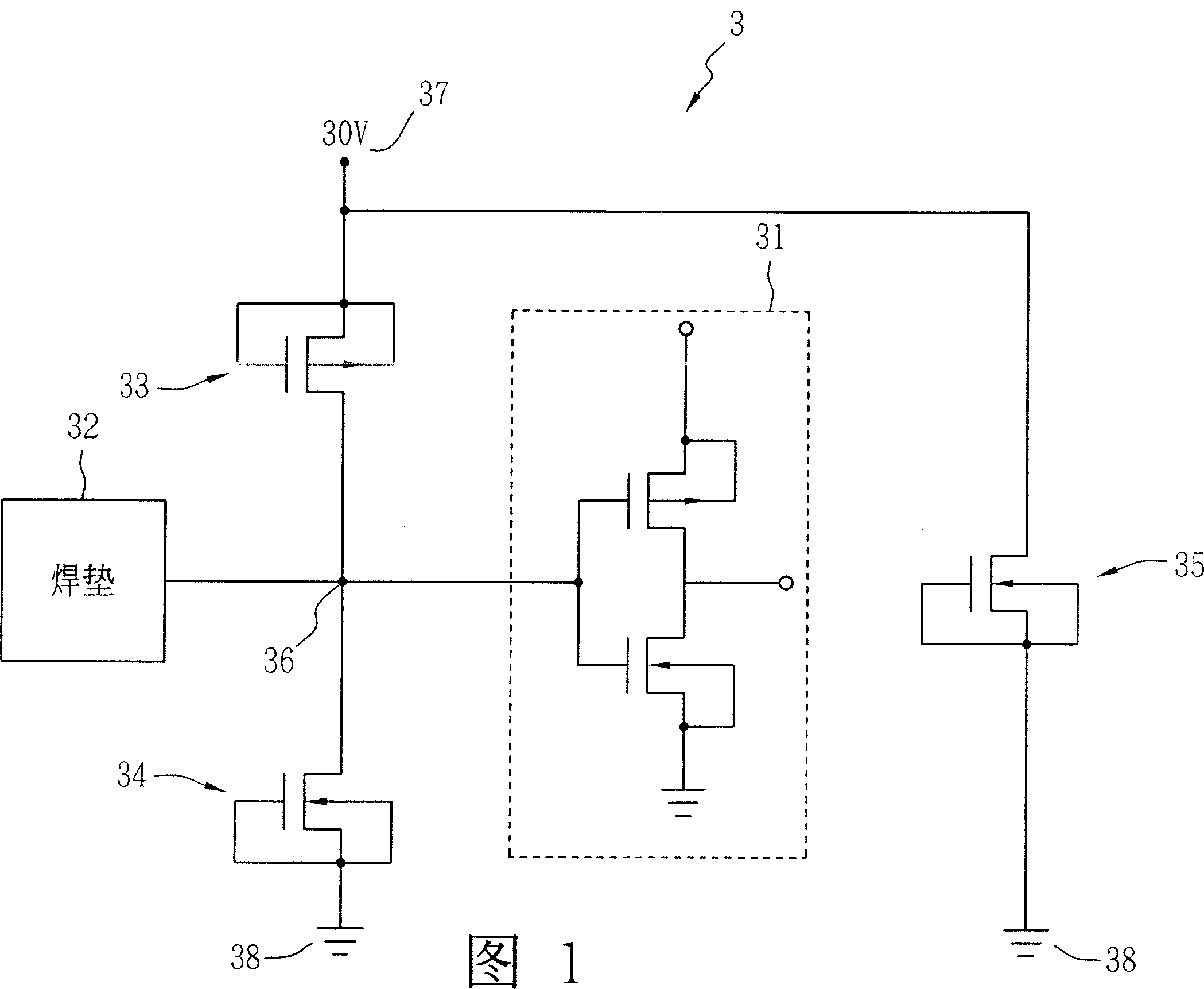

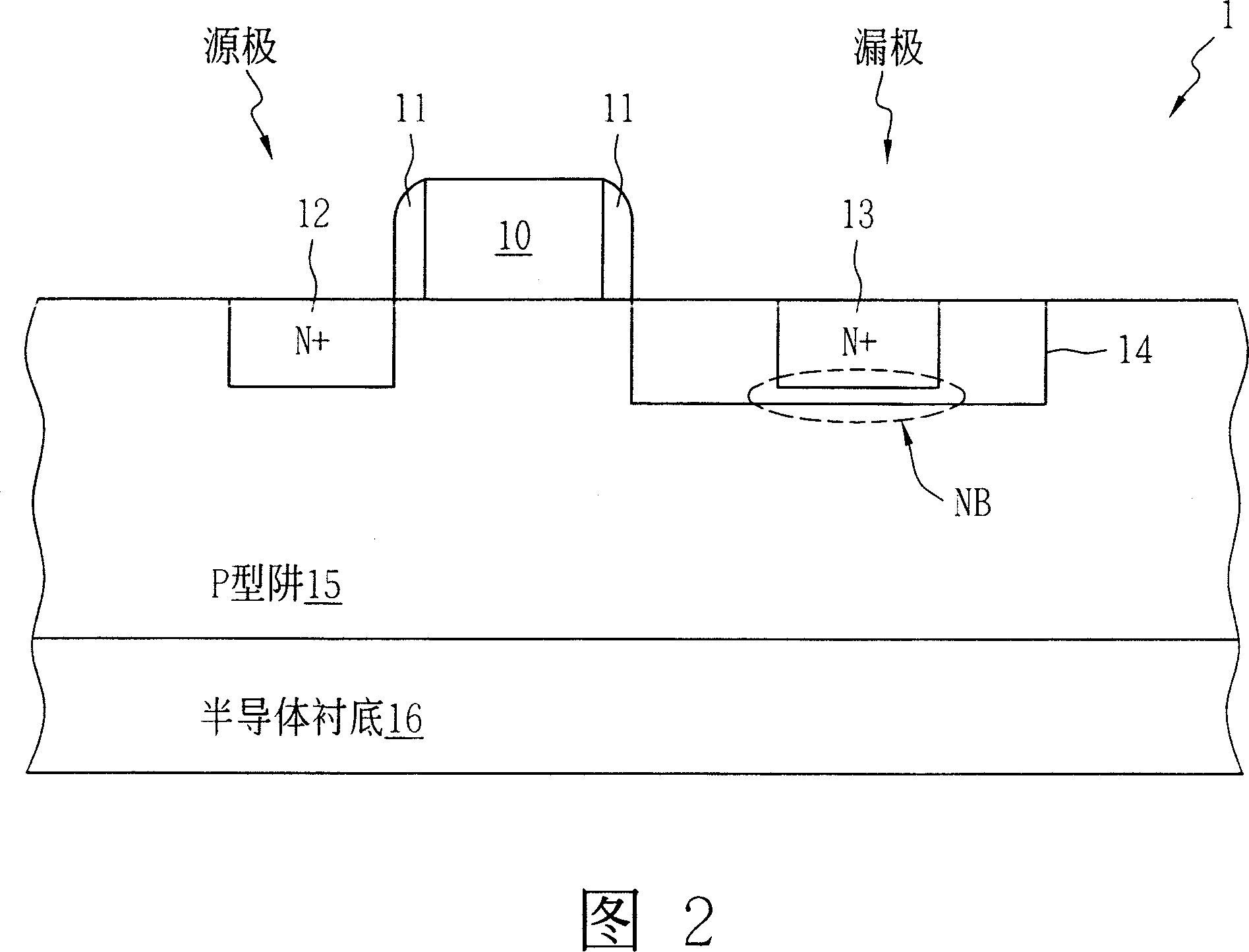

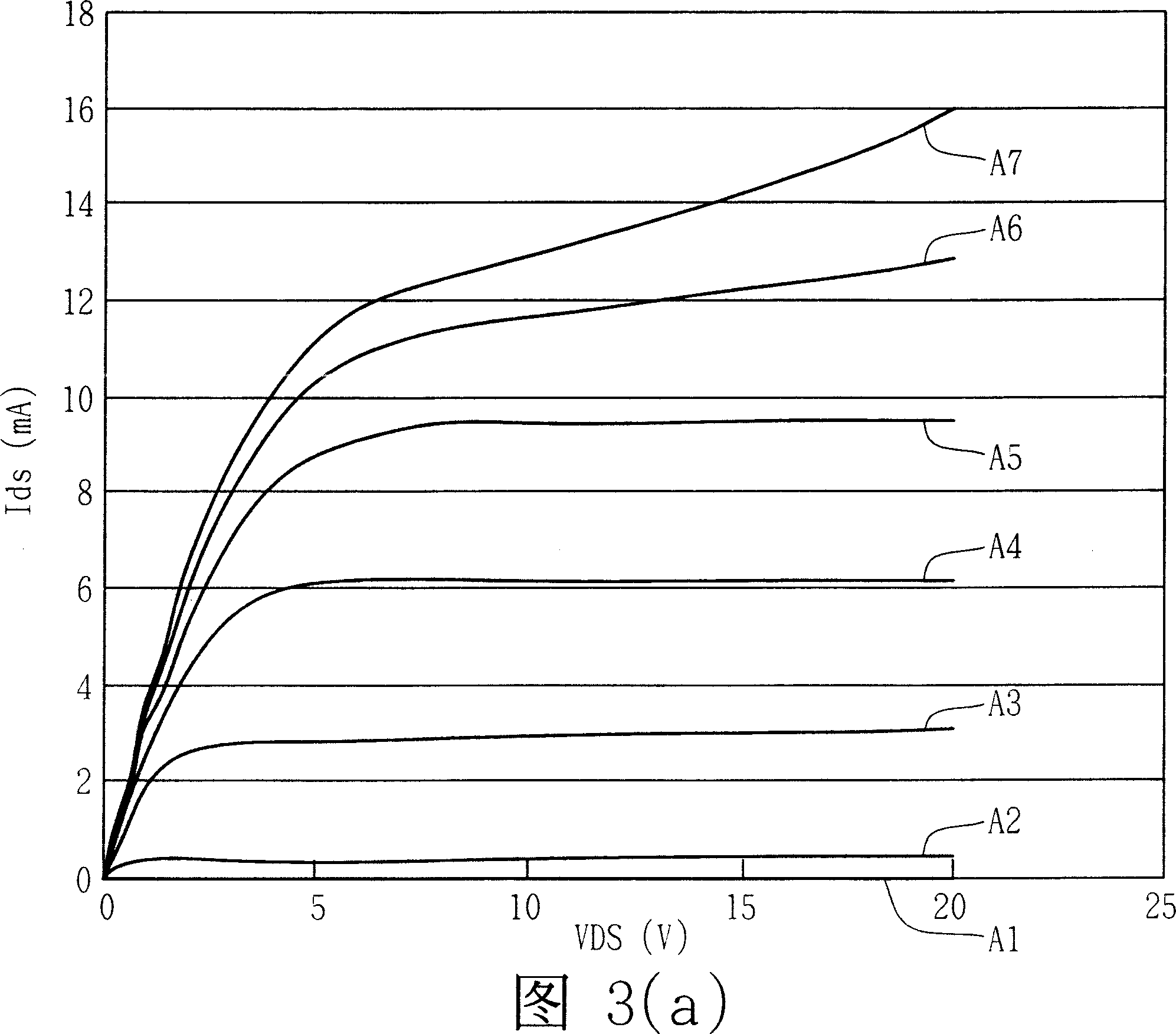

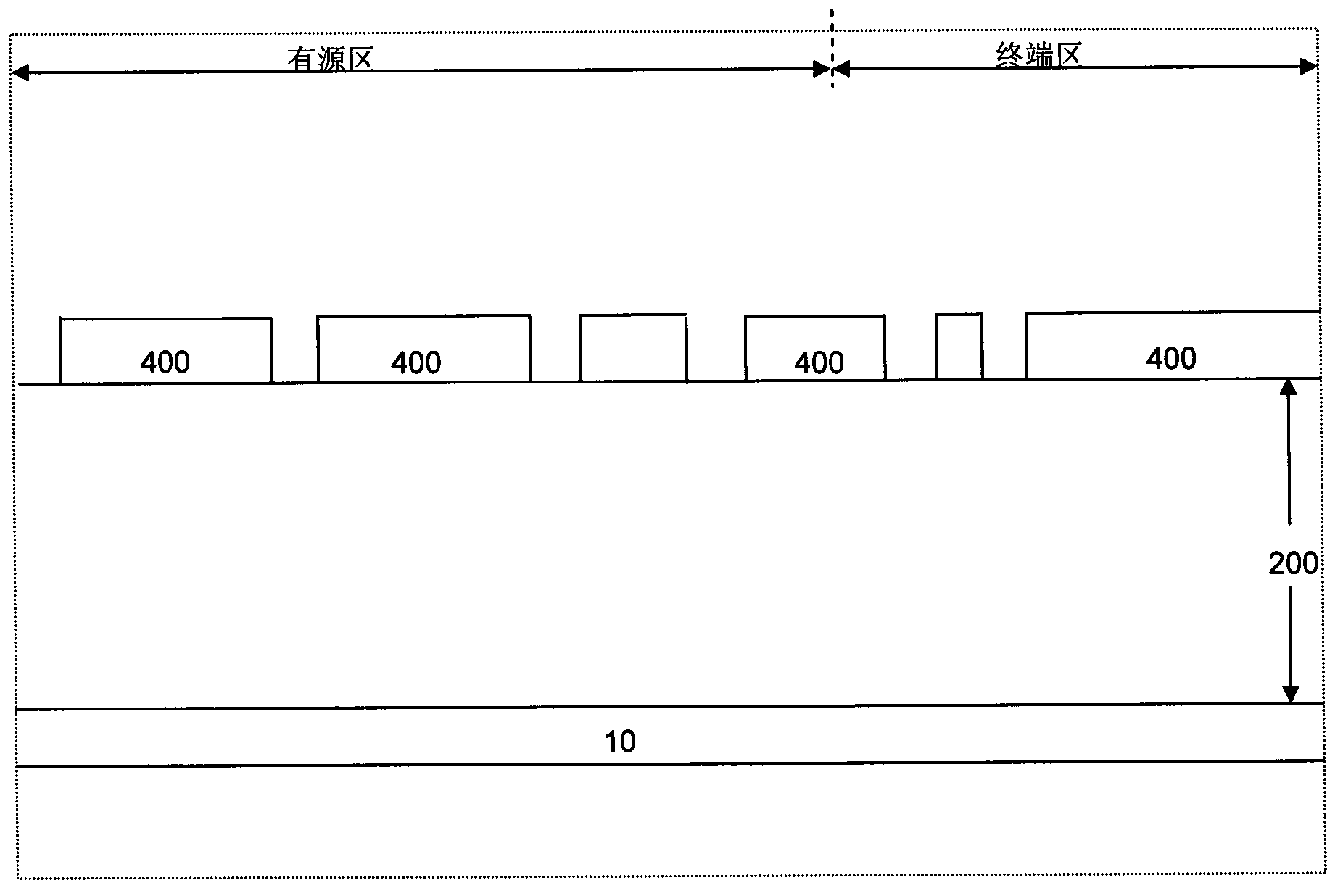

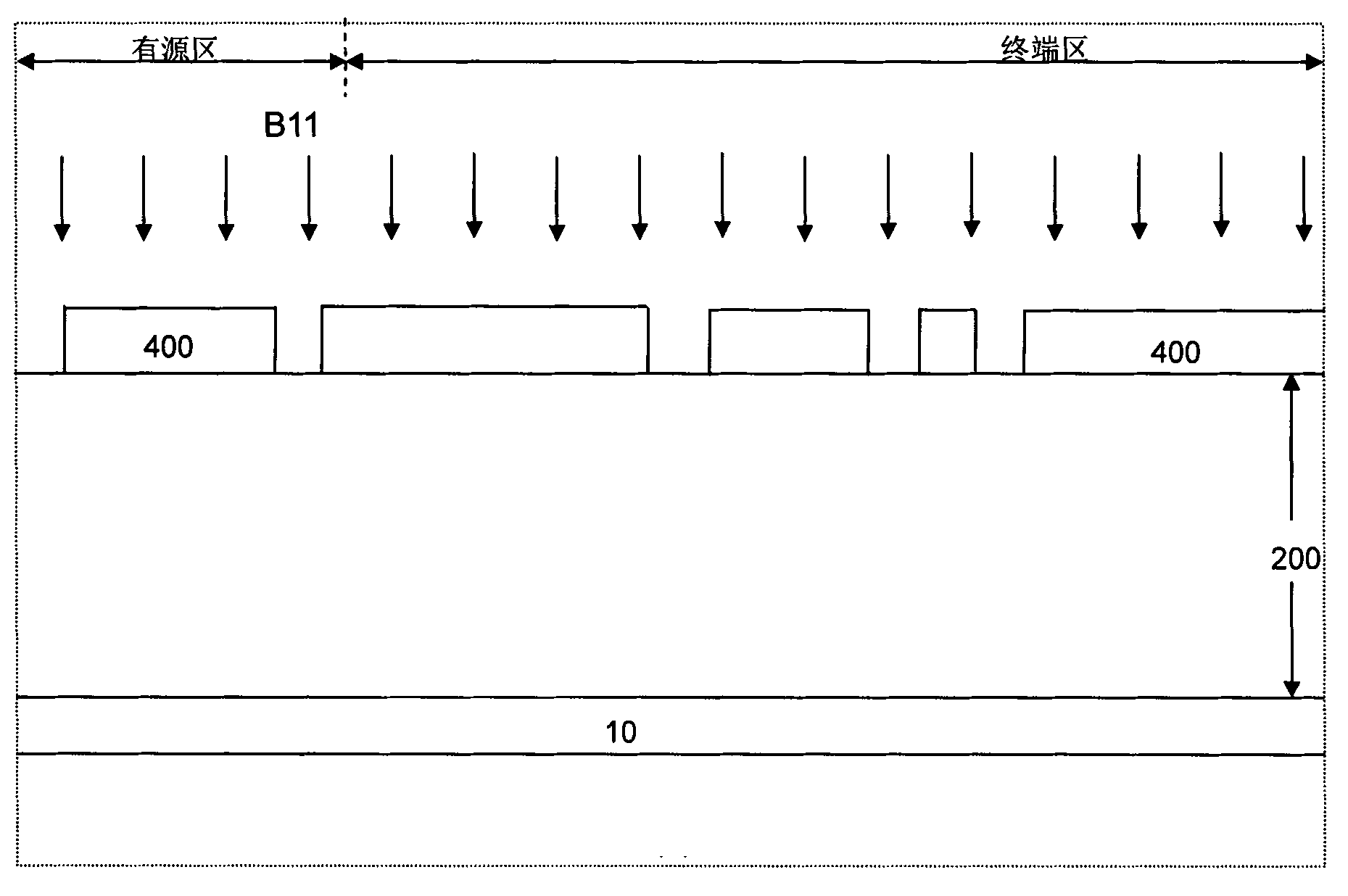

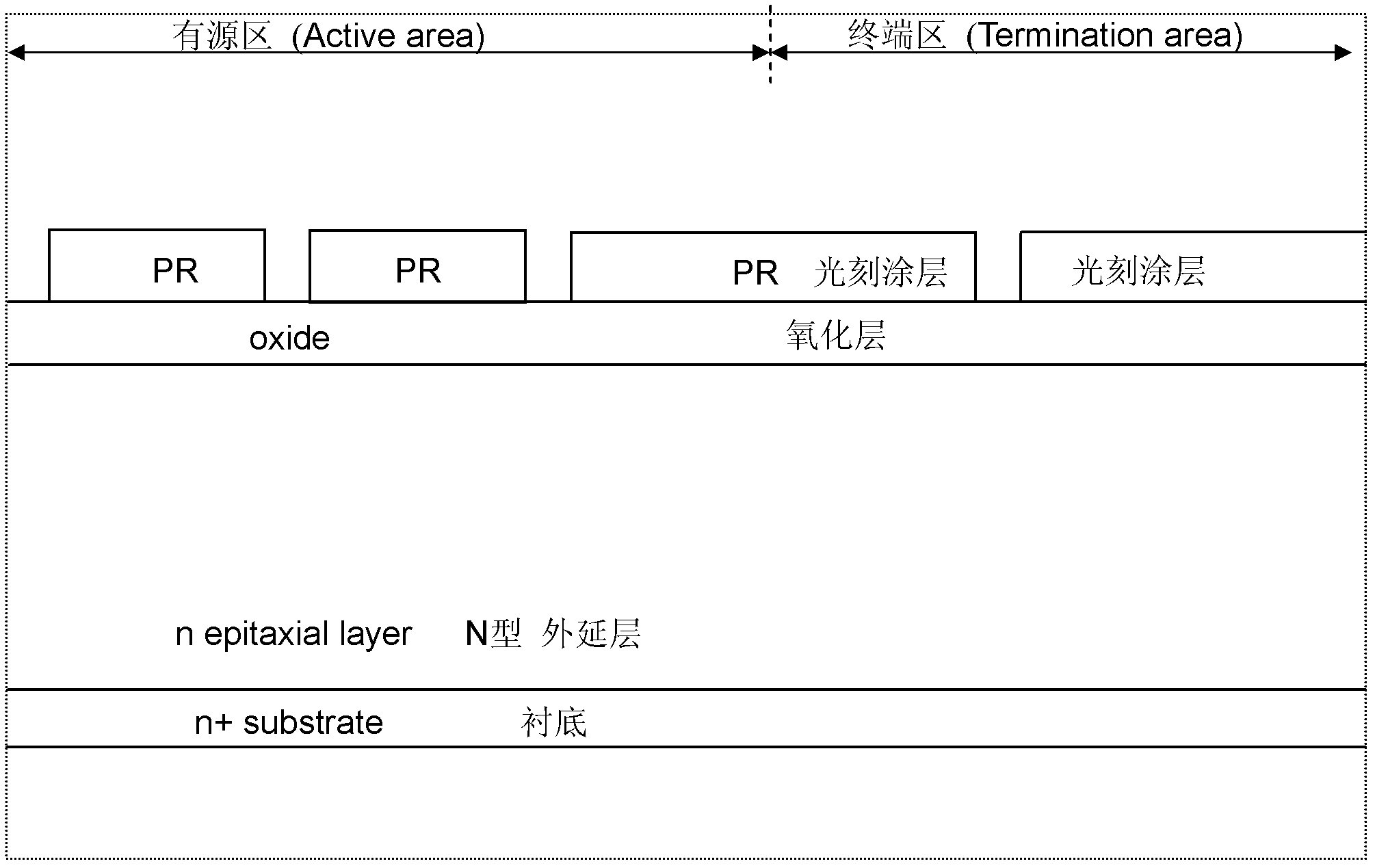

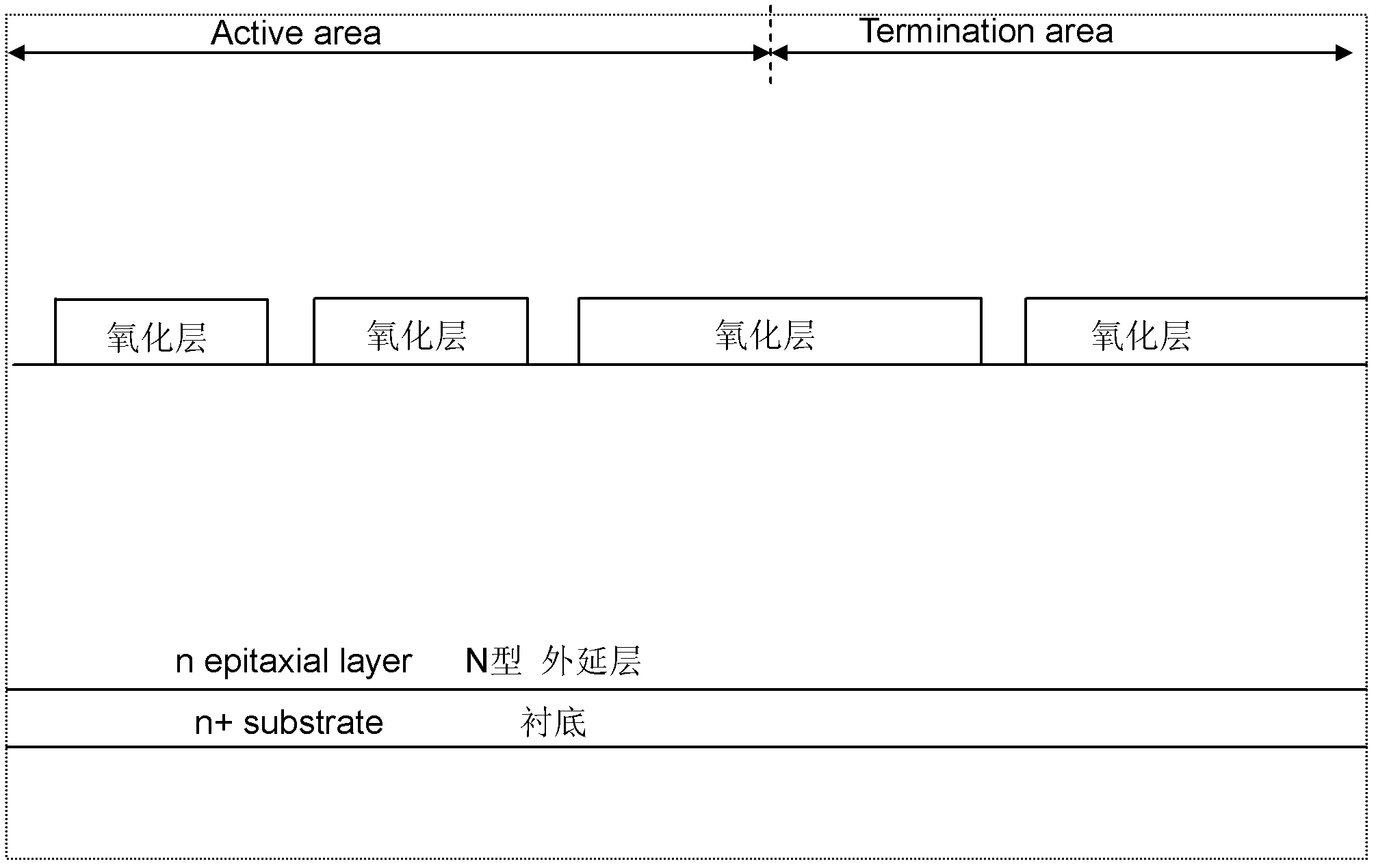

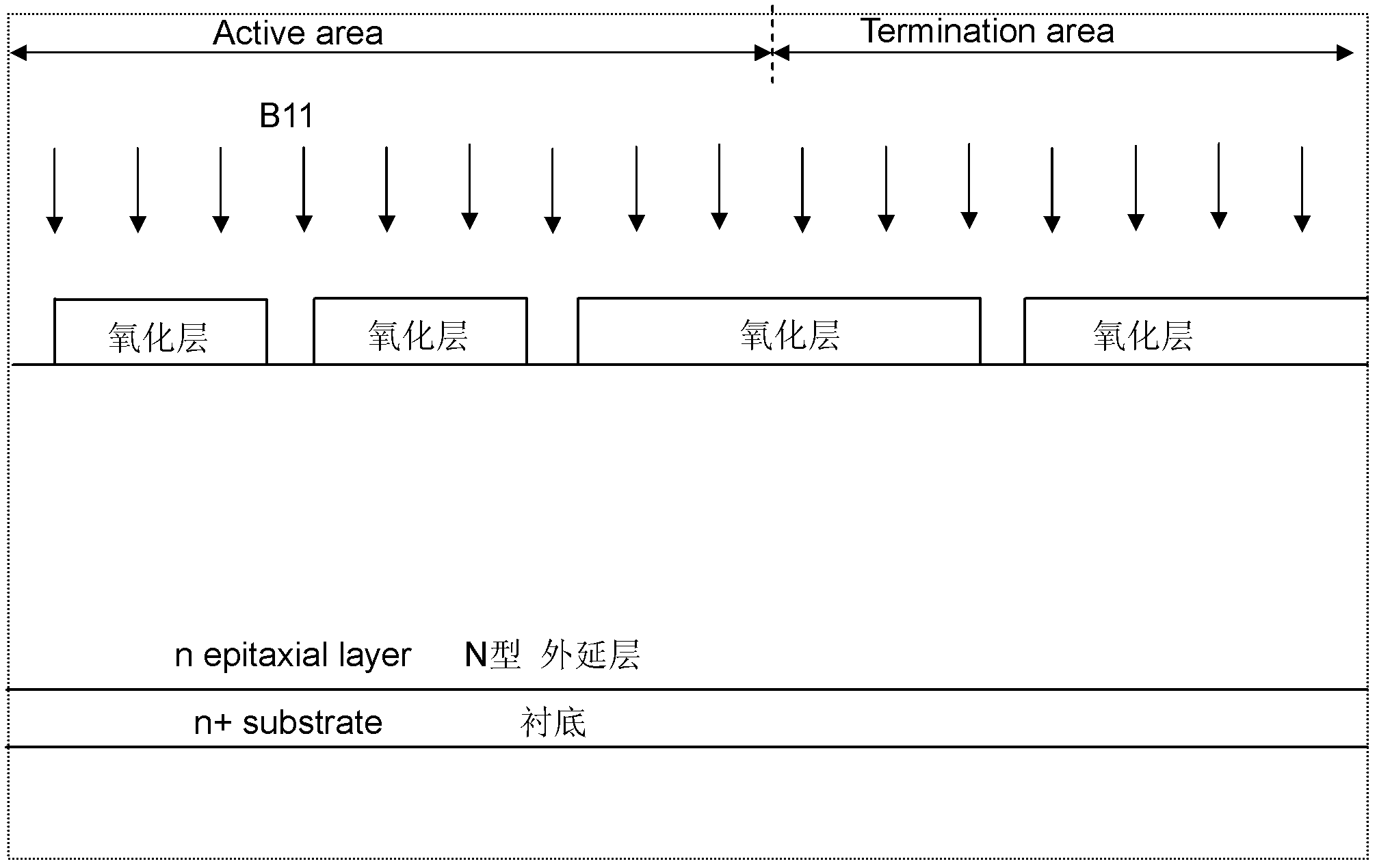

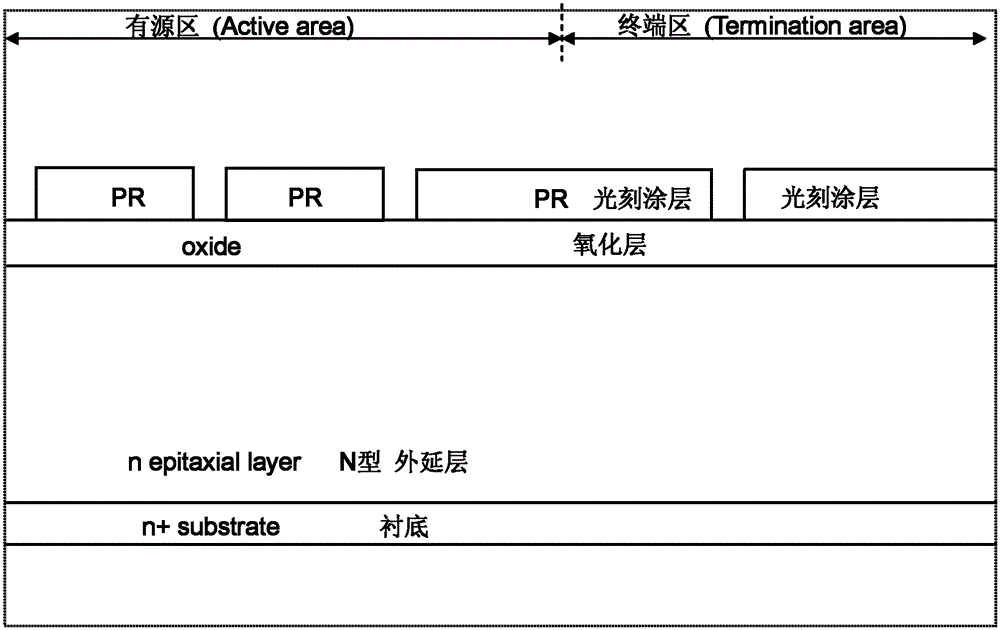

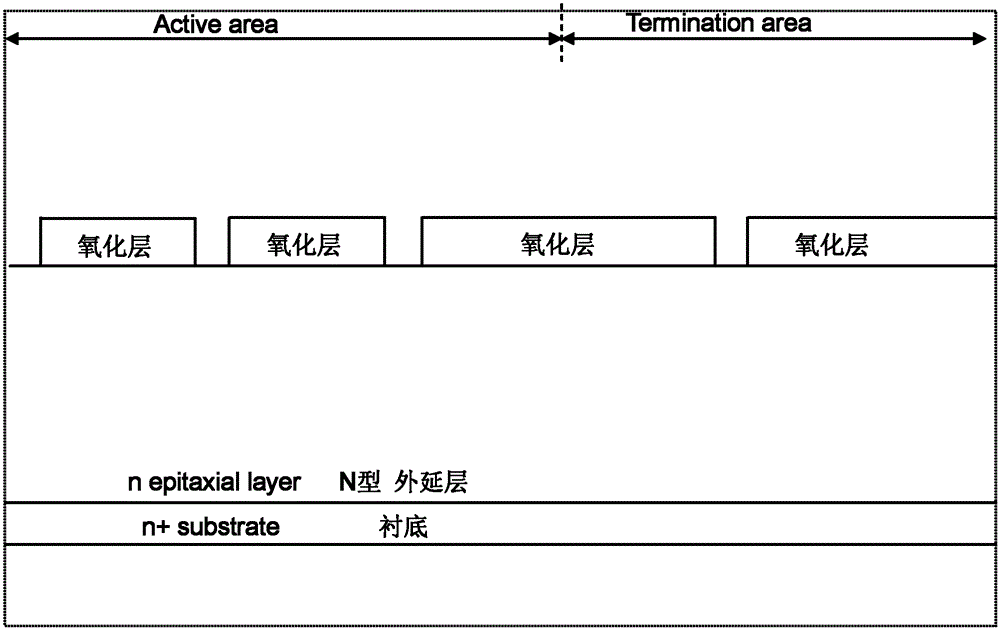

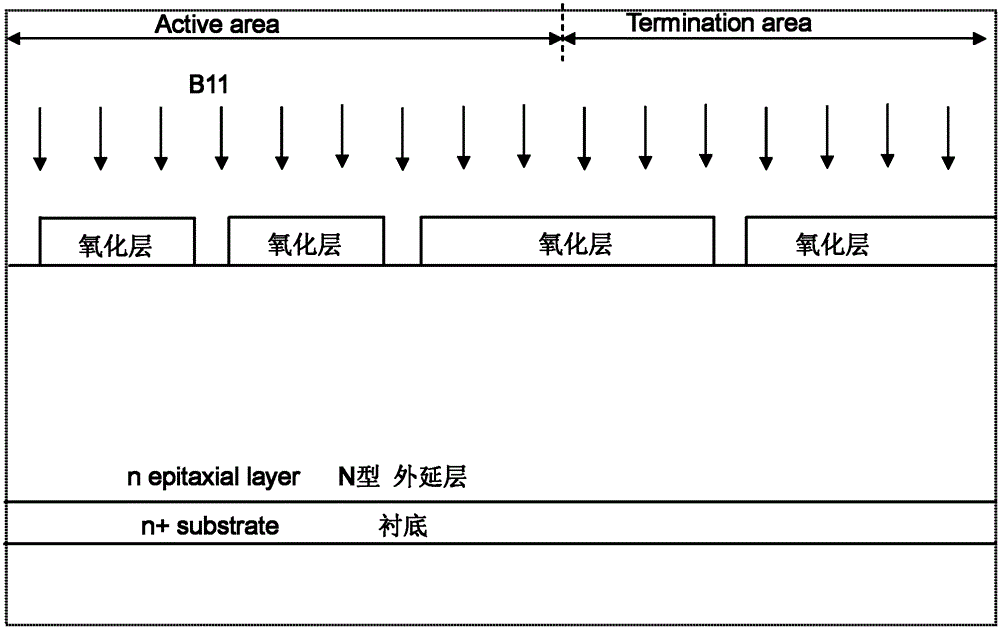

High voltage tolerance element and producing method thereof

InactiveCN101145574ALow costReduce processSolid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorDrain current

The invention discloses a high-voltage resistant element which comprises a semi-conductive substrate and a gate electrode. The semi-conductive substrate comprises a first doping zone with a first conduction type, a second doping zone with a second conduction type, a third doping zone with a second conduction type, a fourth doping zone surrounding the third doping zone and with a second conduction type, and a fifth doping zone surrounding the third doping zone and with a second conduction type. The gate electrode is adjacently equipped between two clearance walls, and divides the second doping zone from the third doping zone to control the communication between the second doping zone and the third doping zone. The high-voltage resistant element utilizes the fifth doping zone to surround the third doping zone, so as to strengthen the encapsulation of the third doping zone, improve the uniformity of ion concentration at the bottom of the third doping zone, and reduce the drain current thereof.

Owner:ADVANCED ANALOG TECH INC

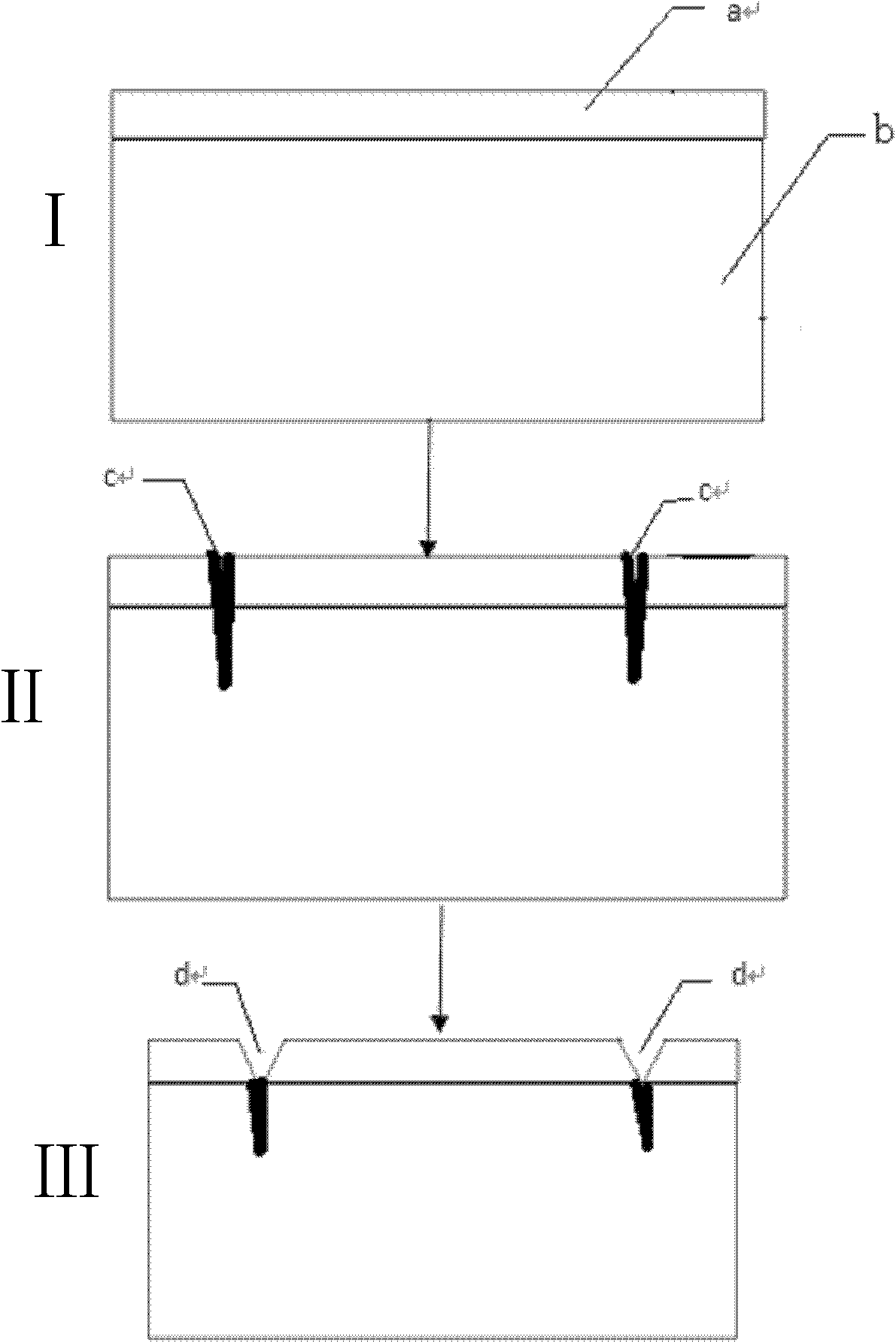

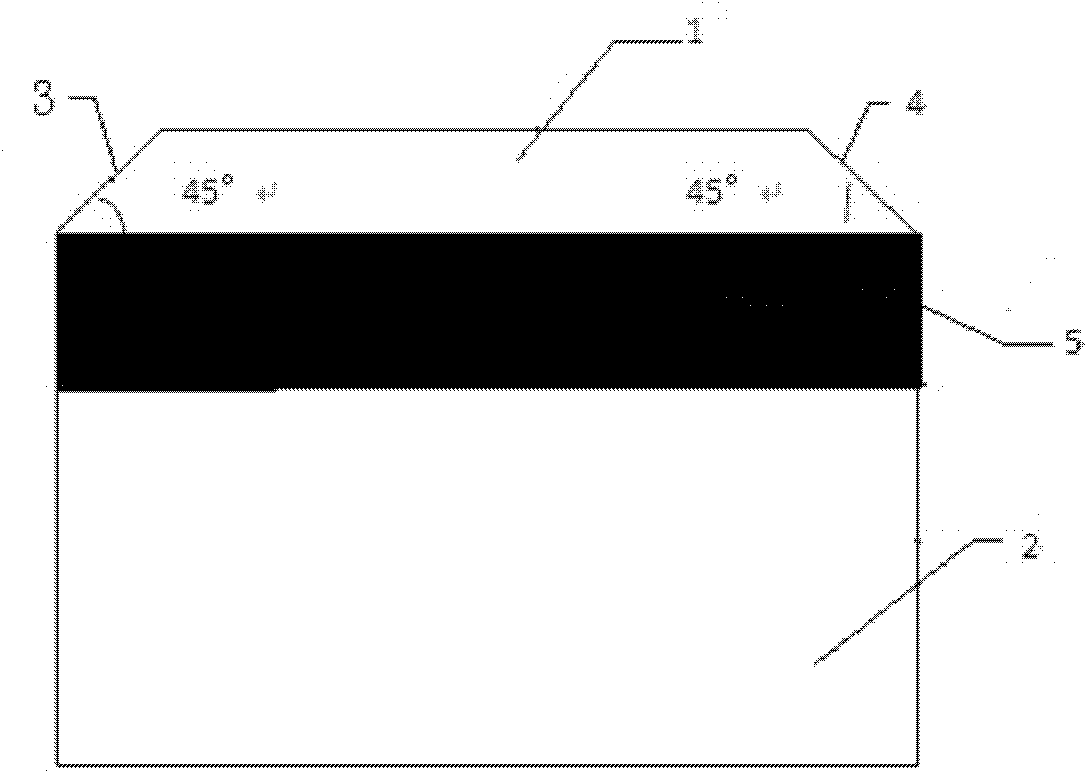

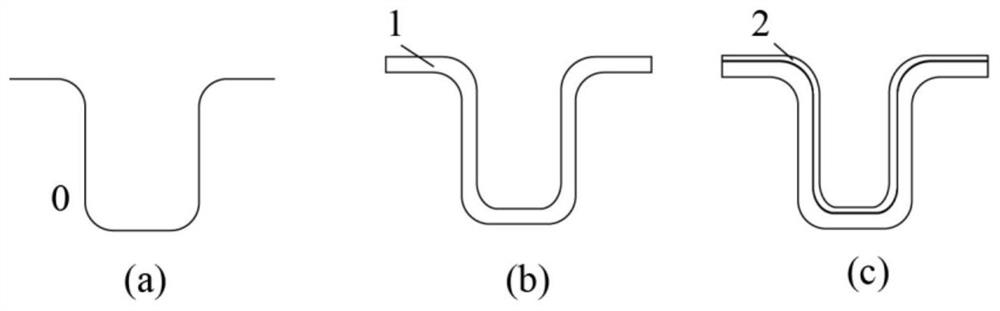

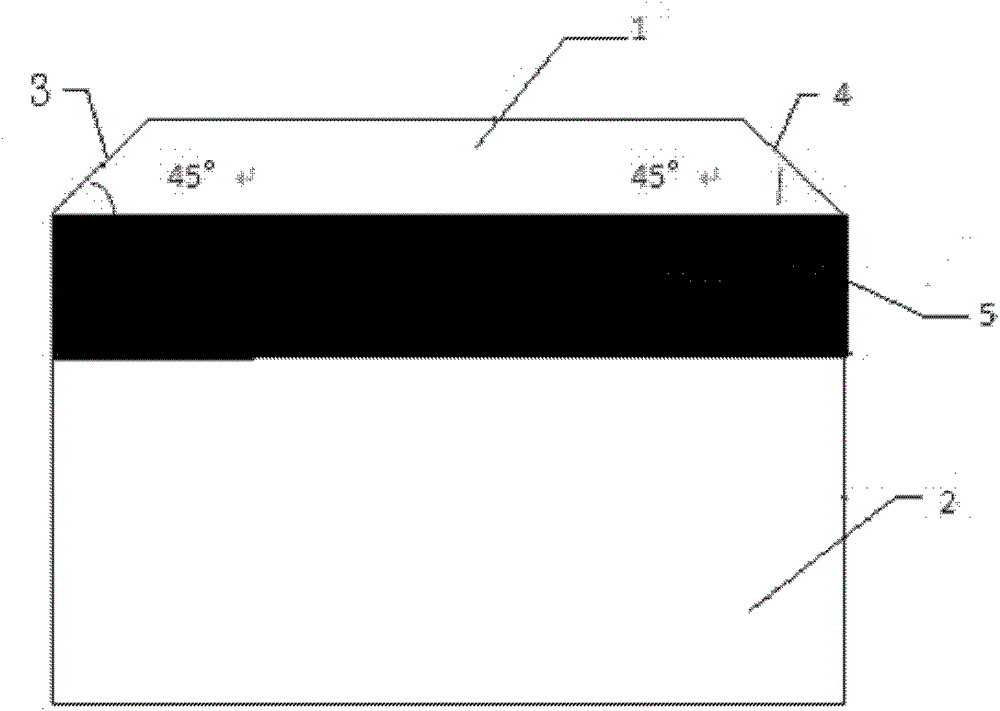

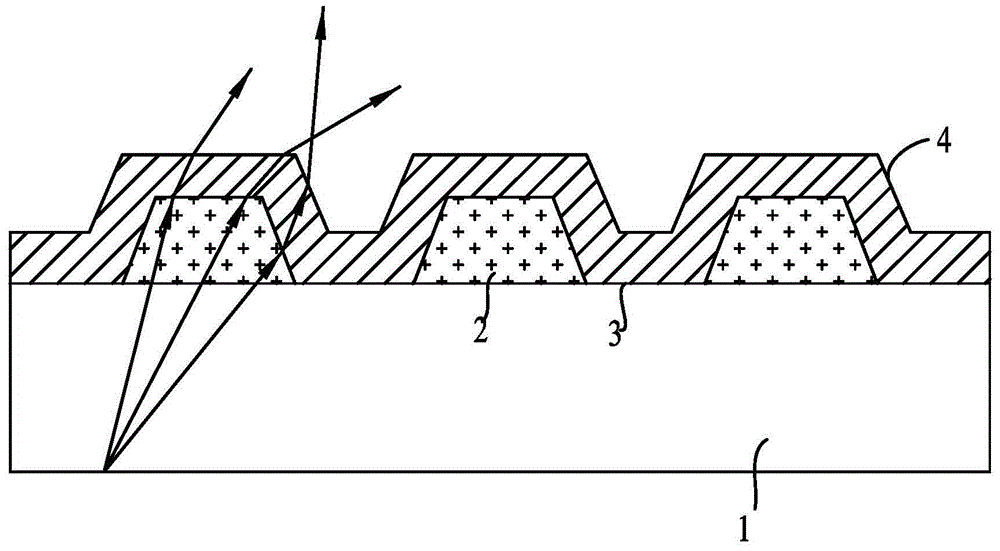

Chip cutting method for increasing LED chip light extraction

ActiveCN102738313AImprove light outputImprove light extraction efficiencyFine working devicesLaser beam welding apparatusEngineeringInverted triangle

A chip cutting method for increasing LED chip light extraction is disclosed. The method comprises the following steps: using a laser to make a scratch on a right side of the chip; then, using a diamond saw blade knife to carry out saw blade along the scratch, wherein the saw blade knife is a bilaterally symmetrical isosceles inverted triangle and an included angle of a knife side surface and a horizontal line is 30-60 DEG; adjusting a knife height of the saw blade knife so that an epitaxial layer is just sawed through; carrying out overturn and inverted membrane on the chip after the saw blade is finished; using a splinter knife to carry out splinter on a back side of the chip along the laser scratch. According to the invention, through a saw blade technology, an epitaxial layer edge of the chip, which is about 10micron, is sawed into an inclined platform. A chip light extraction rate can be increased by more than 20%. Simultaneously, chip appearance is improved. A technology operation is simple and is easy to be realized.

Owner:JIANGSU ETERN +1

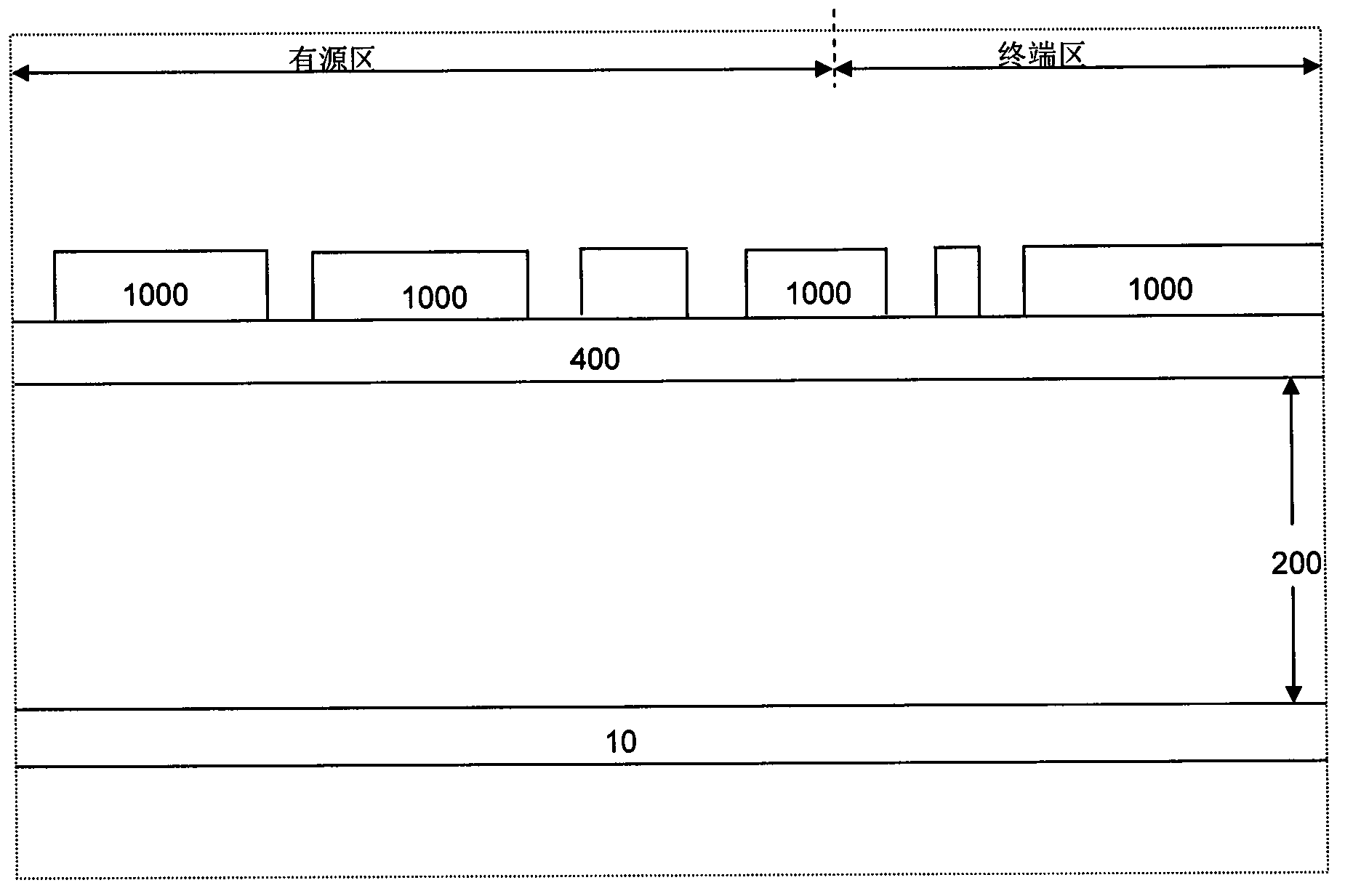

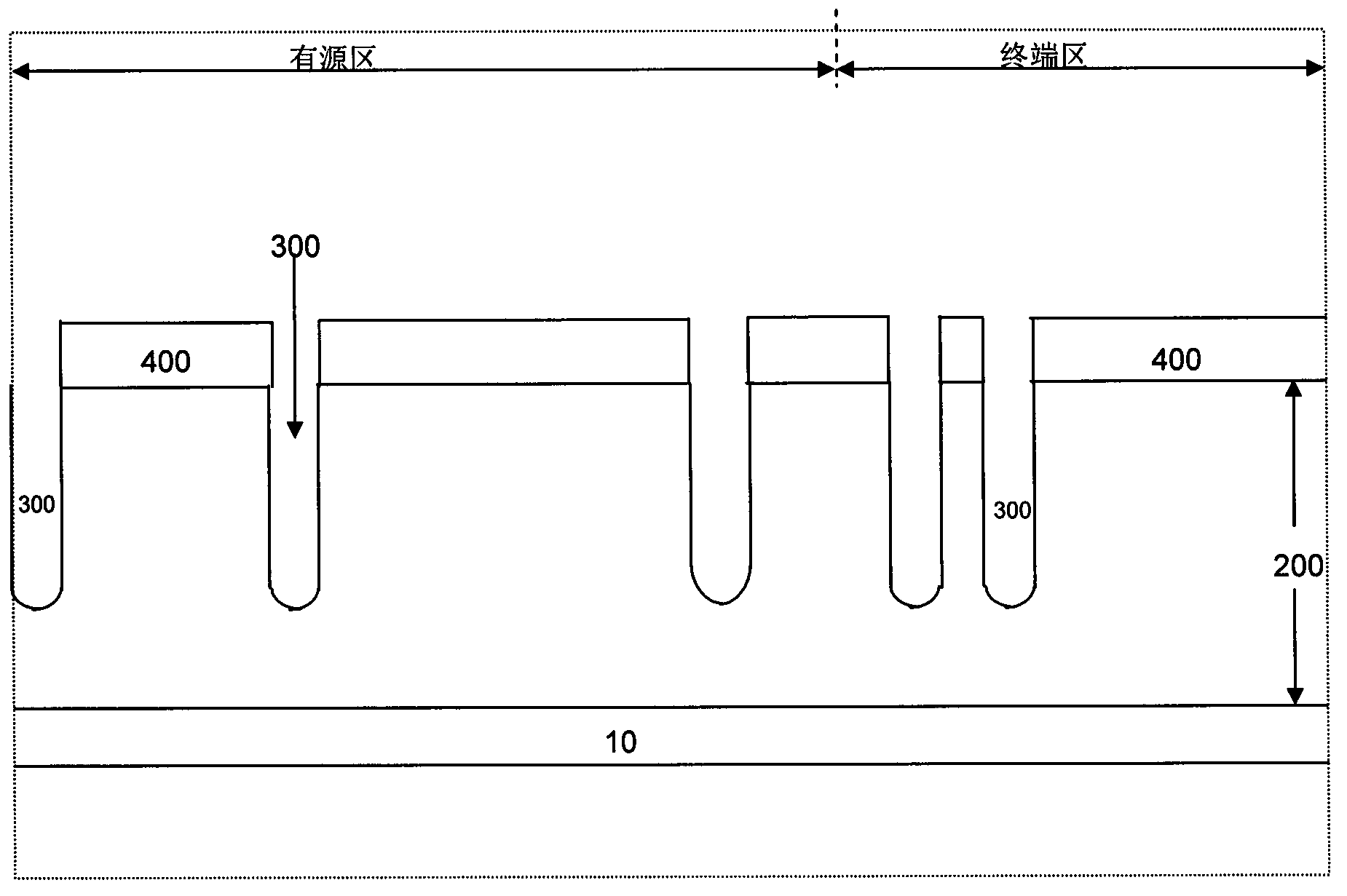

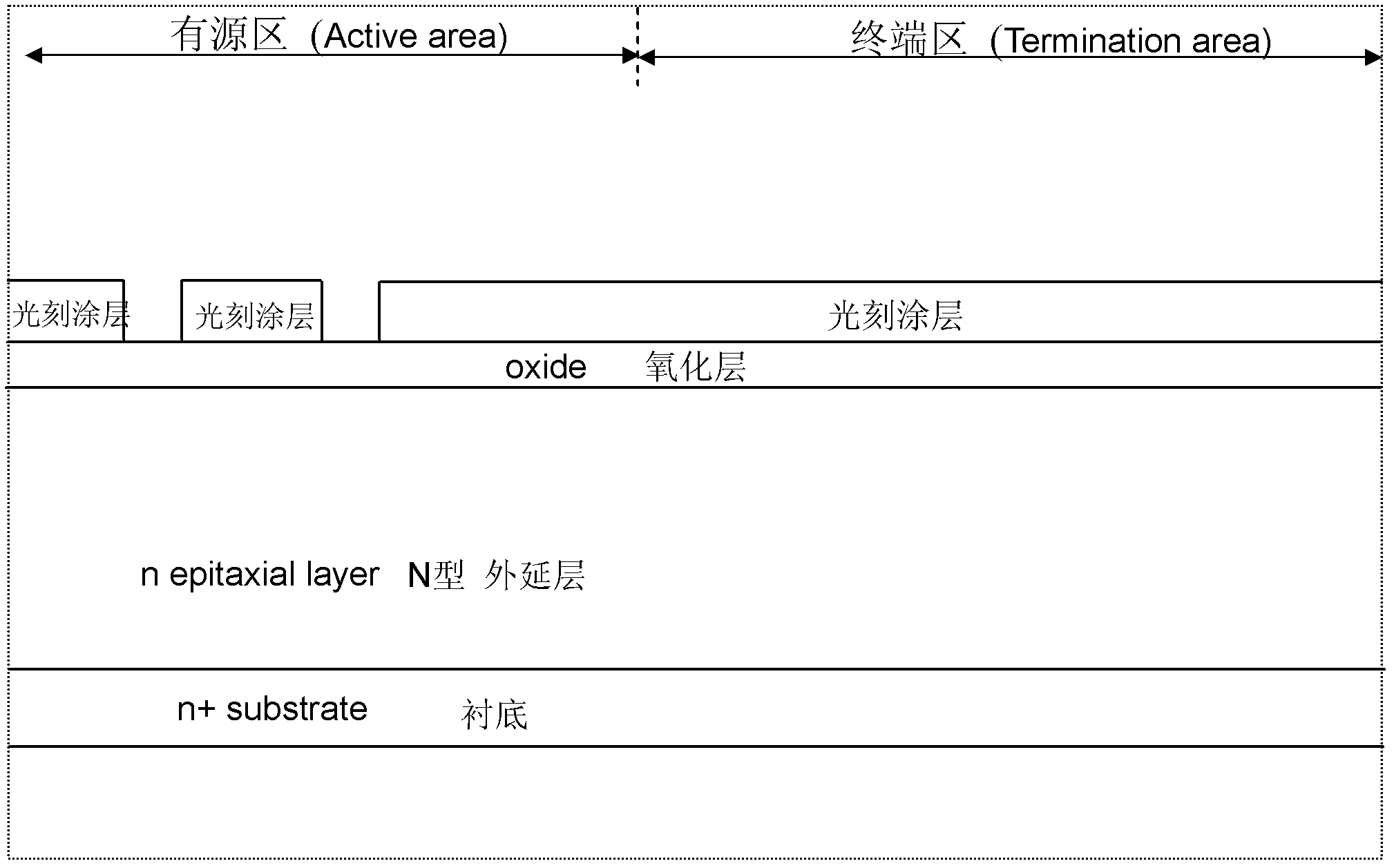

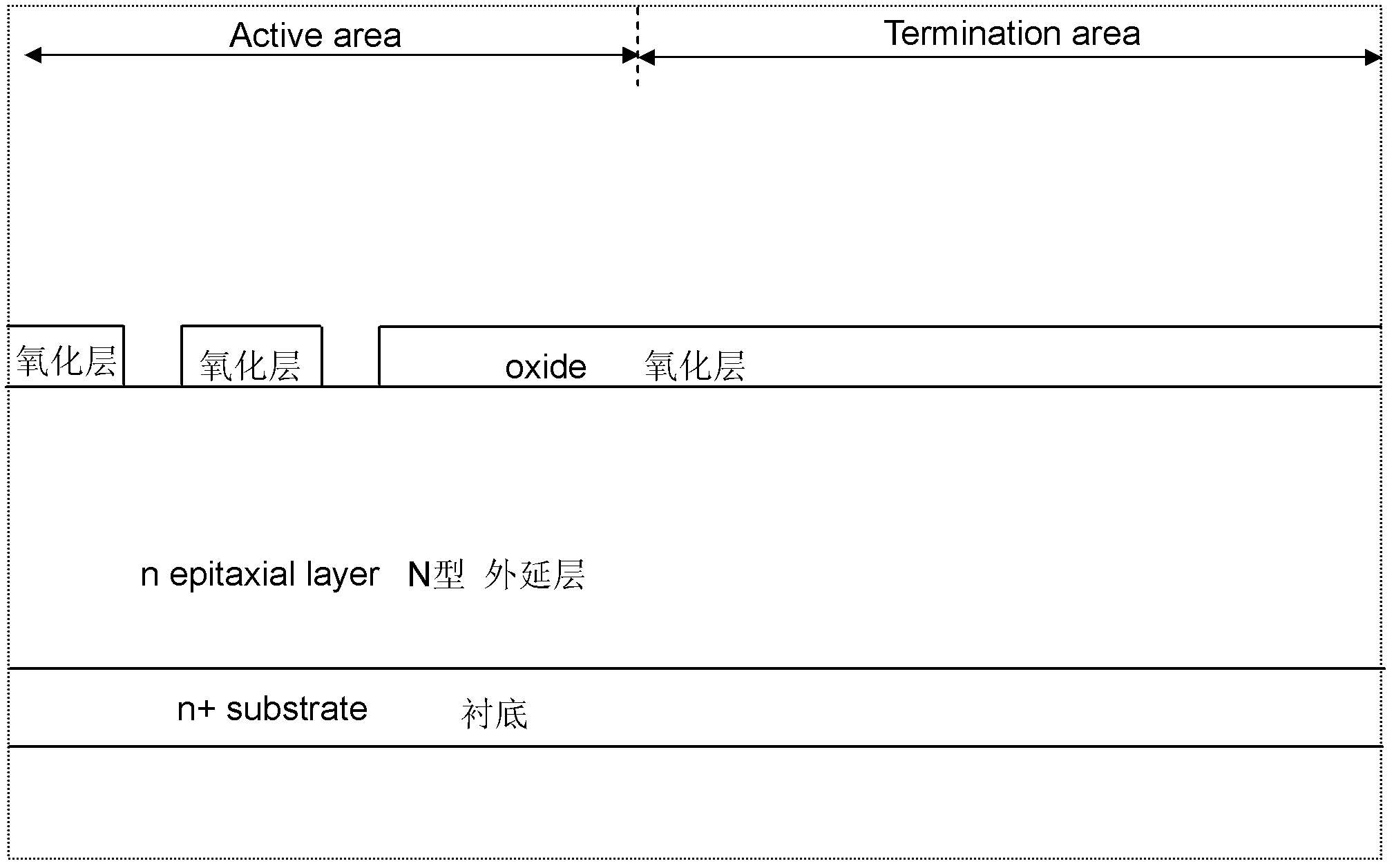

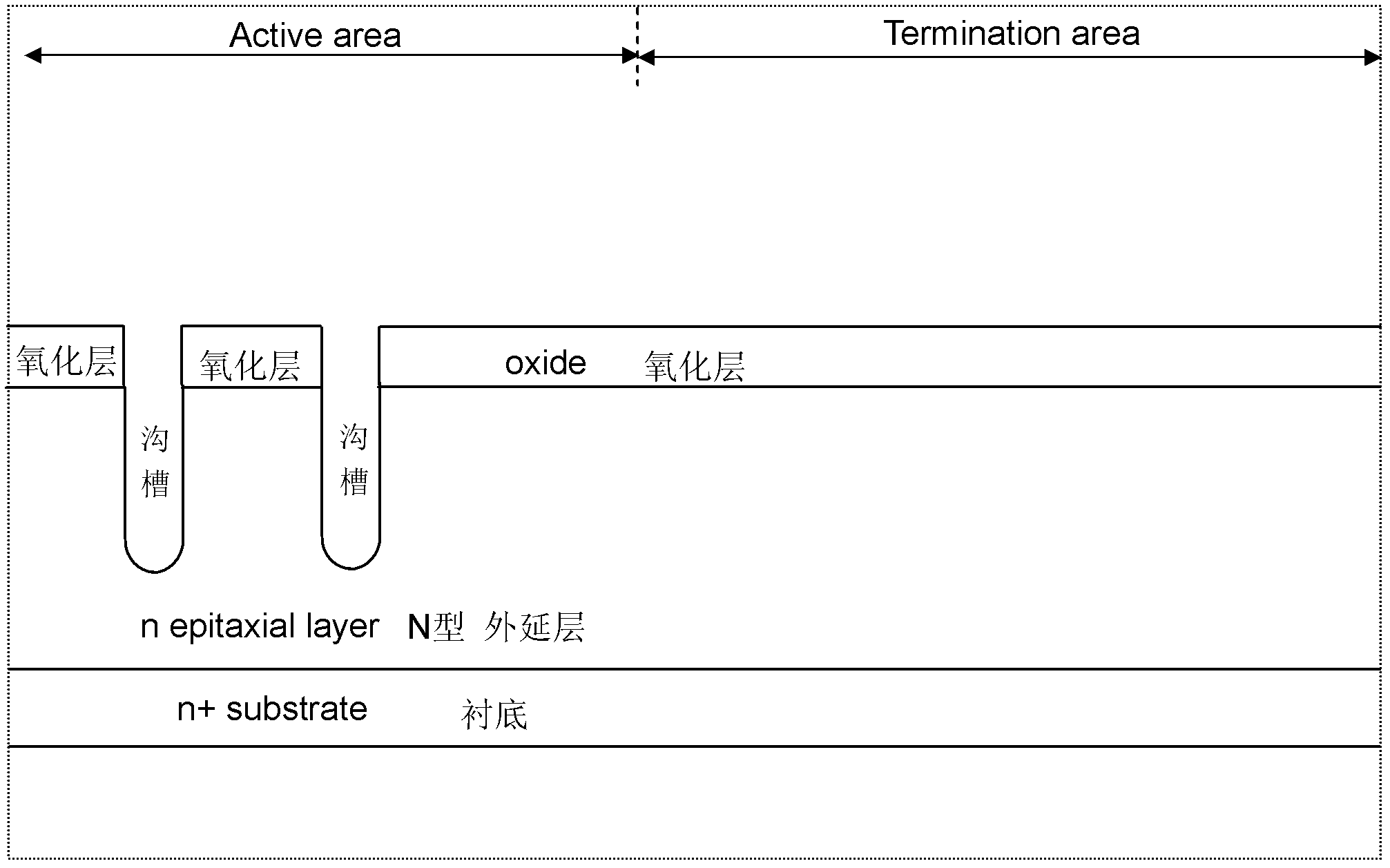

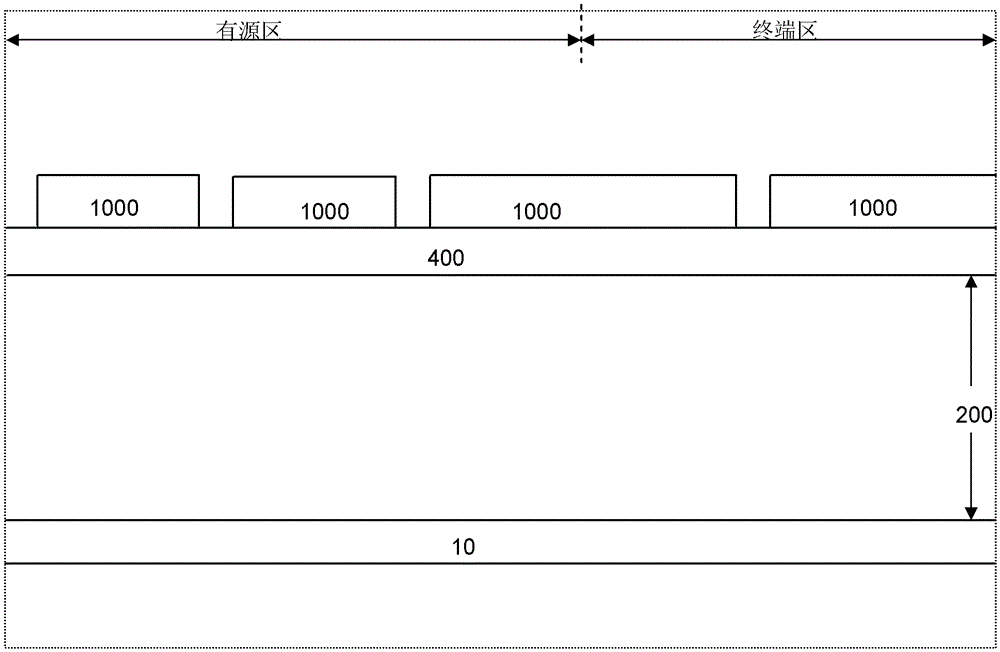

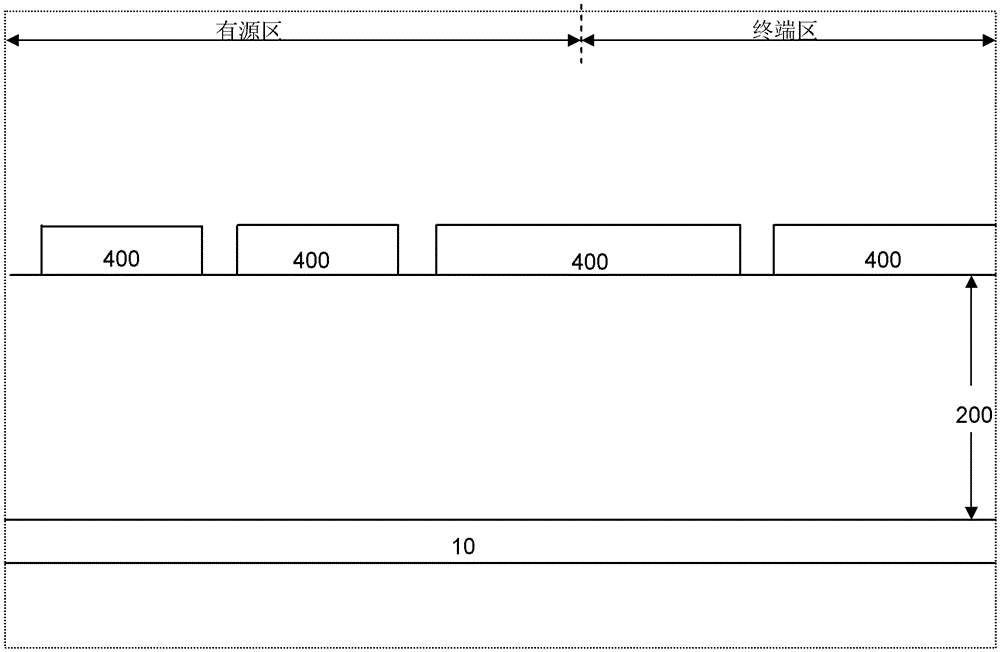

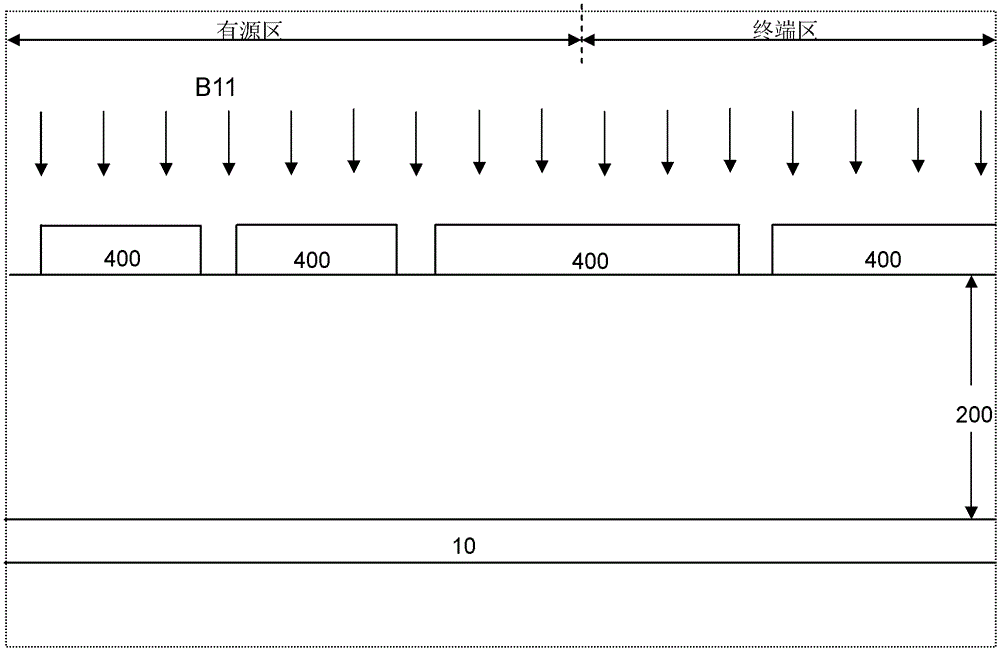

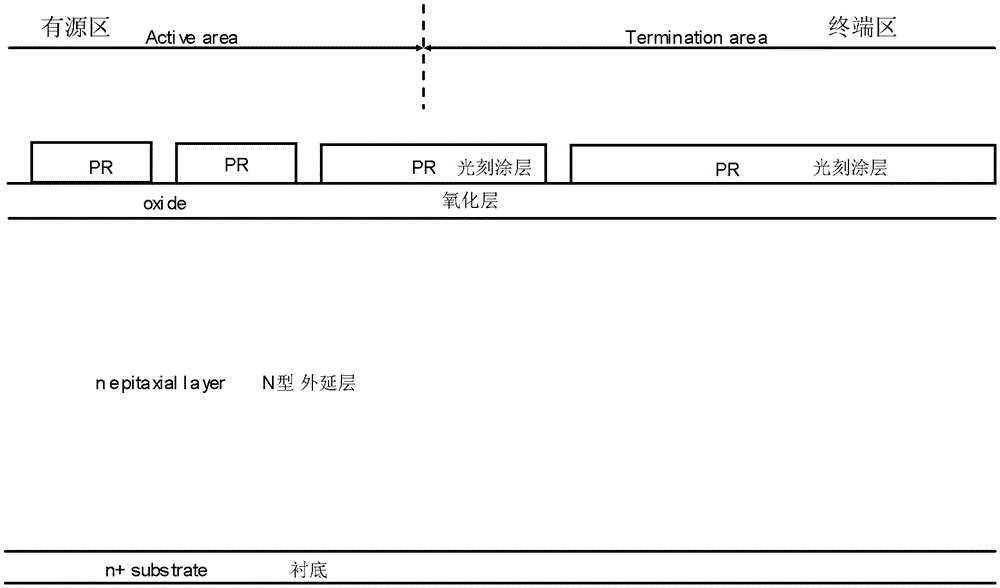

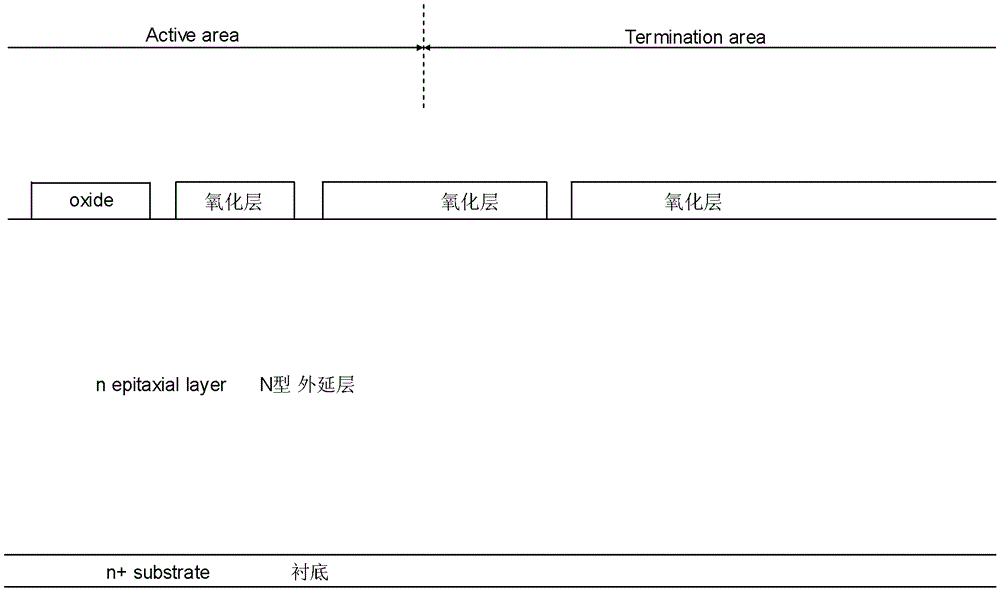

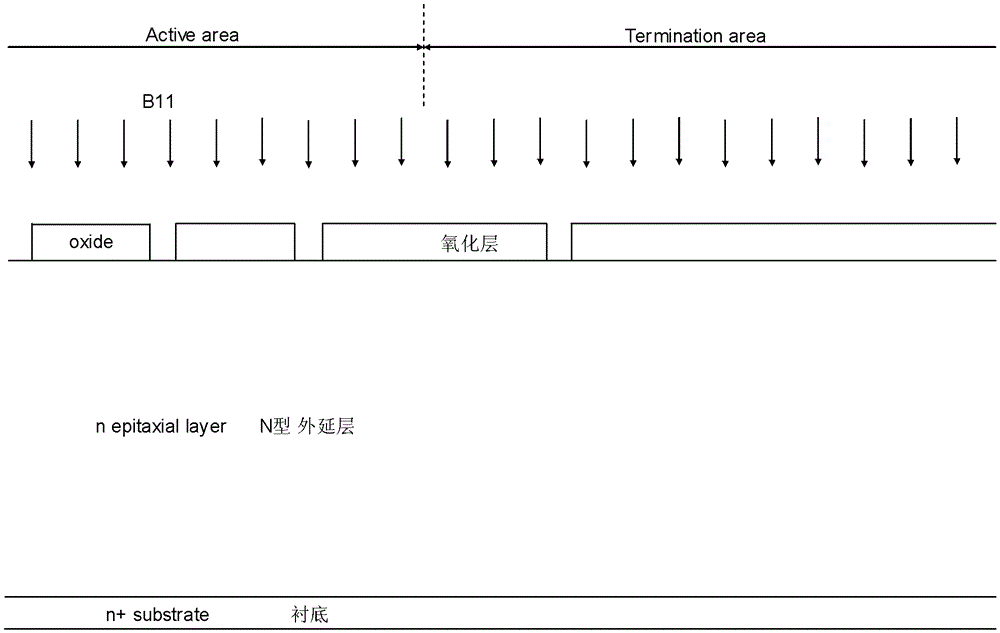

Method of preparing a groove grid-control power device

InactiveCN103632965AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDopantDielectric

The invention discloses a method of preparing a groove grid-control power device, the method comprising the steps of first eroding an epitaxial layer on a substrate by use of a groove mask to form a plurality of grooves; then, injecting a P-type dopant and an N-type dopant into the epitaxial layer to form a P-type base region and an N-type source region respectively, then depositing an interlayer dielectric on the surface of the epitaxial layer, eroding the interlayer dielectric by use of a contact hole mask to form an opening in the interlayer dielectric, eroding the surface of the epitaxial layer later to form a contact hole groove and carrying out metal plugging filling on the contact hole groove; and finally, depositing a metal layer on the surface of a device, and carrying out metal eroding by use of a metal mask to form a metal cushion layer and connection wires. By adopting the method of preparing the groove grid-control power device, preparation procedures of base region masking and source region masking are eliminated, and the preparation cost of the device is greatly reduced.

Owner:SHENZHEN LIZHEN SEMICON

Method of preparing groove grid-control semiconductor power device

InactiveCN103632963AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDopant

The invention discloses a method of preparing a groove grid-control semiconductor power device. The method comprises the steps of first, injecting an P-type dopant into an epitaxial layer on a substrate by use of a groove mask to form a P-type base region, and eroding on the epitaxial layer to form a plurality of grooves; then injecting an N-type dopant into the epitaxial layer to form an N-type source region, then depositing an interlayer dielectric on the surface of the epitaxial layer, eroding the interlayer dielectric by use of a contact hole mask to form an opening in the interlayer dielectric, eroding the surface of the epitaxial layer later to form a contact hole groove and carrying out metal plugging filling on the contact hole groove; and finally, depositing a metal layer on the surface of a device, and carrying out metal eroding by use of a metal mask to form a metal cushion layer and connection wires. By adopting the method of preparing the groove grid-control semiconductor power device, preparation procedures of base region masking and source region masking are eliminated, and the preparation cost of the device is greatly reduced.

Owner:SHENZHEN LIZHEN SEMICON

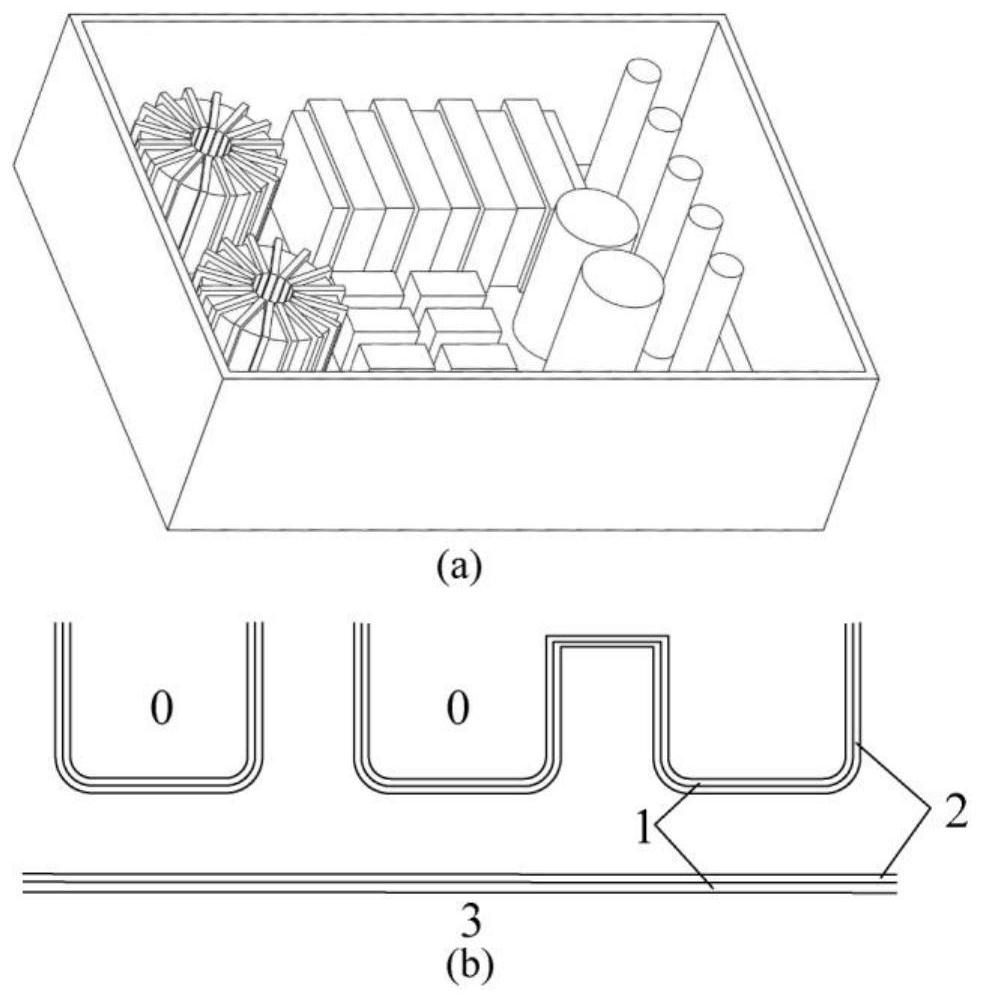

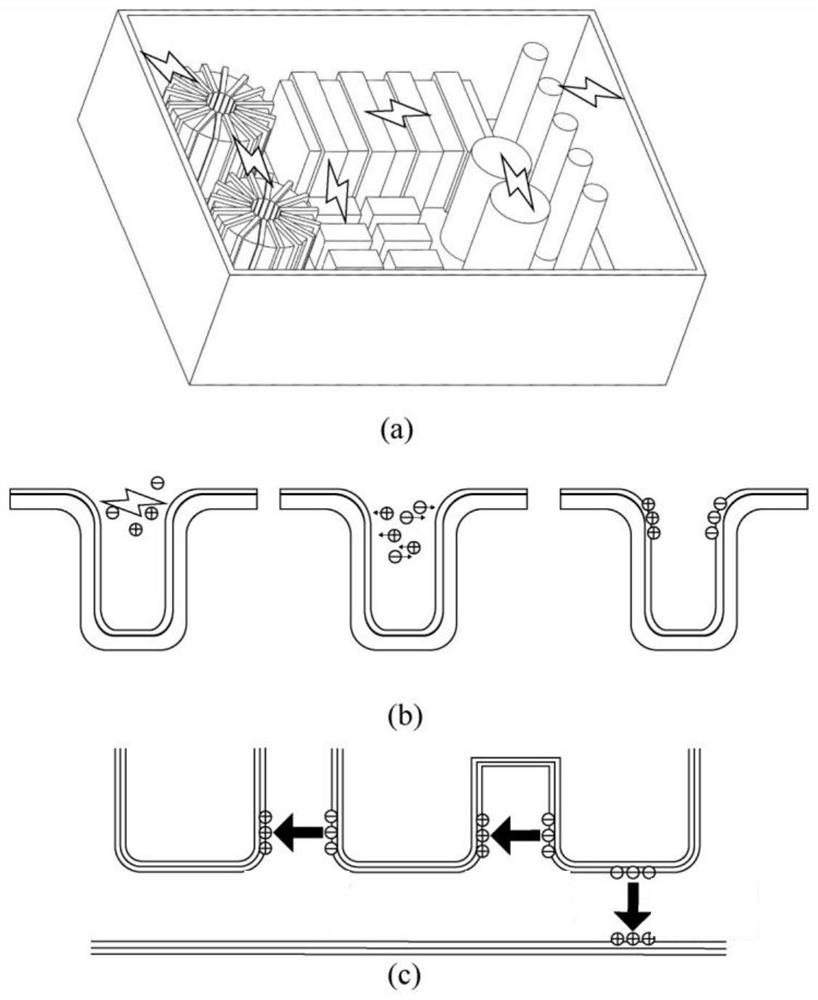

Discharge detection system and method based on poly-p-xylylene film and charged particles

ActiveCN112327116ANo dead corner coveragePrecise positioningTesting dielectric strengthChemical vapor deposition coatingXylyleneMicron scale

The invention discloses a discharge detection system and method based on a poly-p-xylylene film and charged particles. Based on a film deposition technology, a poly-p-xylylene film is deposited in a complex, closed and micro electrical and electronic system and on the surface of an electrical and electronic system in an embedded manner; the micron-sized poly-p-xylylene film is conformal with an electrical and electronic system, so that large-area, all-around and dead-angle-free coverage in the electrical and electronic system is realized; based on a poly-p-xylylene film polarity technology andin combination with the electrostatic interaction of charged particles, discharge detection of the whole electrical and electronic system, precise discharge positioning of the electrical and electronic system in the system and calculation of discharge key parameters are realized; according to the invention, the universality of the discharge detection technology is improved, and the problem that the existing discharge detection technology cannot realize the detection and accurate positioning of the internal discharge of a complex, closed and micro system is solved; the effectiveness and the precision of the discharge detection technology are improved; and the robustness of the discharge detection technology for resisting the interference of the internal environment of the system is improved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

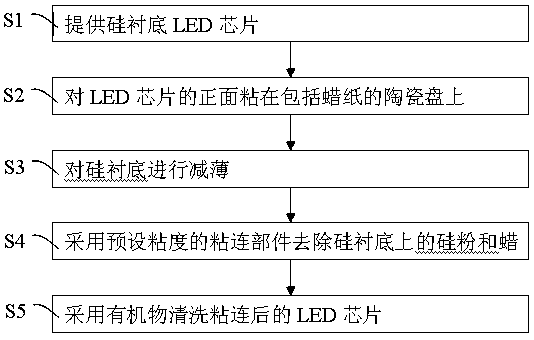

Chip thinning-based cleaning method

InactiveCN108172498AEasy to cleanDoes not affect electrical characteristicsSemiconductor/solid-state device manufacturingEnvironmental resistanceWax

The invention discloses a chip thinning-based cleaning method. The chip thinning-based cleaning method comprises the steps of providing a silicon substrate LED chip; pasting a front surface of the LEDchip onto a ceramic disc comprising wax paper; thinning the silicon substrate; removing silicon powder and wax on the silicon substrate by employing a pasting part with preset viscosity; and cleaningthe pasted LED chip with an organic substance. Before cleaning the LED chip with a cleaning liquid, the silicon powder and the wax are removed by a physical mode, the electrical characteristic of theLED chip cannot be affected, and environmental protection is facilitated.

Owner:南昌易美光电科技有限公司

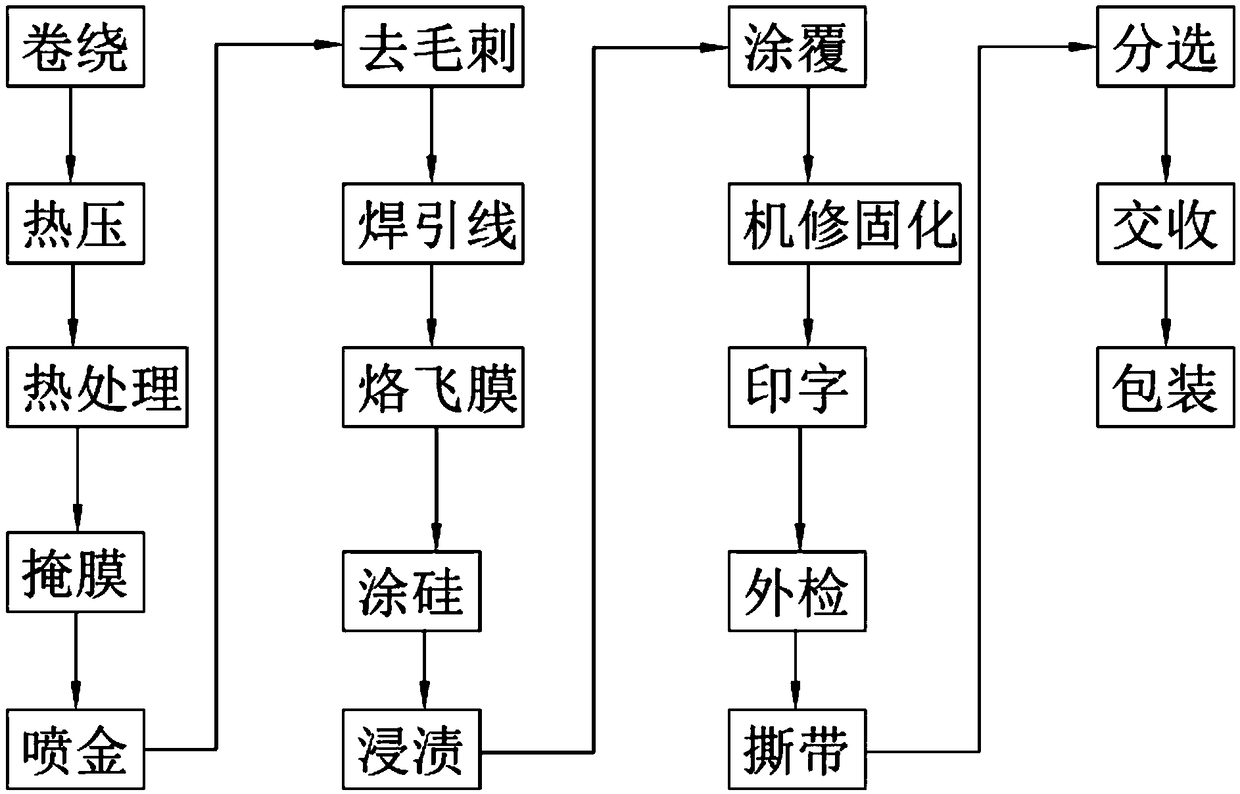

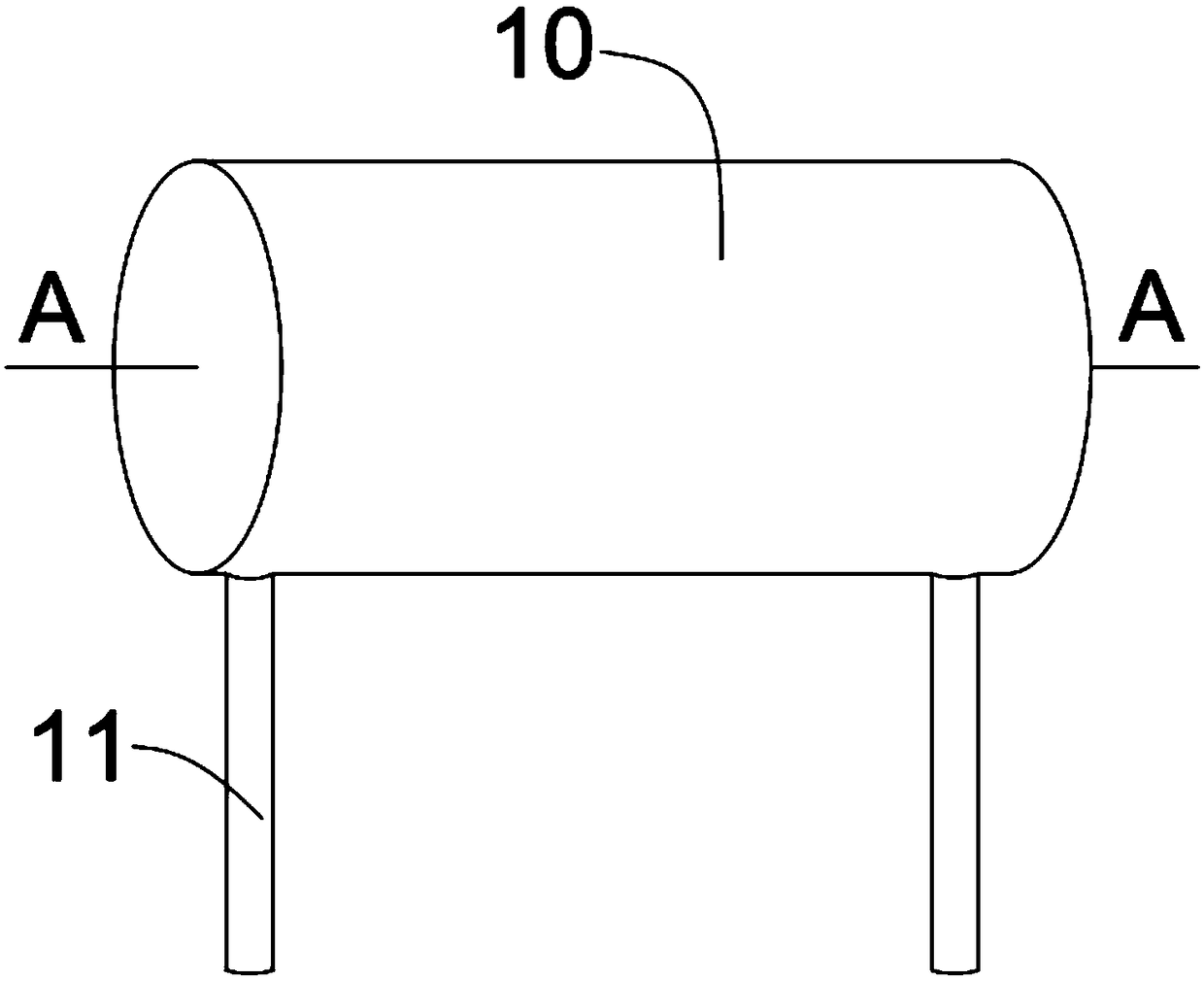

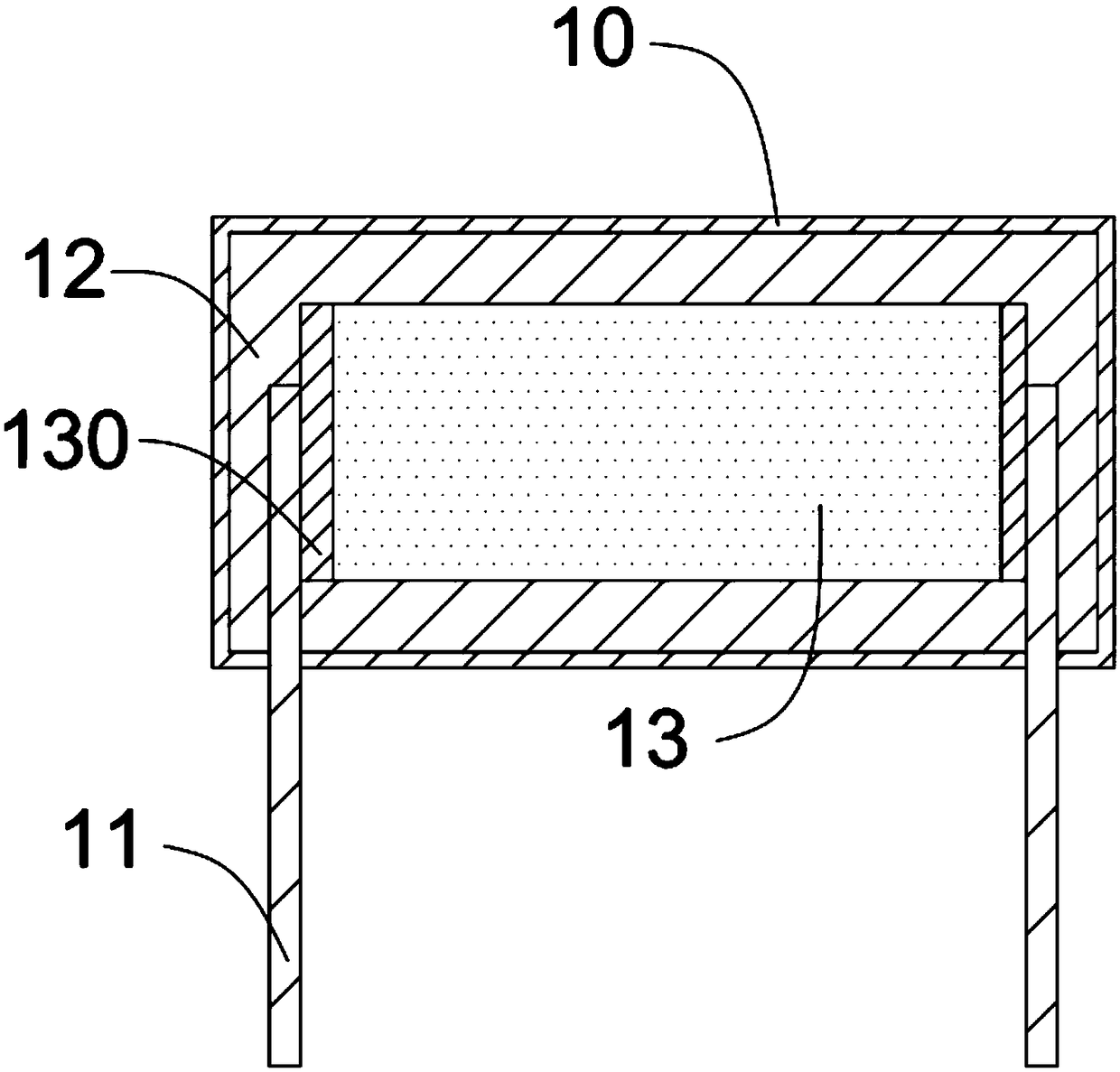

Preparation method of low-noise thin film capacitor

ActiveCN108831764ADoes not affect electrical characteristicsStress reliefThin/thick film capacitorStacked capacitorsLow noiseFilm capacitor

The invention belongs to the technical field of metallized capacitor production, in particular to a preparation method of a low-noise thin film capacitor. The preparation method of the low-noise thinfilm capacitor of the invention maintains the original electrical characteristics, and the tested decibel of the noise is less than 25dB, which meets the requirement of the intelligent home for the noise decibel.

Owner:SICHUAN ZHONGXING ELECTRONICS

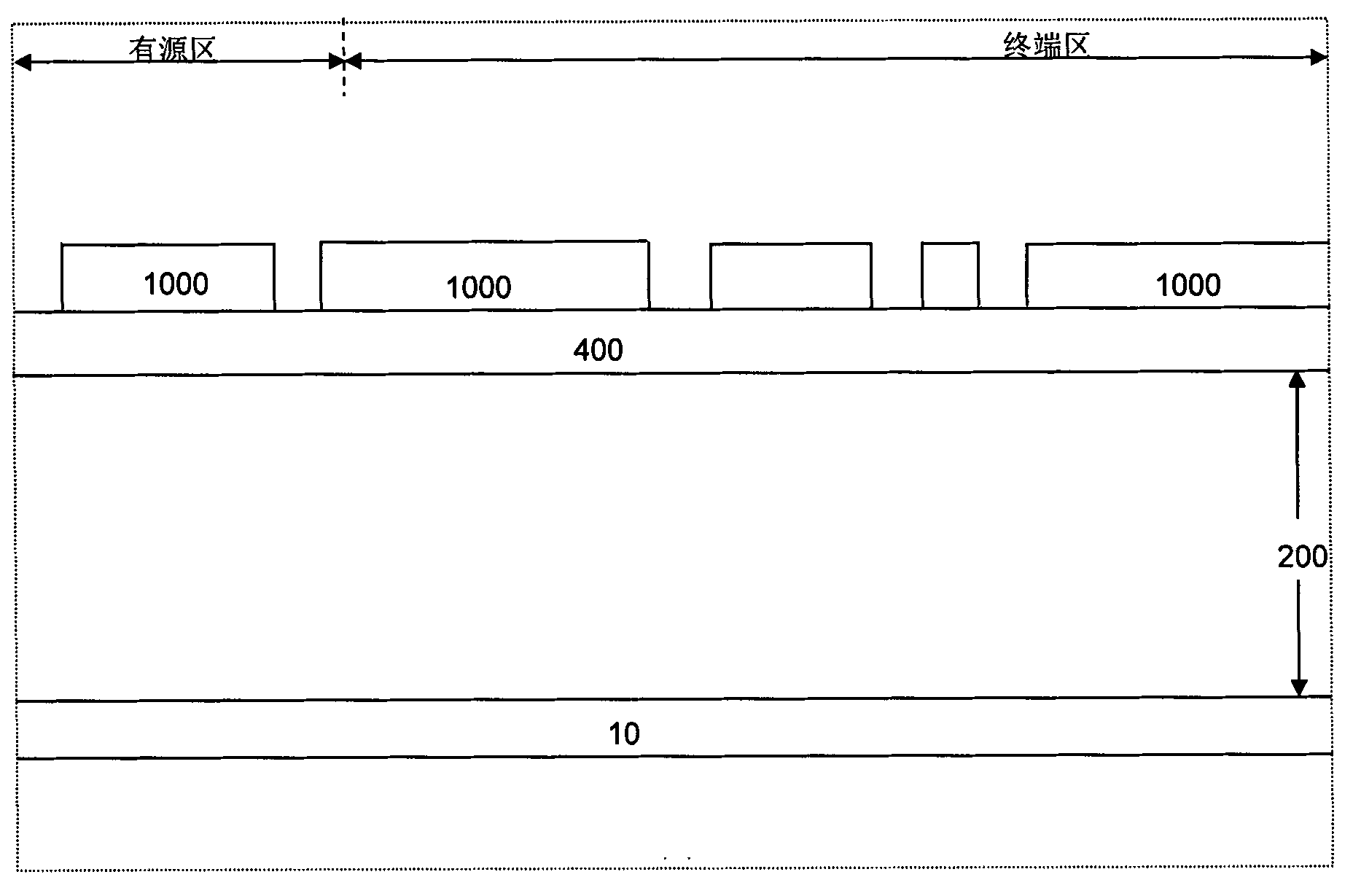

Preparation method of trench semiconductor power discrete device

InactiveCN103187281AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantP type doping

The invention discloses a preparation method of a trench semiconductor power discrete device. The preparation method of the trench semiconductor power discrete device includes a first step of injecting P-type dopant into an epitaxial layer arranged on a substrate to form P-type base regions through a trench mask and conducting corrosion on the epitaxial layer to form a plurality of grid trenches; a second step of depositing interlayer mediums on the epitaxial layer, conducting the corrosion on the interlayer mediums through a contact hole mask, forming trenches in the interlayer mediums, injecting N-type dopant to form N-type source regions, conducting the corrosion on the surface of the epitaxial layer to form contact trenches, and conducting metal plugging filling on the contact trenches; and a third step of depositing a metal layer on the surface of the discrete device, conducting metal corrosion through a metal mask and forming a metal substrate layer and a connecting wire. The preparation method of the trench semiconductor power discrete device eliminates preparation procedures of a base region mask and a source region mask, and therefore the manufacturing cost of the discrete device is greatly reduced. In addition, original electrical characteristics of the discrete device cannot be influenced.

Owner:立新半导体有限公司

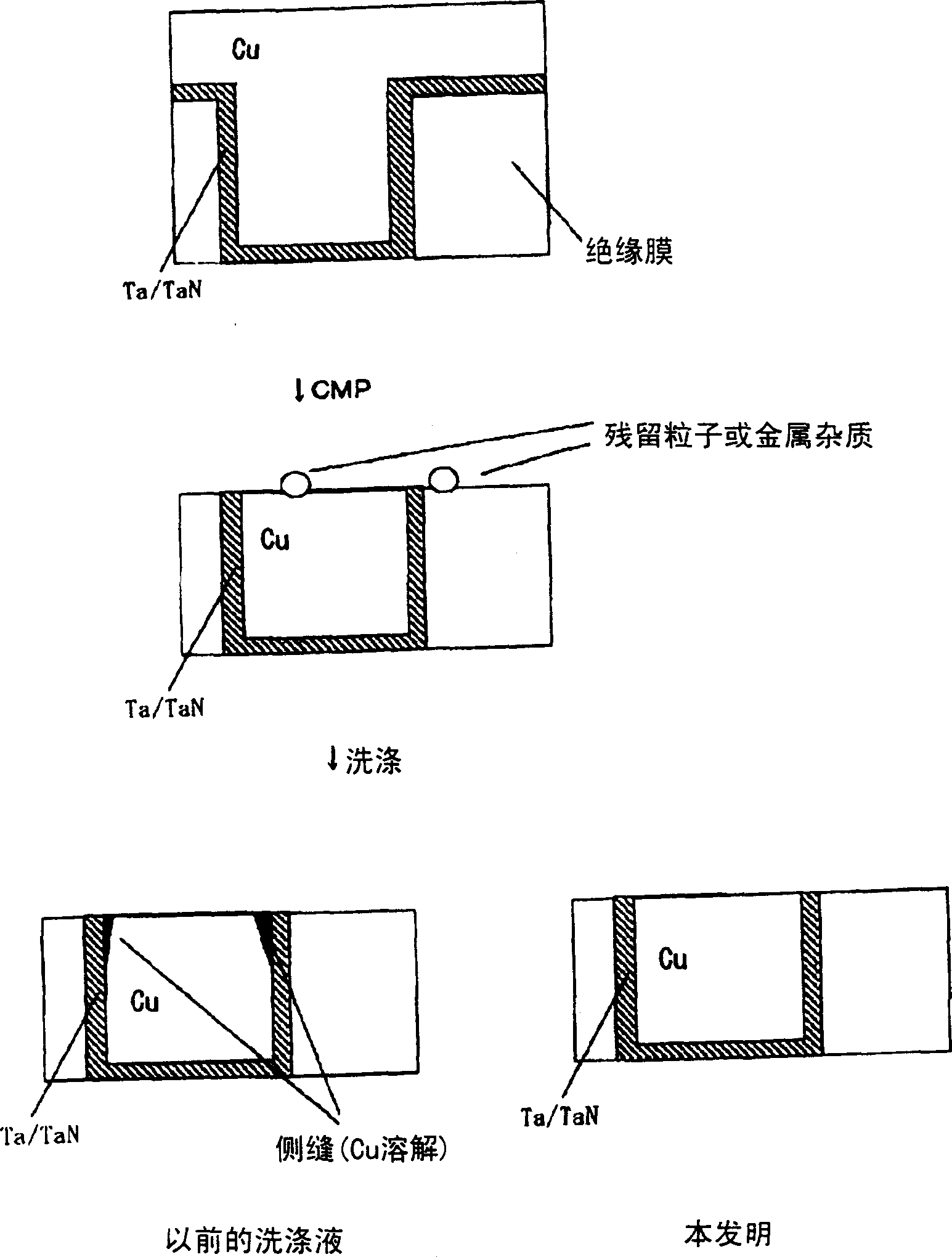

Cleaning liquid composition after chemical and mechanical grinding

InactiveCN1458256ADoes not affect electrical characteristicsRestraint side seamSurface-active detergent compositionsDetergent mixture composition preparationGlyoxylic acidMetal impurities

Owner:RENESAS ELECTRONICS CORP

Preparation method for groove semiconductor discrete device

InactiveCN103187287AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSource areaElectric properties

The invention discloses a preparation method for a groove semiconductor discrete device. The preparation method for the groove semiconductor discrete device includes the following steps: firstly, eroding an epitaxial layer by utilization of a groove mask to form a plurality of grid electrode grooves; then depositing interlayer medium on the surface of the epitaxial layer, eroding the interlayer medium by utilization of a contact hole mask, open holes are formed in the interlayer medium, injecting p-type and n-type dopant to respectively form a p-type base area and a n-type source area, eroding the surface of the epitaxial layer to form contact grooves, and filling the contact grooves through metal inserting plugs; and finally, depositing a metal layer on the upper surface of the device, and performing metal erosion by utilization of a metal mask to form a metal padding layer and connecting lines. By adoption of the preparation method, the preparation processes of a base area mask and a source area mask are omitted, and manufacturing cost of the device is enabled to be reduced greatly; and meanwhile, original electric properties and reliability of the device can not be affected, and therefore the performance / cost ratio of the device is increased.

Owner:立新半导体有限公司

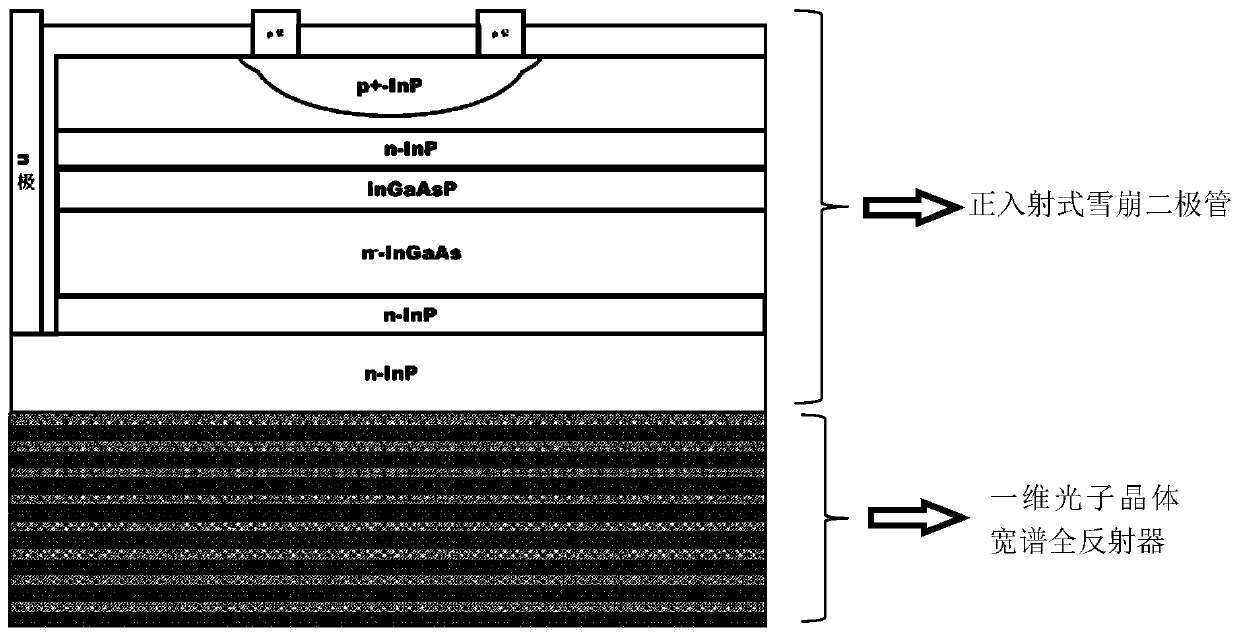

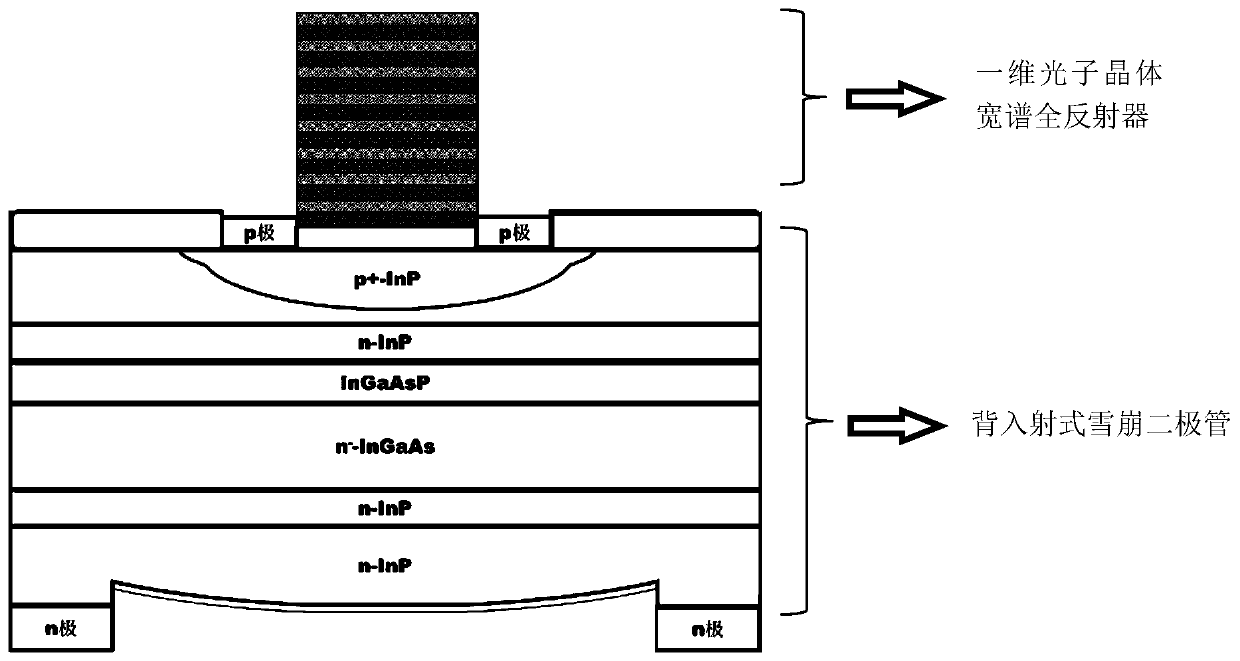

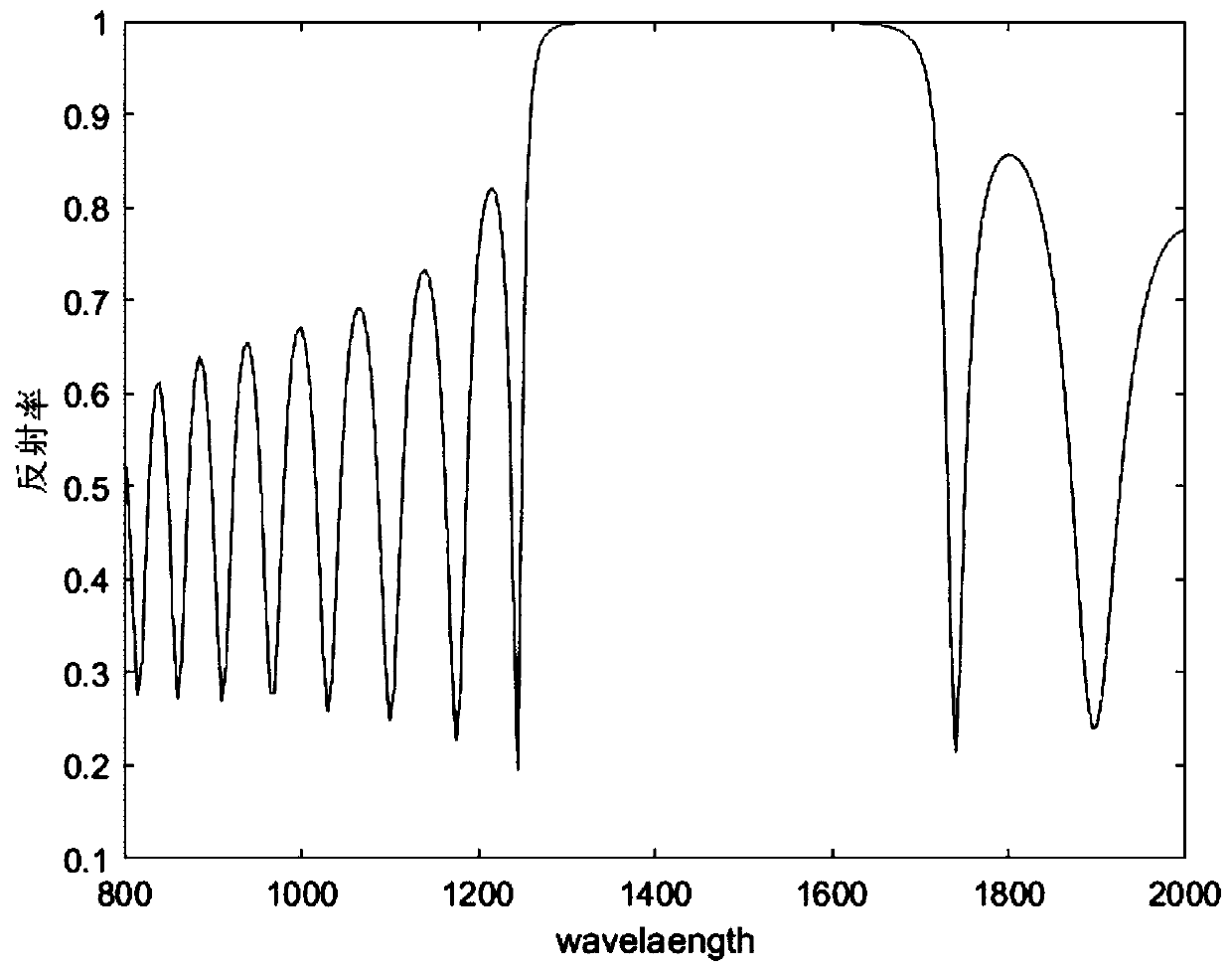

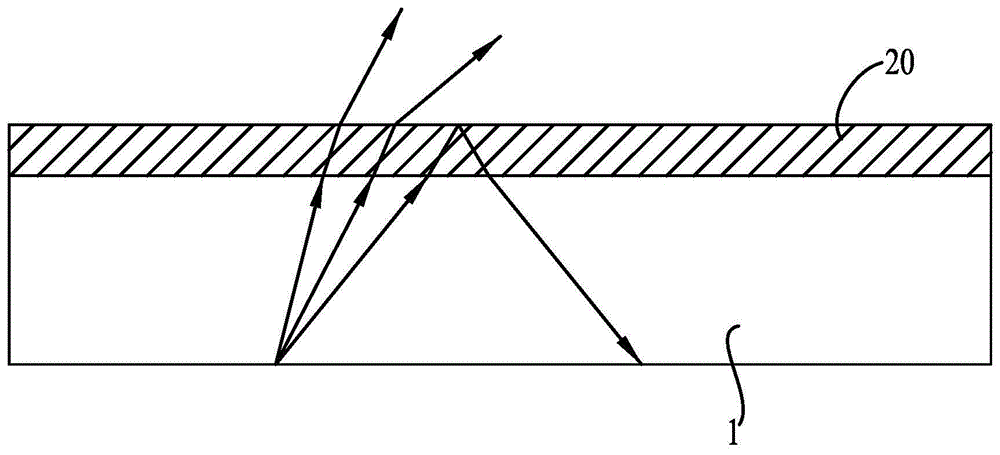

Avalanche photodiode optimized based on photonic crystal broadband total reflector

InactiveCN109860327AImprove quantum efficiencyImprove responsivenessSemiconductor devicesDielectricQuantum efficiency

The present invention discloses an avalanche photodiode optimized based on a photonic crystal broadband total reflector and a manufacturing method thereof. The avalanche photodiode is a one-dimensional photonic crystal broadband total reflector alternately formed by multiple layers of SiO2 dielectric films and TiO2 dielectric films at the back surface of the substrate of a normal incidence avalanche photodiode or the front surface of a back incidence avalanche photodiode. The one-dimensional photonic crystal broadband total reflector reflects light which is not absorbed by an absorption layerin the incident light back to the absorption layer in the avalanche photodiode for absorption again. Compared to a current avalanche photodiode, the one-dimensional photonic crystal broadband total reflector is added to reflect the light which is not absorbed by the absorption layer back to the absorption layer for secondary absorption for all the incident light with different angles with opticalcommunication wave bands of 1310-1675nm without influence of the device frequency response so as to increase the quantum efficiency and responsivity of the device and improve about 50% performances ofthe device.

Owner:南京科普林光电科技有限公司

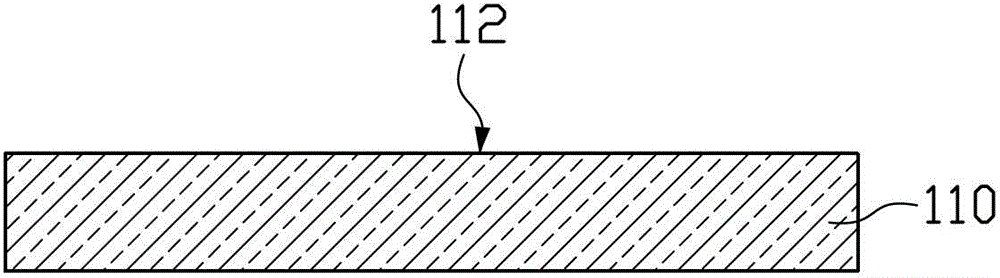

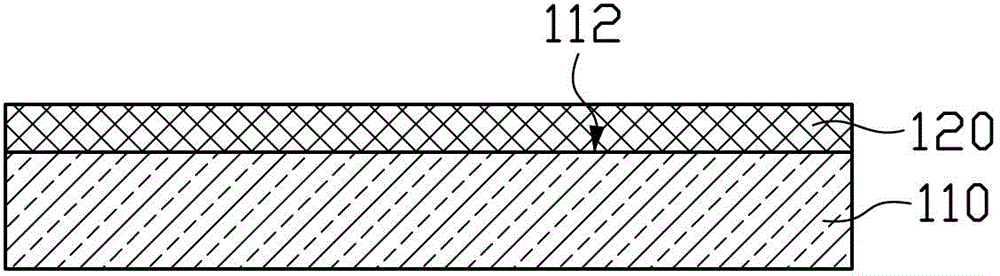

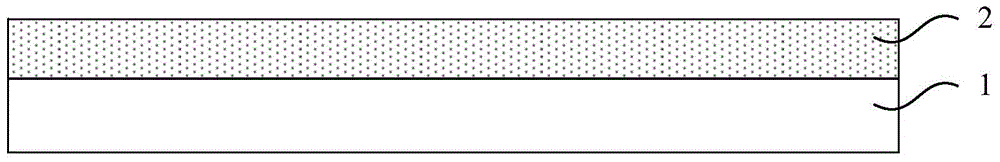

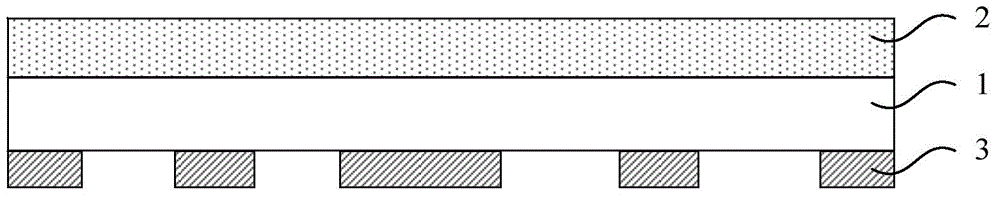

Method for manufacturing flexible display and substrate for manufacturing flexible display

ActiveCN102769109BEasy to manufactureQuality improvementFinal product manufactureSolid-state devicesDisplay deviceFlexible display

A method of manufacturing a flexible display includes forming a silicon sacrificial layer on a rigid base material layer, affixing a flexible base material layer to the silicon sacrificial layer by an adhesive layer, forming a display element layer on the flexible base material layer, and utilizing a fluorine-containing corrosive gas to etch and gasify the silicon sacrificial layer to cause the flexible base material layer to separate from the rigid base material layer. A substrate for manufacturing a flexible display includes a rigid base material layer, a silicon sacrificial layer disposed on the rigid base material layer, an adhesive layer disposed on the silicon sacrificial layer, a flexible base material layer disposed on the adhesive layer, and a display element layer disposed on flexible base material layer.

Owner:HISENSE VISUAL TECH CO LTD

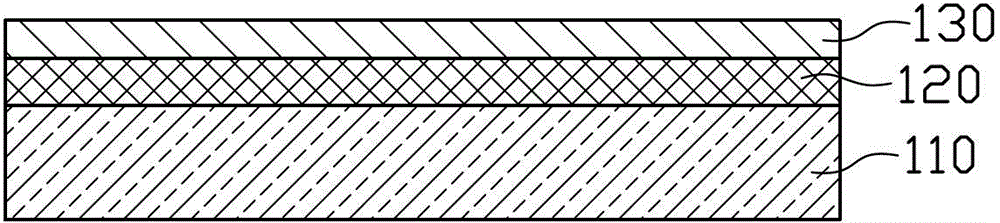

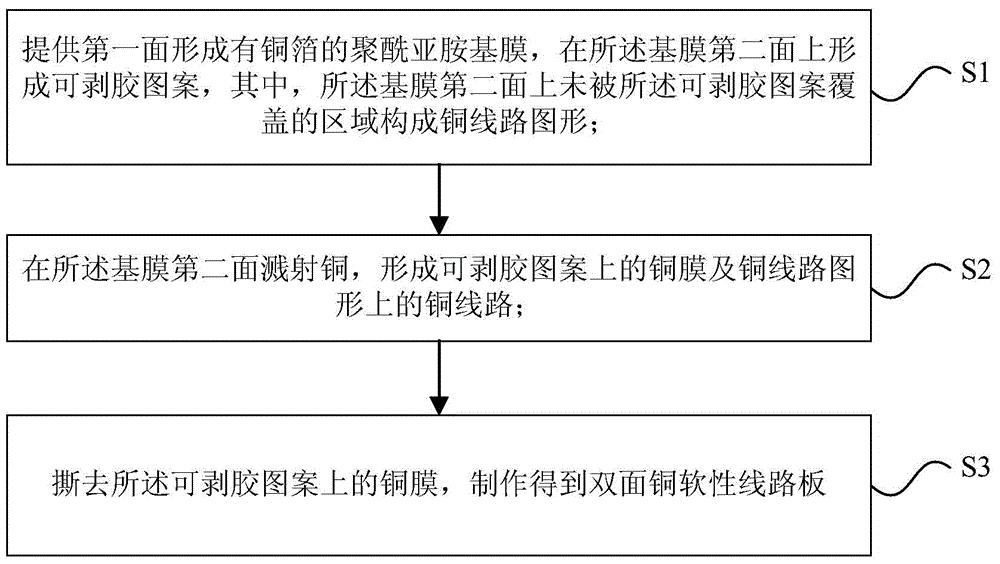

Manufacturing method for two-sided copper flexible circuit board

ActiveCN104159408ATear off easyGood removal effectConductive material mechanical removalFlexible circuitsCopper foil

The invention provides a manufacturing method for a two-sided copper flexible circuit board. The manufacturing method at least comprises the following steps: step 1, providing a polyimide base membrane, on the first surface of which, copper foil is formed, and forming a peelable mask pattern on the second surface of the base membrane, wherein the area, which is not covered by the peelable mask pattern, on the second surface of the base membrane constitutes a copper circuit figure; step 2, sputtering copper on the second surface of the base membrane, so as to form a copper membrane on the peelable mask pattern and the copper circuit on the copper circuit figure; step 3, tearing off the copper membrane on the peelable mask pattern and manufacturing to obtain the two-sided copper flexible circuit board. The manufacturing method has the advantages as follows: the ultrathin two-sided copper flexible circuit board can be manufactured, the process is simple, the 20-30% of production cost can be reduced, the manufacturing of the copper circuit is based on an addition process, waste emission is reduced, and environmental pollution is reduced; meanwhile, the torn copper membrane can be recycled after being cleaned simply, and material waste can be reduced.

Owner:上海蓝沛信泰光电科技有限公司

Chip cutting method for increasing LED chip light extraction

ActiveCN102738313BImprove light outputImprove light extraction efficiencyFine working devicesLaser beam welding apparatusEngineeringInverted triangle

A chip cutting method for increasing LED chip light extraction is disclosed. The method comprises the following steps: using a laser to make a scratch on a right side of the chip; then, using a diamond saw blade knife to carry out saw blade along the scratch, wherein the saw blade knife is a bilaterally symmetrical isosceles inverted triangle and an included angle of a knife side surface and a horizontal line is 30-60 DEG; adjusting a knife height of the saw blade knife so that an epitaxial layer is just sawed through; carrying out overturn and inverted membrane on the chip after the saw blade is finished; using a splinter knife to carry out splinter on a back side of the chip along the laser scratch. According to the invention, through a saw blade technology, an epitaxial layer edge of the chip, which is about 10micron, is sawed into an inclined platform. A chip light extraction rate can be increased by more than 20%. Simultaneously, chip appearance is improved. A technology operation is simple and is easy to be realized.

Owner:JIANGSU ETERN +1

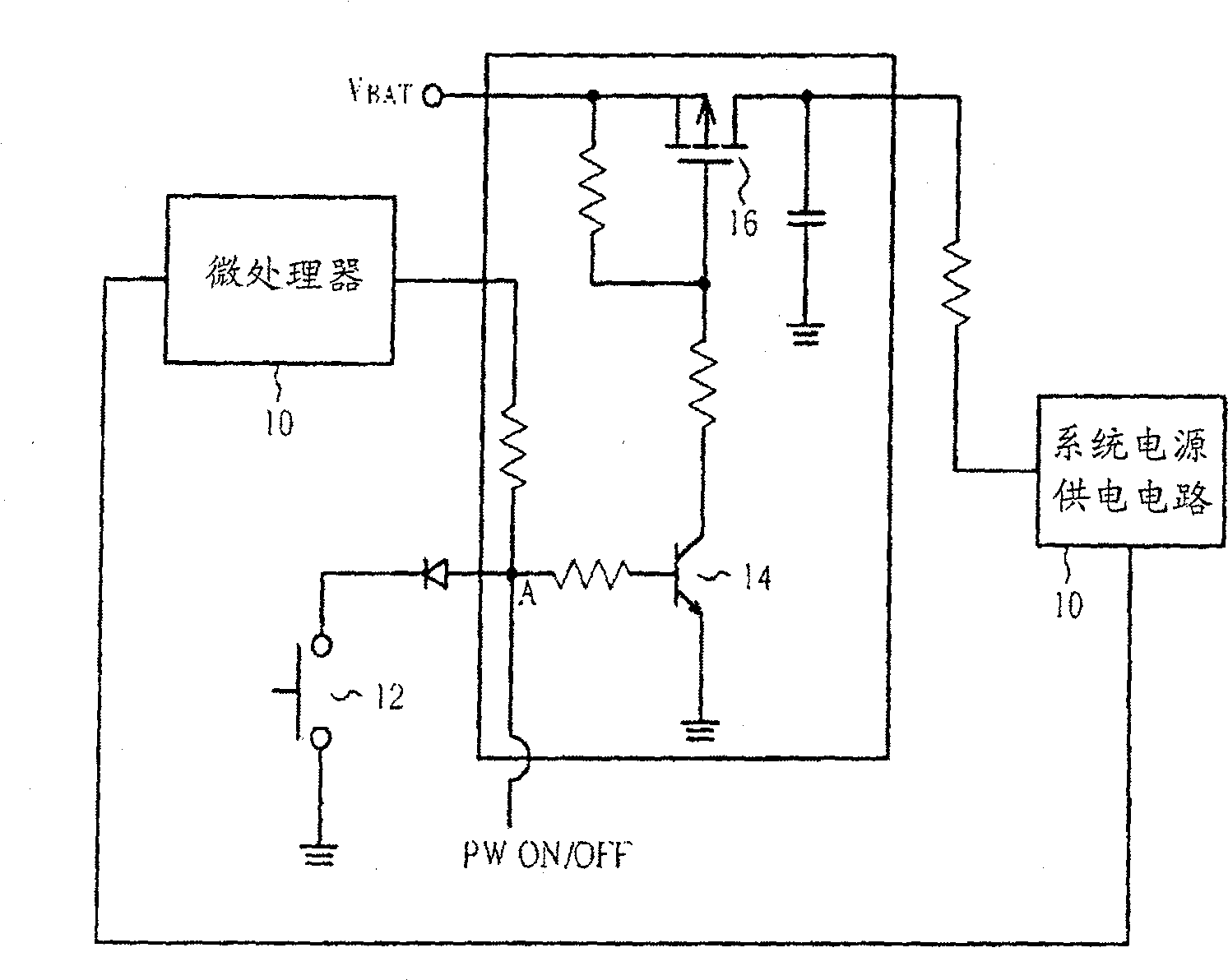

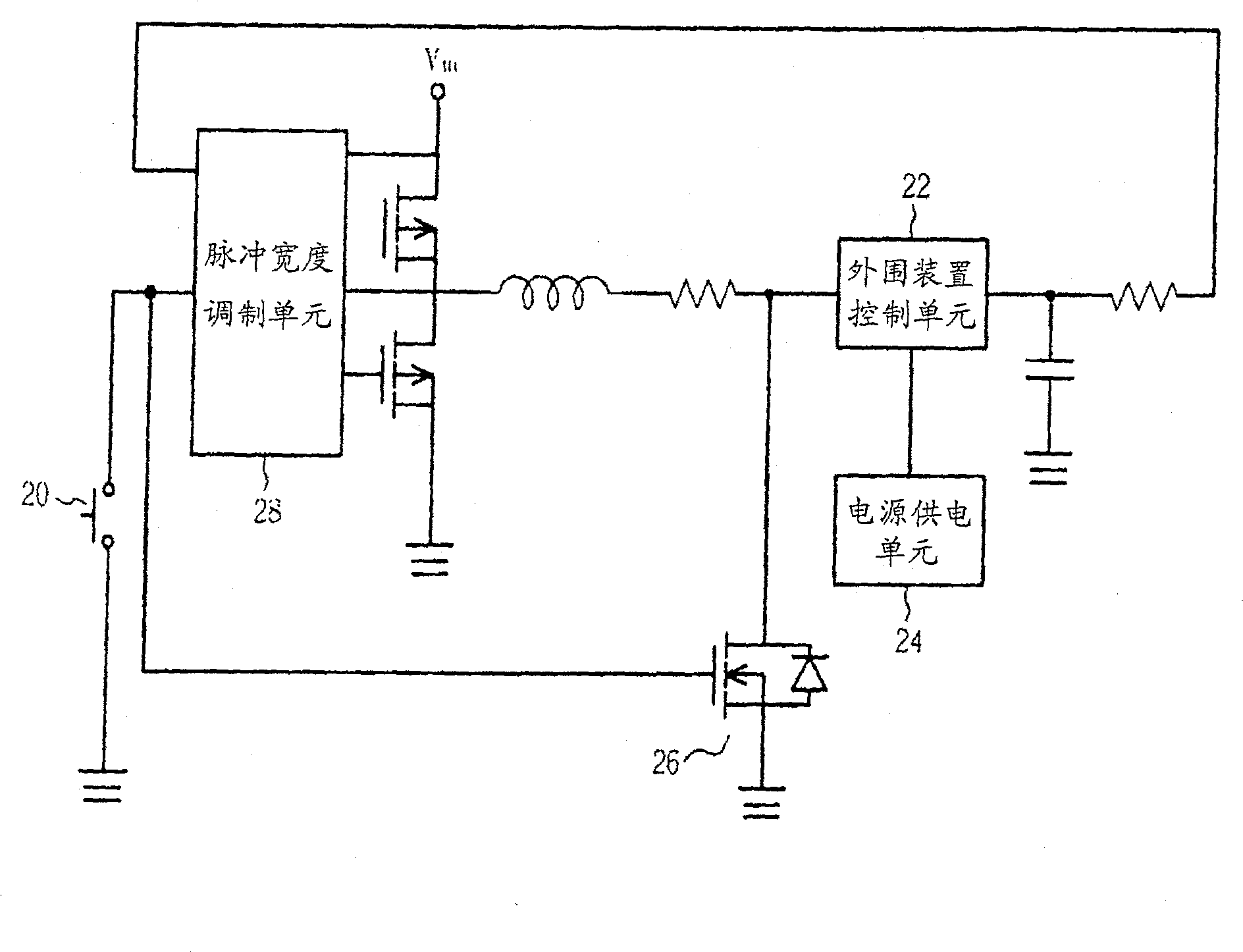

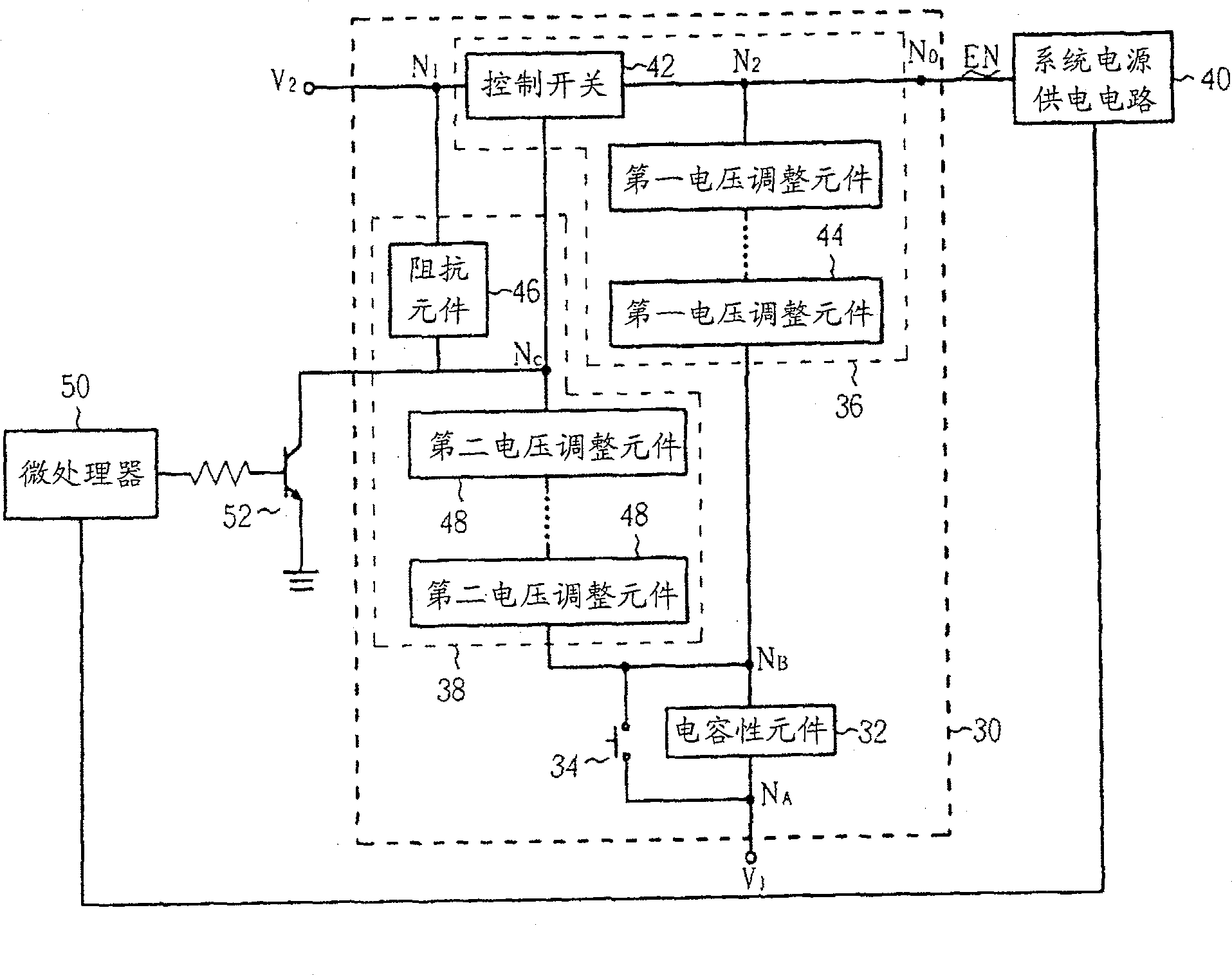

System restarting circuit and its system restarting method

InactiveCN100543646CDoes not affect electrical characteristicsWon't wasteData resettingControl circuitElectrical current

Owner:RRT TECH LTD

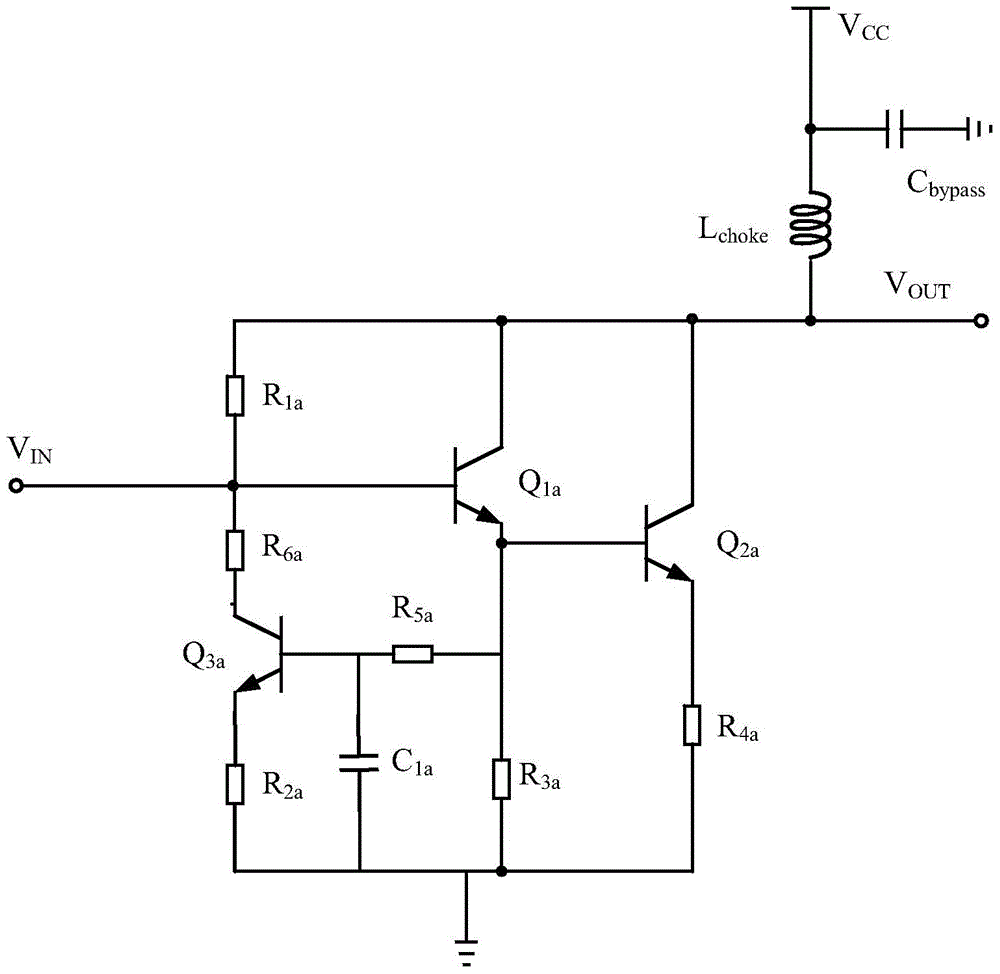

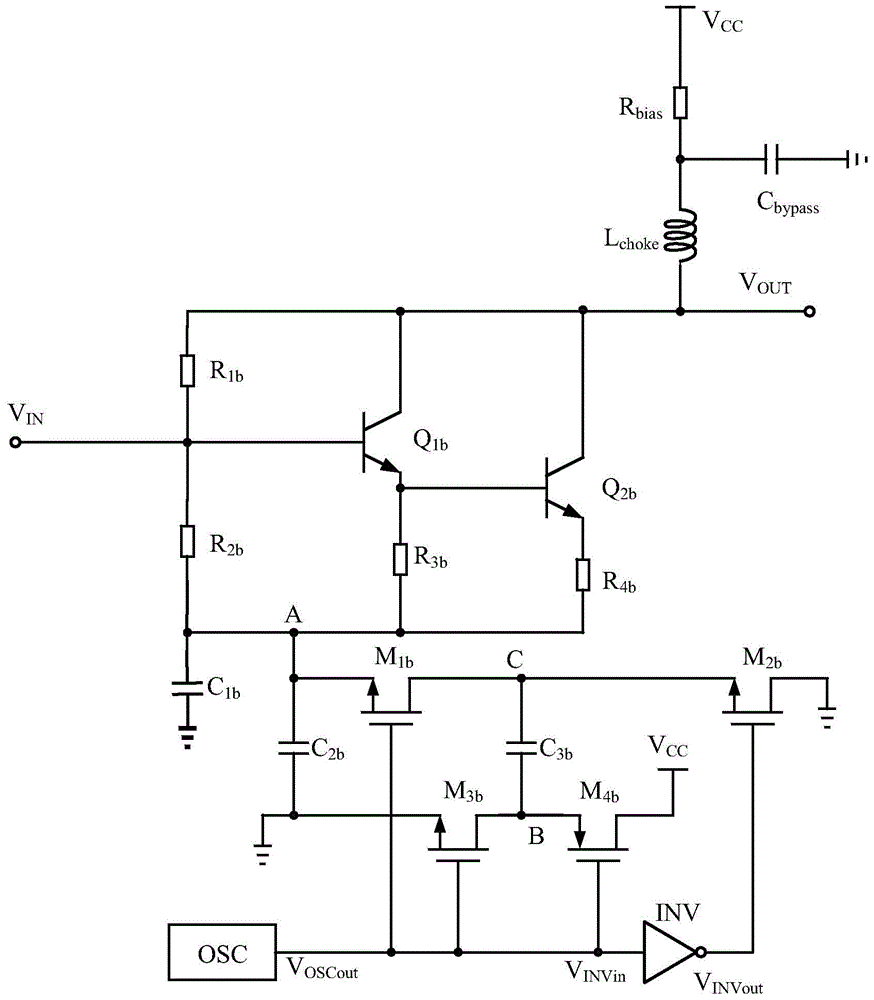

Low Voltage Darlington Amplifier

ActiveCN104113291BIncrease potential differenceReduce the power supply voltageAmplifier with semiconductor-devices/discharge-tubesAudio power amplifierMicrowave

Owner:NO 24 RES INST OF CETC

Chip scale package diode component with ultra-low forward voltage and manufacture method

InactiveCN107622956ALower internal resistanceForward voltage dropSemiconductor/solid-state device detailsSolid-state devicesCrystalliteEngineering

The present invention discloses a chip scale package diode component with an ultra-low forward voltage and a manufacture method. According to the diode component, all regions except a second electrodeare directly adopted as a first electrode, and / or the front surface and back surface of the first electrode are penetrated through perforation, and are conducting, and then cutting is performed, so that a chip scale package diode component finished product with a smaller size can be obtained. Since the first electrode is not required to be conducting through an epitaxial layer or a diffusion layer, and therefore, internal resistance can be avoided, a forward voltage can be lowered. With the manufacture method adopted, a manufacture process is simplified, quality can be improved, costs can bereduced, and the diode component can be lighter, shorter and smaller.

Owner:FORMOSA MICROSEMI

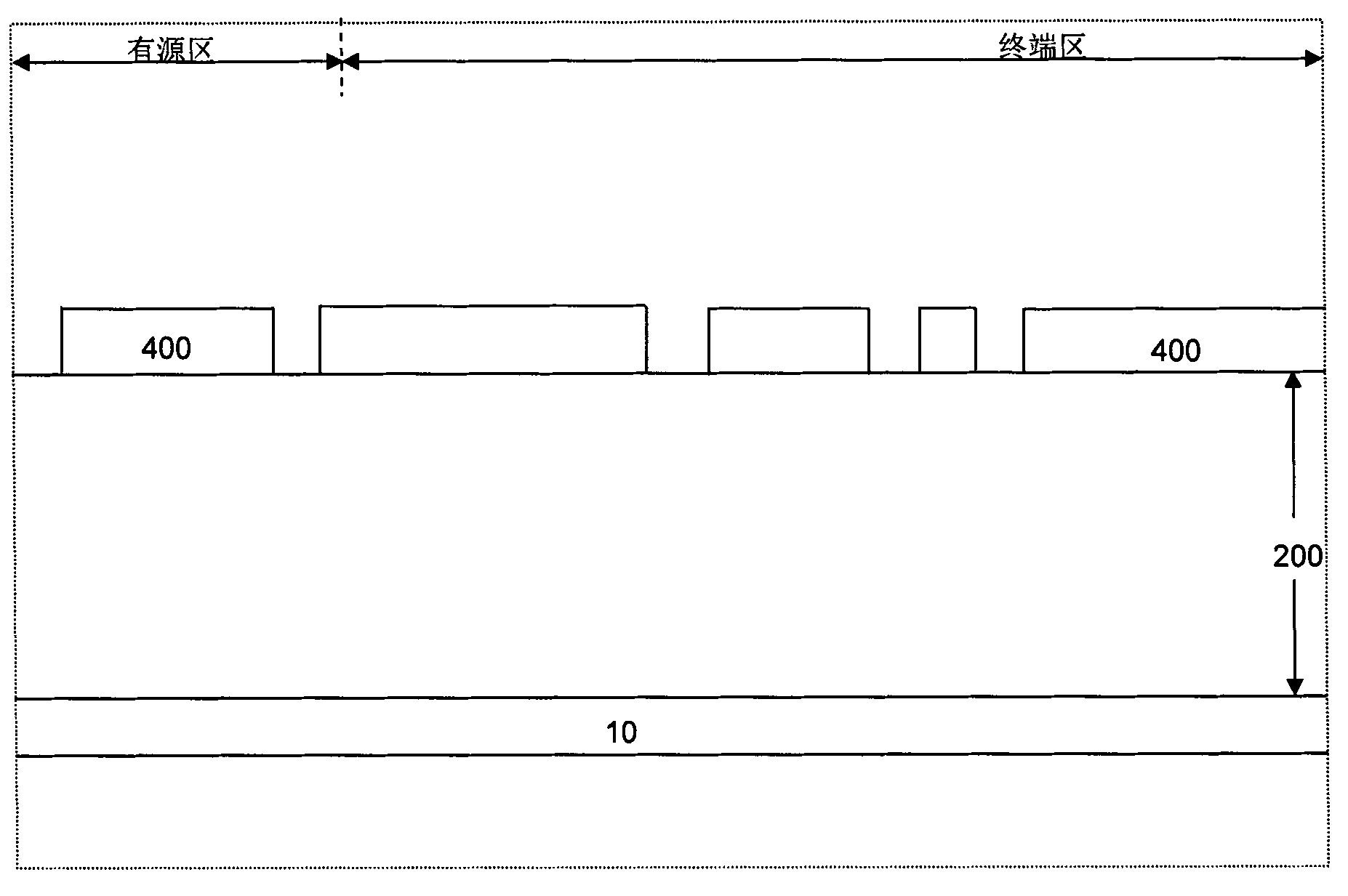

A method for preparing trench semiconductor discrete devices

InactiveCN103219241BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantEngineering

Owner:立新半导体有限公司

A kind of preparation method of trench semiconductor power device

InactiveCN103187282BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantEngineering

The invention discloses a preparation method of a trench semiconductor power device. The preparation method of the trench semiconductor power device includes a first step of injecting dopant into an epitaxial layer arranged on a substrate for two times to form P-type base regions and N-type base regions, and conducting corrosion on the epitaxial layer to form a plurality of grid trenches; a second step of depositing interlayer mediums on the epitaxial layer, conducting the corrosion on the interlayer mediums through a contact hole mask, conducting the corrosion on the interlayer mediums and the surface of the epitaxial layer through a contact hole mask to form contact trenches, and conducting metal plugging filling on the contact trenches; and a third step of depositing a metal layer on the surface of the discrete device, conducting metal corrosion through a metal mask and forming a metal substrate layer and a connecting wire. The preparation method of the trench semiconductor power device eliminates preparation procedures of a base region mask and a source region mask, and therefore the manufacturing cost of the power device is greatly reduced. In addition, original electrical characteristics of the power device cannot be influenced. The cost-performance ratio of the power device is improved. The performance, the quality and the reliability of the trench semiconductor power device are not influenced.

Owner:立新半导体有限公司

High light extraction efficiency Gan-based LED transparent electrode structure and preparation method

ActiveCN104659180BNo risk of injuryAvoid reflection lossSemiconductor devicesIndium tin oxideLight-emitting diode

The invention relates to a transparent electrode structure and a preparation method thereof, particularly relates to a transparent electrode structure of a GaN-based LED (Light Emitting Diode) with high light extraction efficiency and a preparation method thereof and belongs to the technical field of LED semiconductor devices. According to the technical scheme provided by the invention, the transparent electrode structure comprises a GaN substrate, wherein the GaN substrate is provided with a nano column layer and an ITO (Indium Tin Oxide) layer covering the nano column layer; the nano column layer comprises a plurality of nano columns; the ITO layer covers on the nano columns and column disconnecting holes at the two sides of the nano columns are filled with the ITO layer, so that the ITO layer and the GaN substrate are contacted. The transparent electrode structure has the advantages that the light extraction efficiency of the GaN-based positive LED can be obviously improved, the process operation is convenient, the cost is low, the application range is wide, and the safe and reliable effects are achieved.

Owner:JIANGSU XINGUANGLIAN TECH +1

A kind of preparation method of trench semiconductor power discrete device

InactiveCN103187281BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantP type doping

Owner:立新半导体有限公司

A method for preparing trench semiconductor power discrete devices

InactiveCN103187291BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDielectricP type doping

The invention discloses a method of preparing a trench semiconductor power discrete device. The method comprises the following steps of firstly injecting P-type doping agents into an epitaxial layer on a substrate through a trench mask to form P-type base regions, and then eroding the epitaxial layer to form a plurality of grid trenches; injecting N-type doping agents into side walls of the tops of the trenches to form N-type source regions; then, settlinginterlayer dielectric on the surface of the epitaxial layer, eroding the interlayer dielectric and the surface of the epitaxial layer to form contact trenches by means of a contact hole mask, and filling the contact trenches with metal plugs; and finally, settling a metal layer on the upper surface of the device, and conducting metal erosion through a metal mask to form a metal cushion layer and a connection line. By means of the preparing method, preparing processes of a base-region mask and a source-region mask are omitted, and therefore manufacturing cost of the device is greatly lowered; and meanwhile, original electrical characteristics of the device is not influenced, and therefore the price performance ratio of the device is increased.

Owner:立新半导体有限公司

A kind of graphene carbon nanotube composite film and its preparation method and application

ActiveCN108070891BImprove conductivityImprove heat transfer performanceElectrolytic inorganic material coatingSemiconductor/solid-state device detailsComposite filmPtru catalyst

The invention provides a graphene carbon nano tube composite film and a preparation method and application thereof. The preparation method comprises the following steps that S1, a substrate is provided, and the whole or at least one face of the substrate is made of a graphene catalyst; S2, electroplating is conducted, thus, a carbon nano tube is attached to the surface of the substrate, and the graphene catalyst is not fully covered with the carbon nano tube; and S3, graphene continues to grow on the face, containing the graphene catalyst, of the substrate through a chemical gas phase method,and the graphene carbon nano tube composite film is obtained. The graphene carbon nano tube composite film and the preparation method and application thereof have the characteristic of being simple intechnology, the graphene carbon nano tube composite film obtained through the non-transferring self growing technology is good in quality, and contact and attaching between the composite film and thecatalyzing substrate are good.

Owner:SHANGHAI UNIV +1

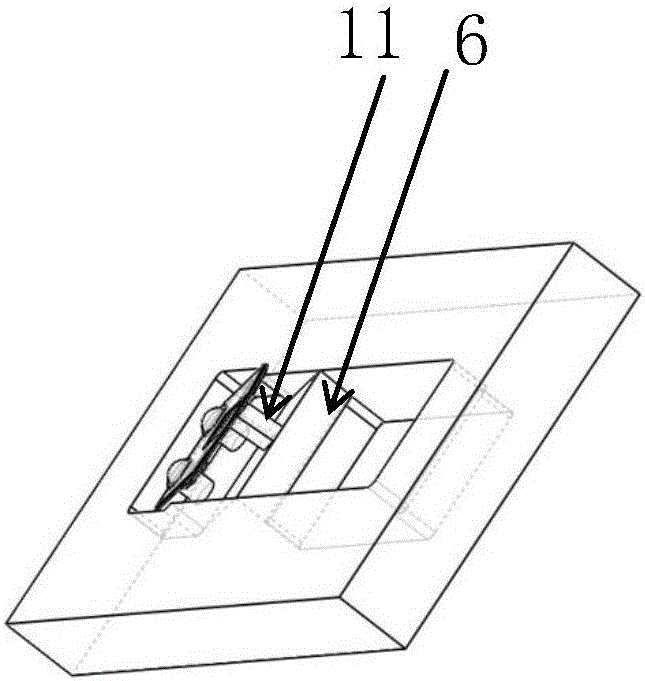

Ultrasonic transducer

InactiveCN106018566AEasy to replaceSmall sizeAnalysing solids using sonic/ultrasonic/infrasonic wavesUltrasonic imagingCantilever

The invention belongs to the field of ultrasonic imaging equipment, and discloses an ultrasonic transducer. The ultrasonic transducer comprises a base, a lower piezoelectric ceramic piece, a cushion block, a stainless steel elastic sheet support, a cantilever, a probe and upper piezoelectric ceramic pieces. A groove is formed in the upper surface of the base, and the lower piezoelectric ceramic piece is installed in the groove of the base and is connected with the cushion block; the stainless steel elastic sheet support is connected with the base through the cushion block, the stainless steel elastic sheet support and the cushion block cooperate to clamp one end of the cantilever, and the probe is fixedly installed at the other end of the cantilever; the two upper piezoelectric ceramic pieces are installed on the upper surface of the end, close to the cushion block, of the stainless steel elastic sheet support, and each upper piezoelectric ceramic piece is installed on the stainless steel elastic sheet support through a turnup electrode. The ultrasonic transducer and the cantilever are integrated in a split mode, the probe can be replaced conveniently, and high-frequency composite ultrasonic waves can be generated.

Owner:HUAZHONG UNIV OF SCI & TECH