Method of preparing groove grid-control semiconductor power device

A technology for power devices and semiconductors, which is applied in the field of preparation of trench-type gate-controlled semiconductor power discrete devices, can solve the problems of complex steps, poor breakdown voltage and reliability of semiconductor devices, and difficulty in generating

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

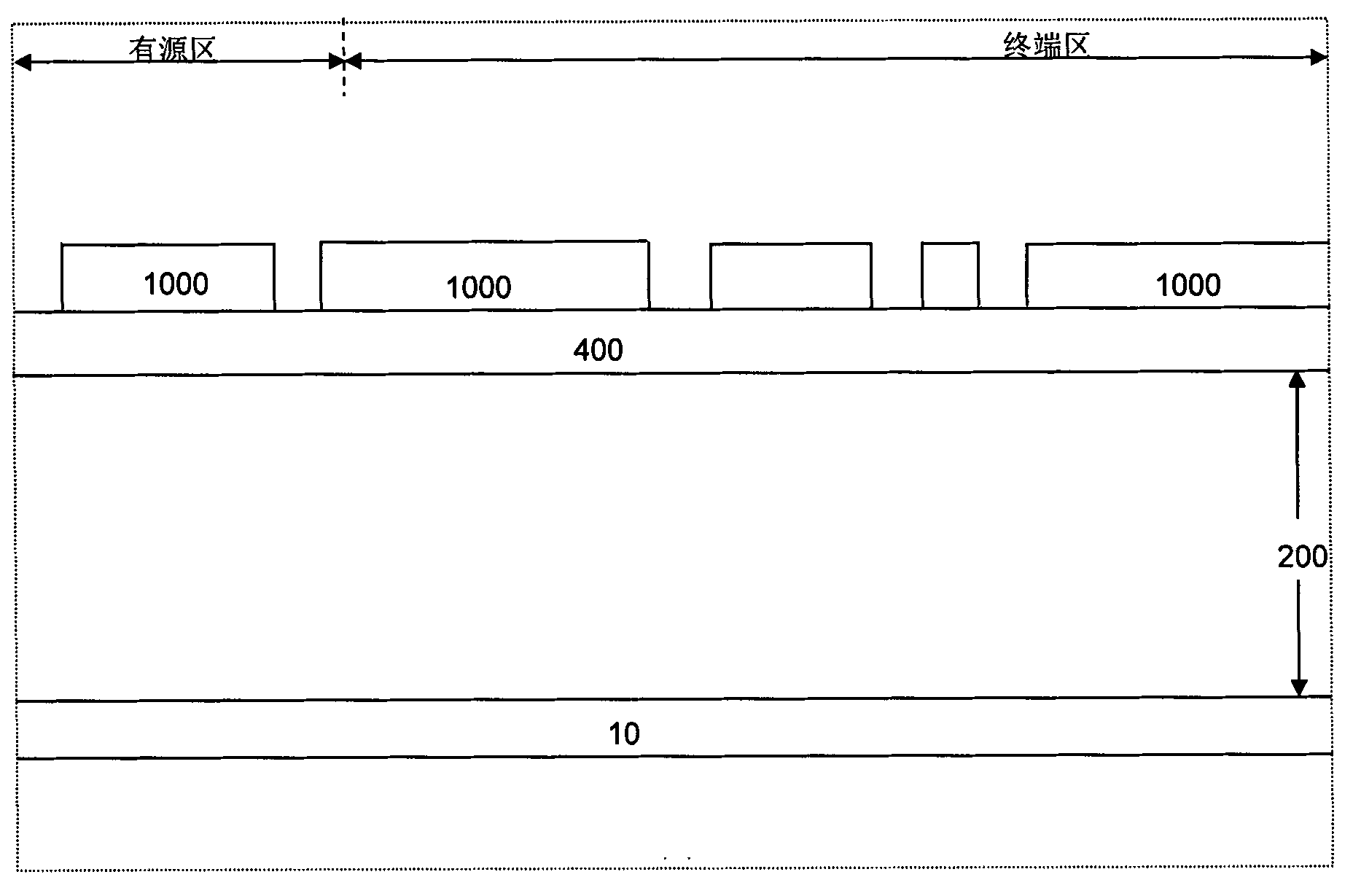

[0087] like figure 1 As shown, the epitaxial layer 200 is placed above the substrate 10. First, an oxide layer 400 (with a thickness of 0.3um to 1.5um oxide hard mask) is formed on the epitaxial layer by deposition or thermal growth, and then on the oxide layer A photoresist coating 1000 is deposited and then patterned through a trench mask to expose portions of the oxide layer.

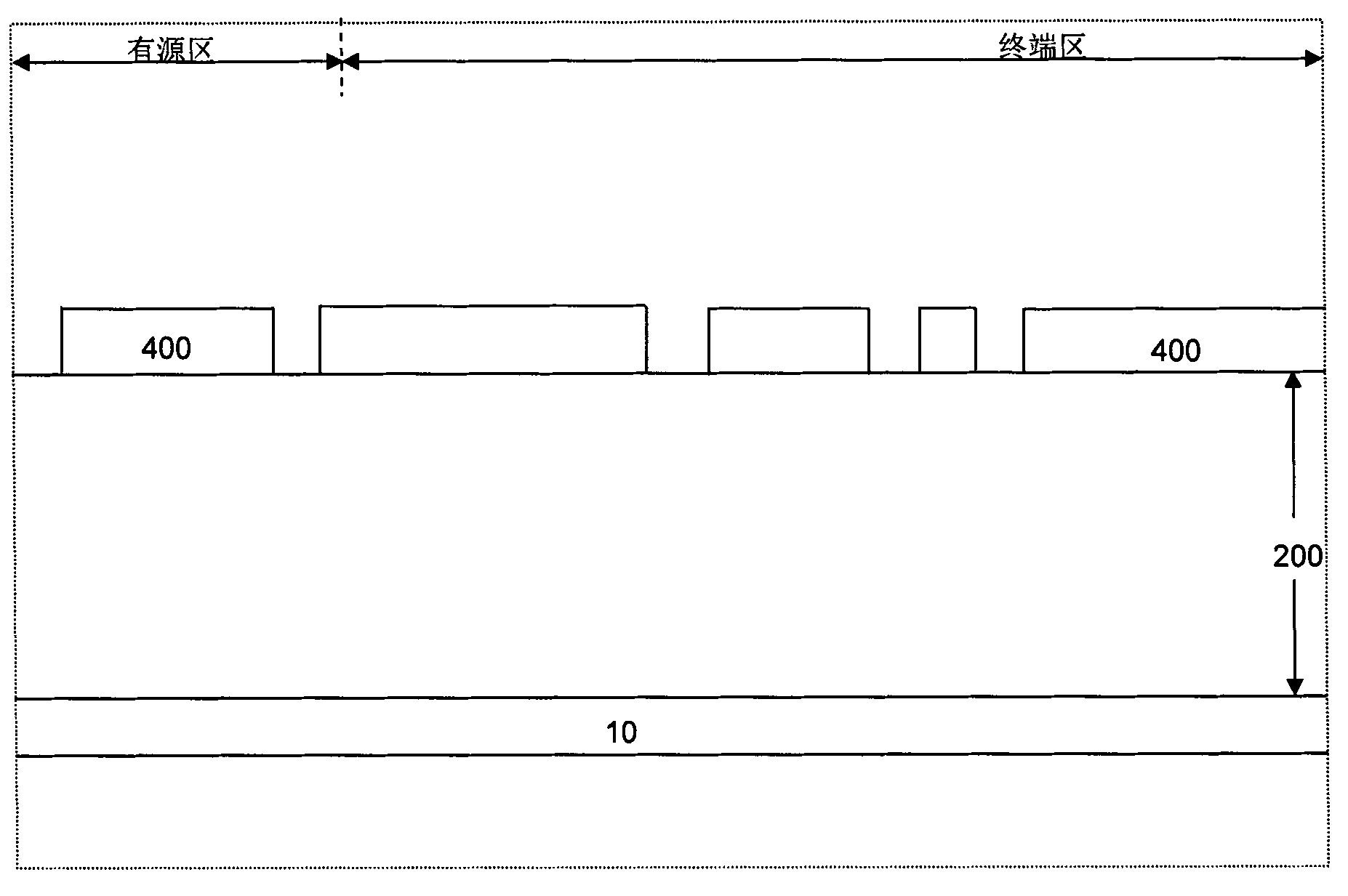

[0088] like figure 2 As shown, after dry etching the oxide layer exposed by patterning the trench mask, the epitaxial layer is exposed, and then the photolithographic coating is removed.

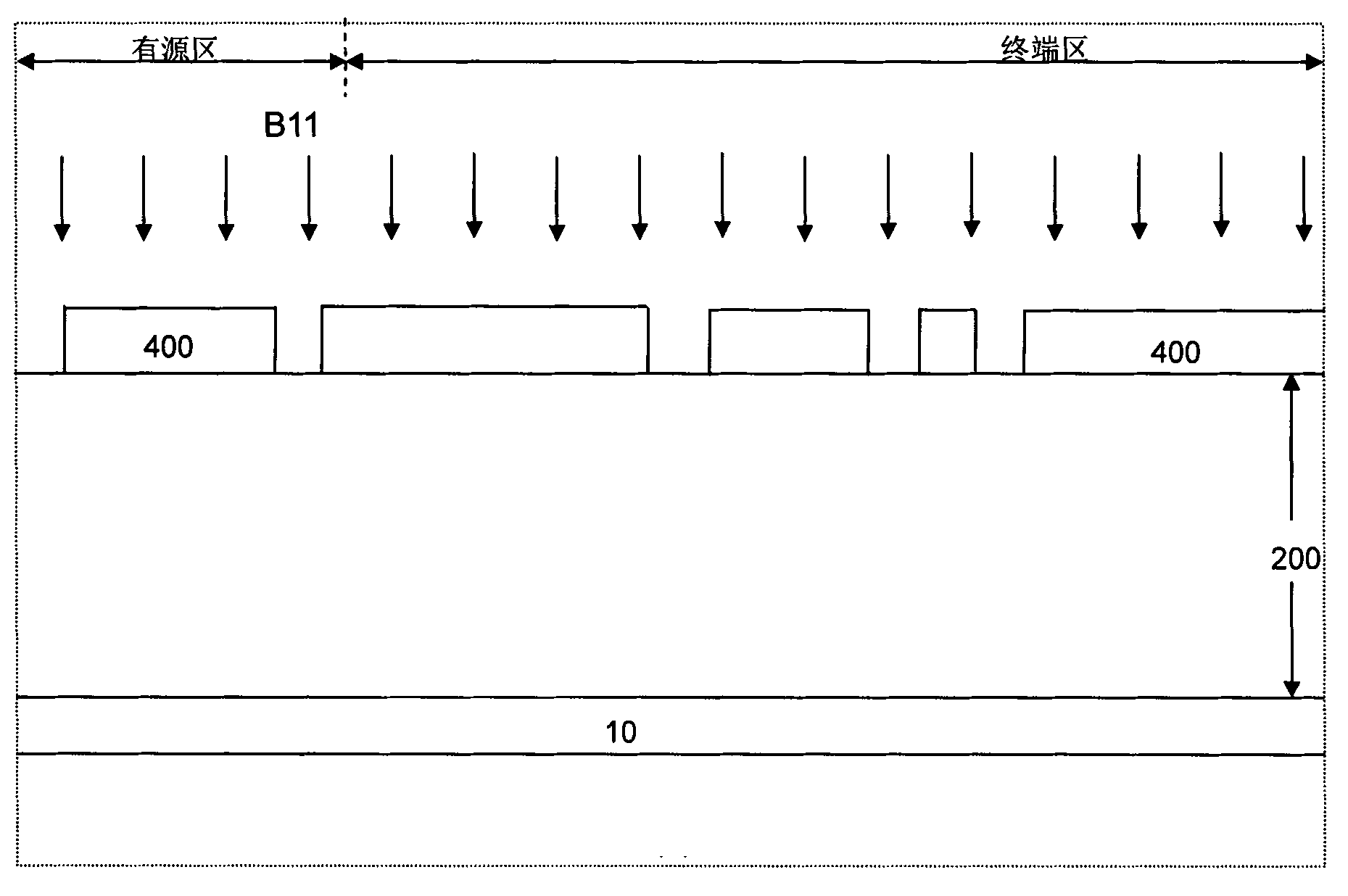

[0089] like image 3 As shown, implant P-type dopants on the surface of the silicon wafer (the dose is 2e12 / cm 3 to 2e14 / cm 3 ), the part covered by the original oxide layer 400 has not been implanted, the part not covered by the original oxide layer, the P-type dopant will be injected into the surface of the epitaxial layer to form a P-type region, and the P-type dopant can be B11 (boron boron ).

[0090] ...

Embodiment 2

[0101] It is an embodiment of the present invention.

[0102] Step and embodiment 1 are by Figure 1 to Figure 8 Same, then utilize the source region mask step to form the N-type source region 204, and the remaining steps are the same as in Embodiment 1 by Figure 10 to Figure 13 same.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More