Patents

Literature

38results about How to "Omit the preparation process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

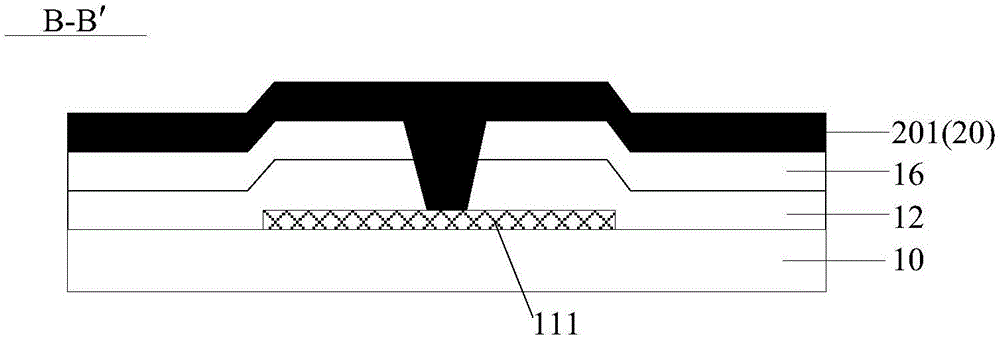

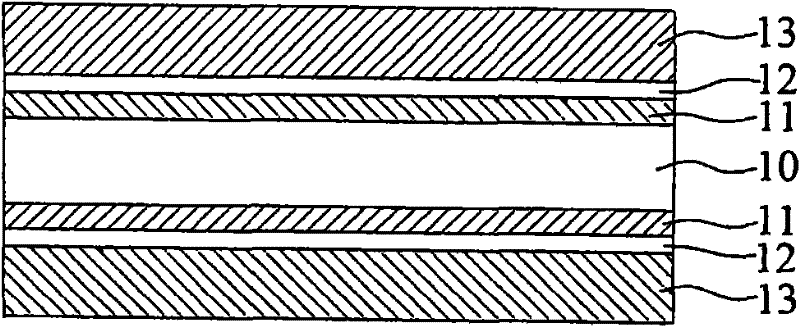

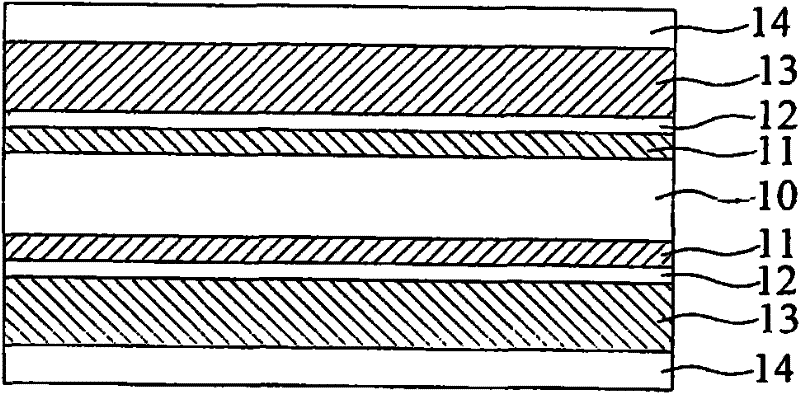

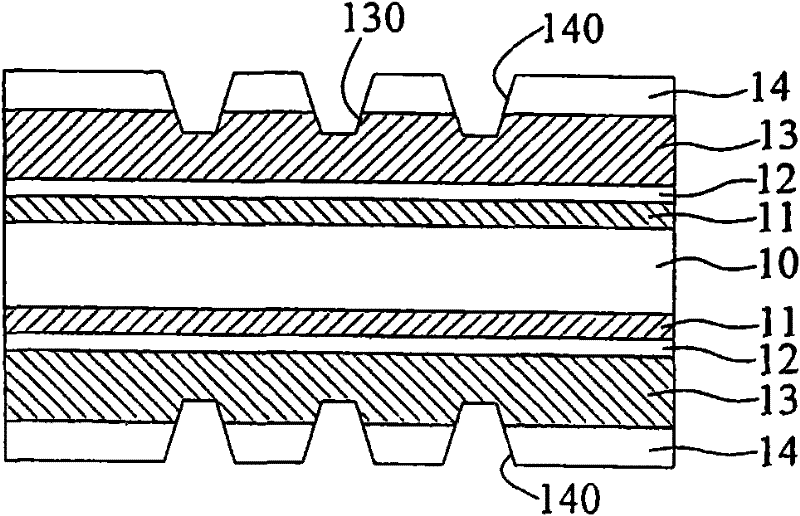

Packaging substrate as well as manufacturing method and base material thereof

ActiveCN101989592ASimple manufacturing processAvoid wastingSemiconductor/solid-state device detailsSolid-state devicesDielectric layerLine structure

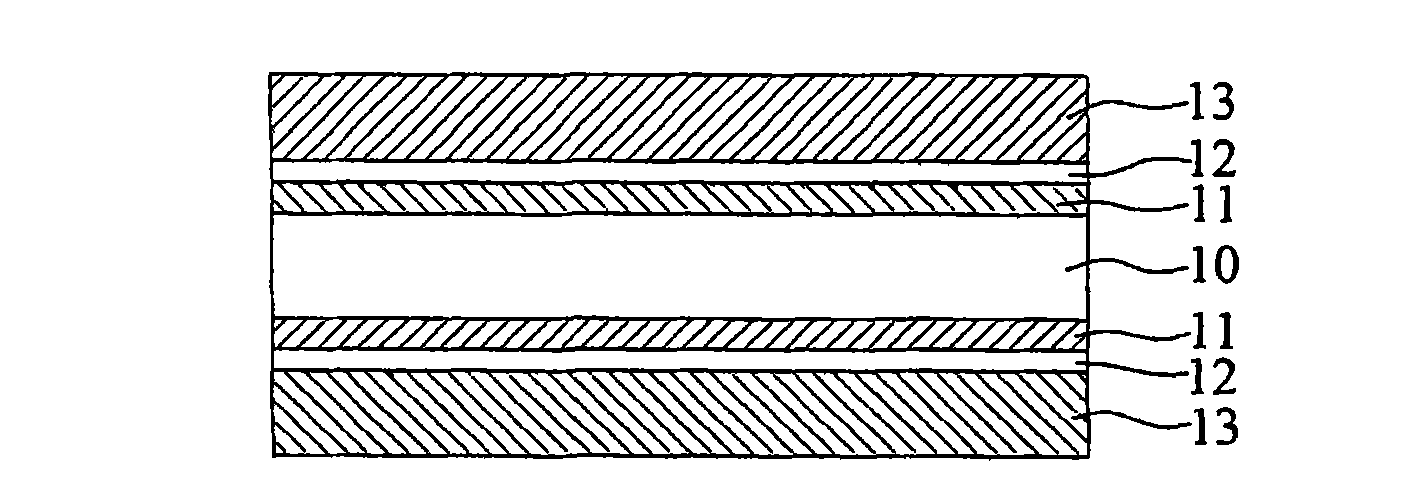

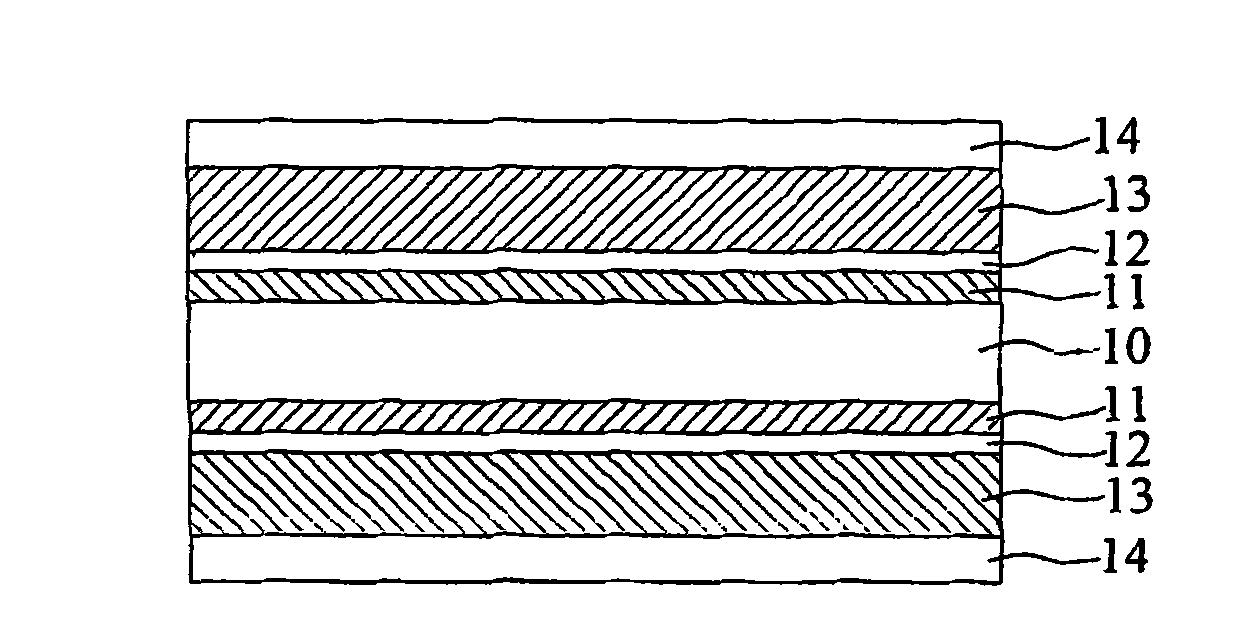

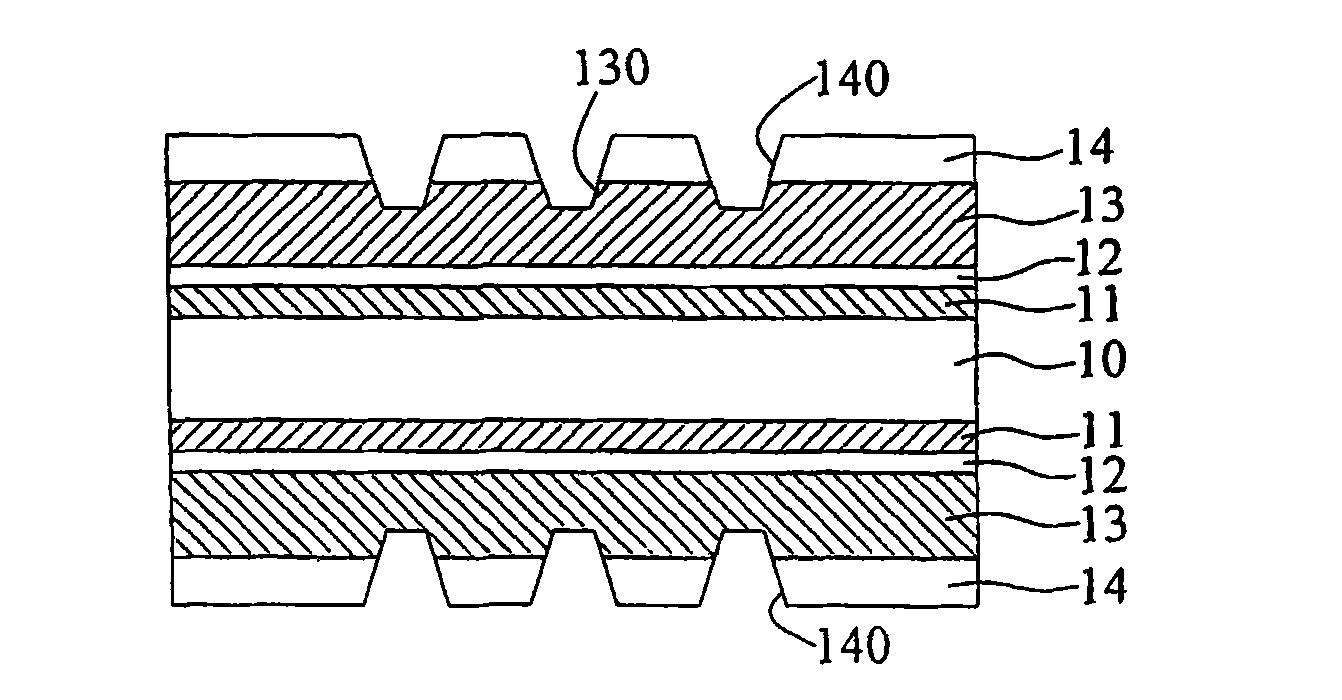

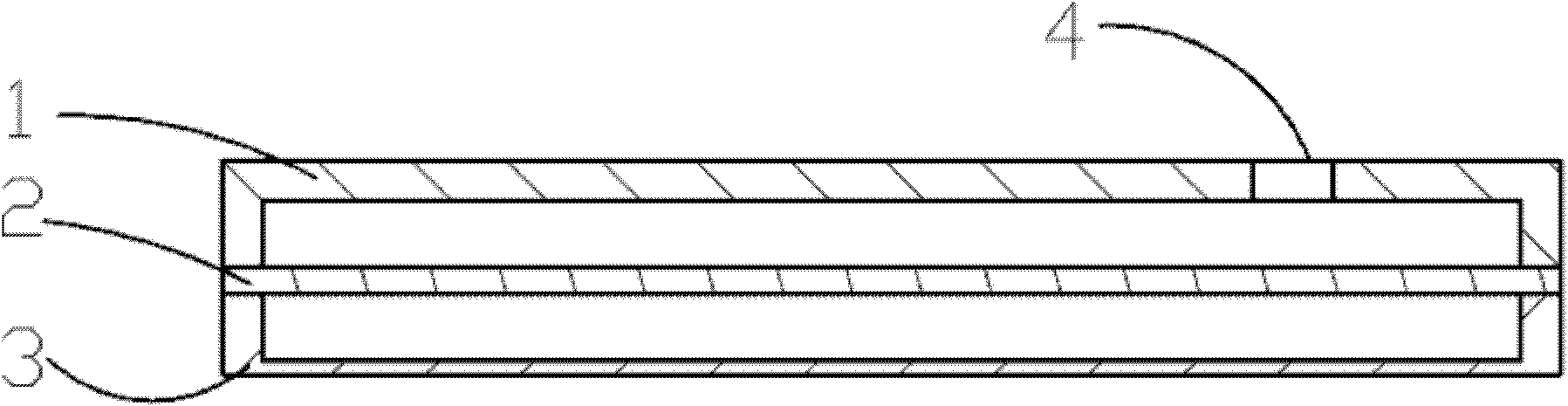

The invention discloses a packaging substrate as well as a manufacturing method and a base material thereof. The manufacturing method of the packaging substrate comprises the following steps: two metal layers are mutually laminated, and a dielectric layer is utilized to clad the two metal layers; next, layer increasing line structures are respectively formed at the two sides of the dielectric layer; and finally, the layer increasing line structures at the two sides of the dielectric layer are separated along the interface of the two metal layers so that two packaging substrates are formed. In the invention, the adhesion characteristics of the dielectric layer is utilized so that the two metal layers in the middle cannot be separated in the course of forming the layer increasing line structures in the initial stage, and the dielectric layer part around the two metal layers is cut off to successfully separate the two metal layers so that the manufacturing process is simplified, and the two metal layers in the middle can form a line layer, a metal lug or a supporting structure through the pattering manufacturing process and have no waste.

Owner:UNIMICRON TECH CORP

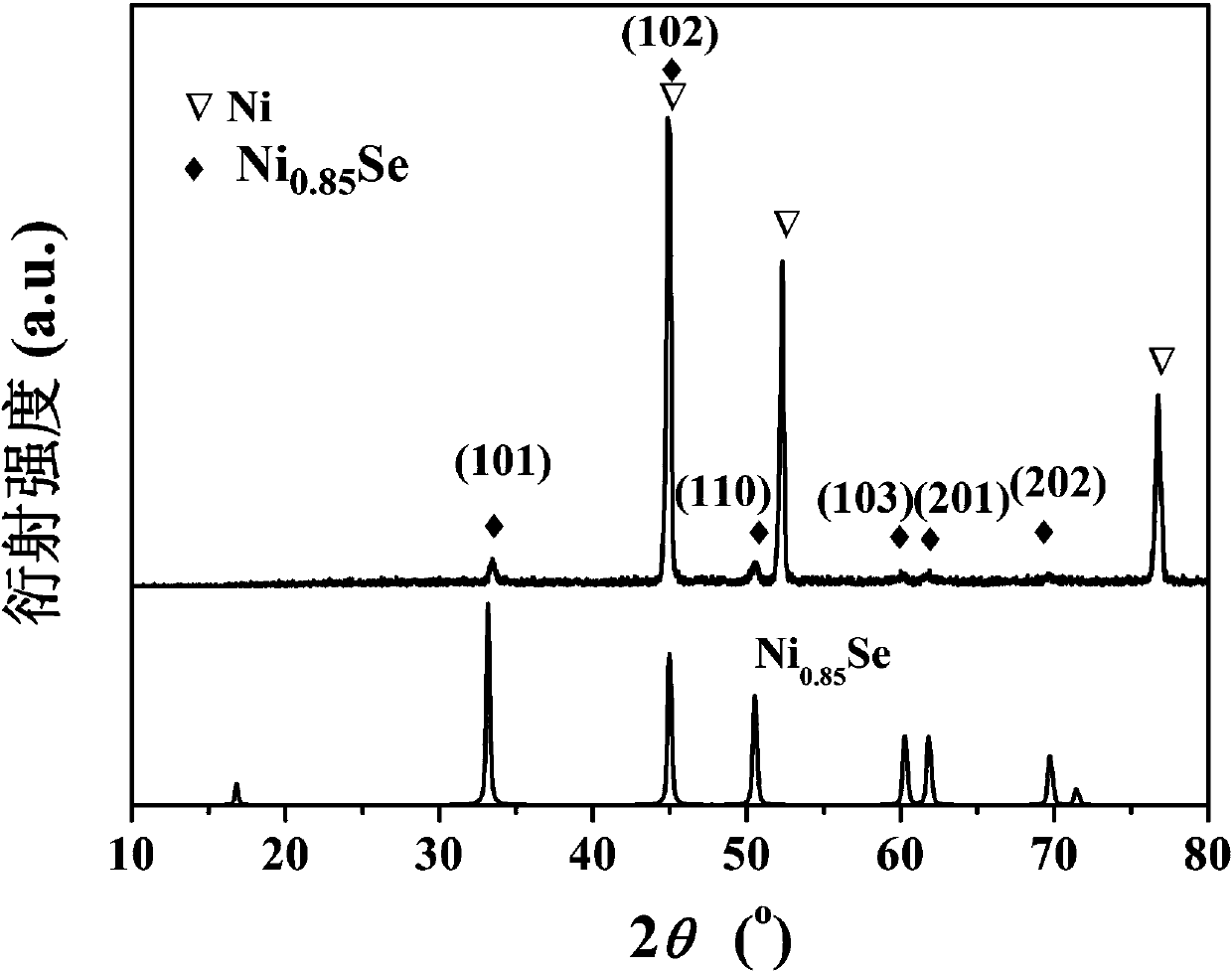

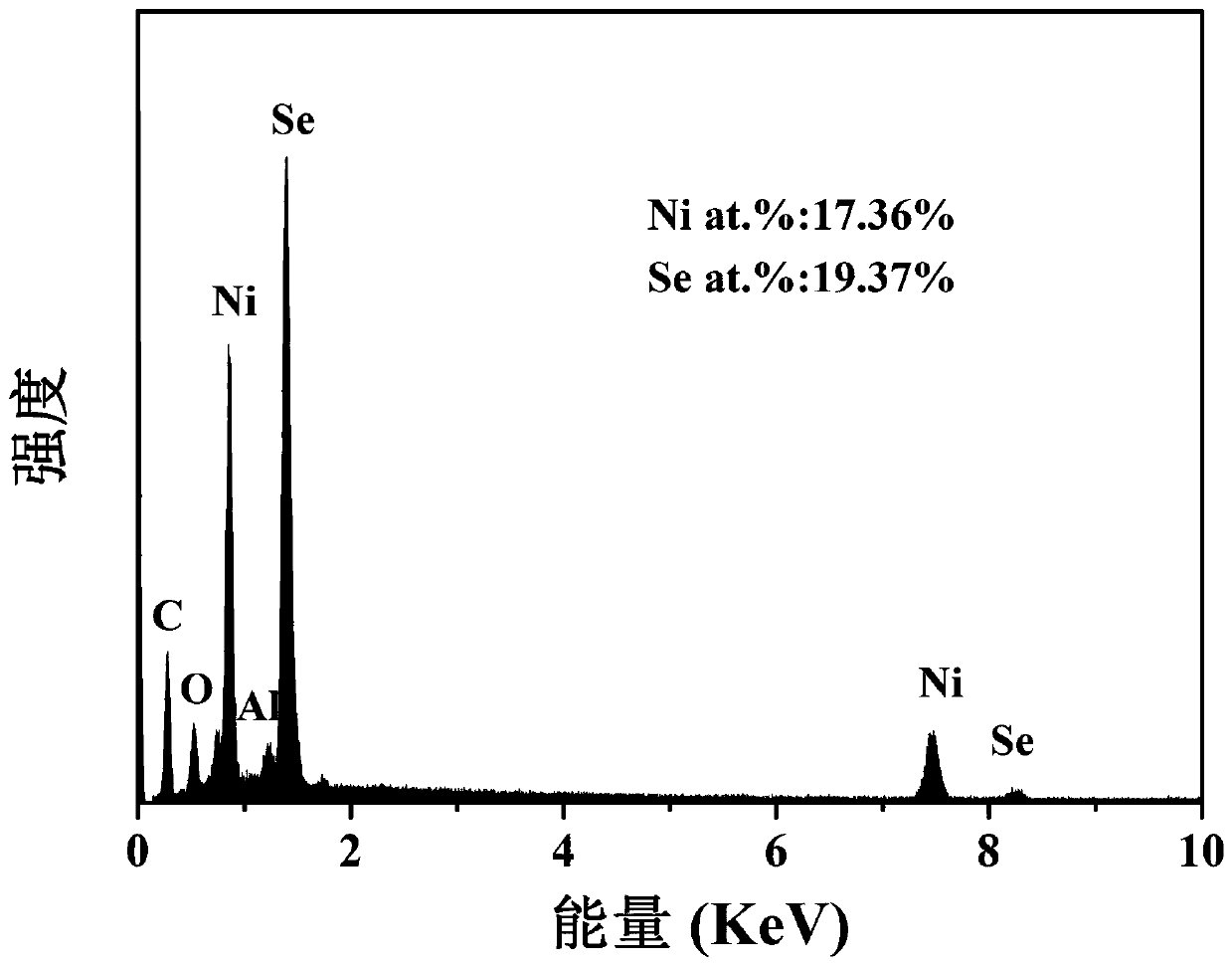

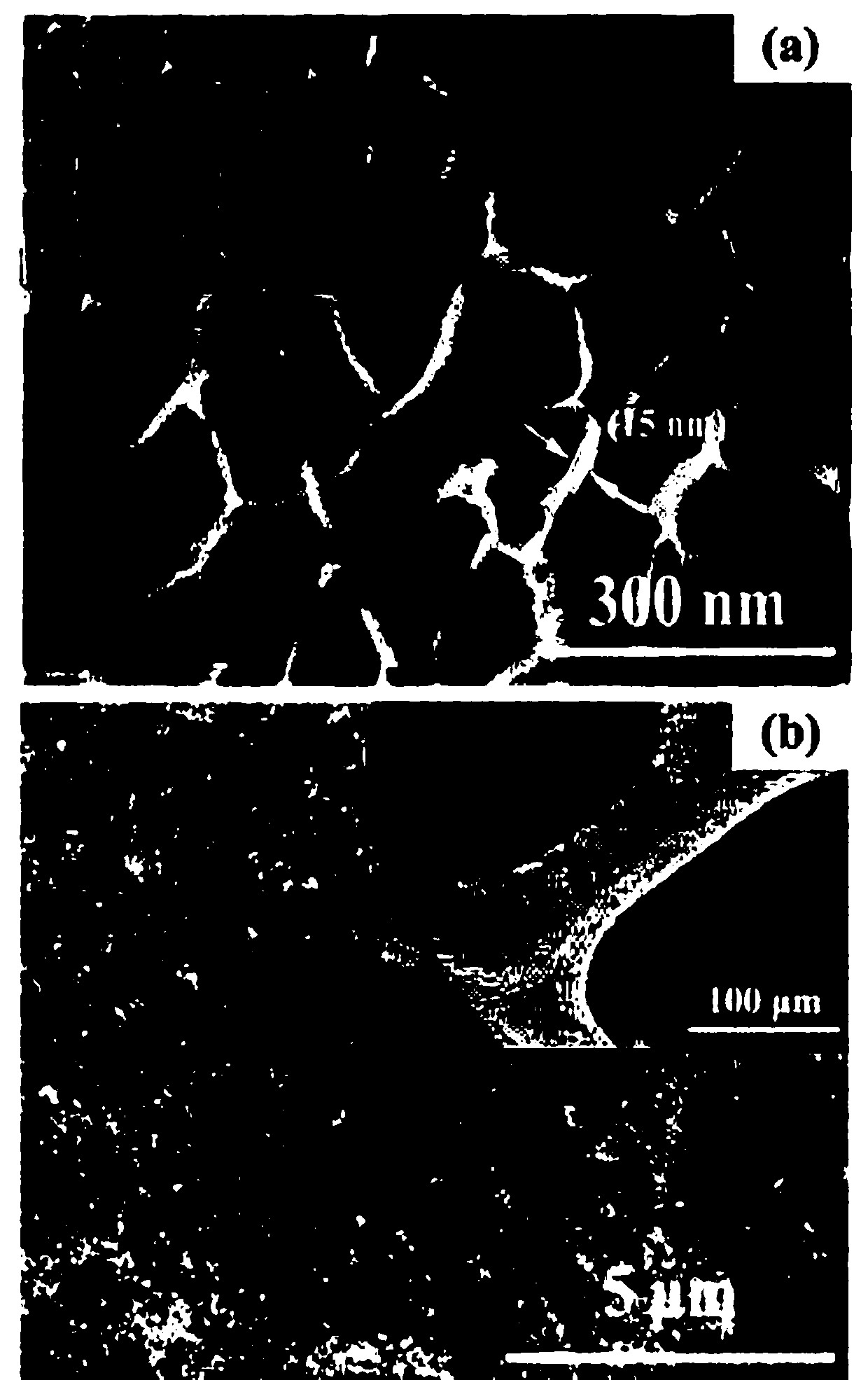

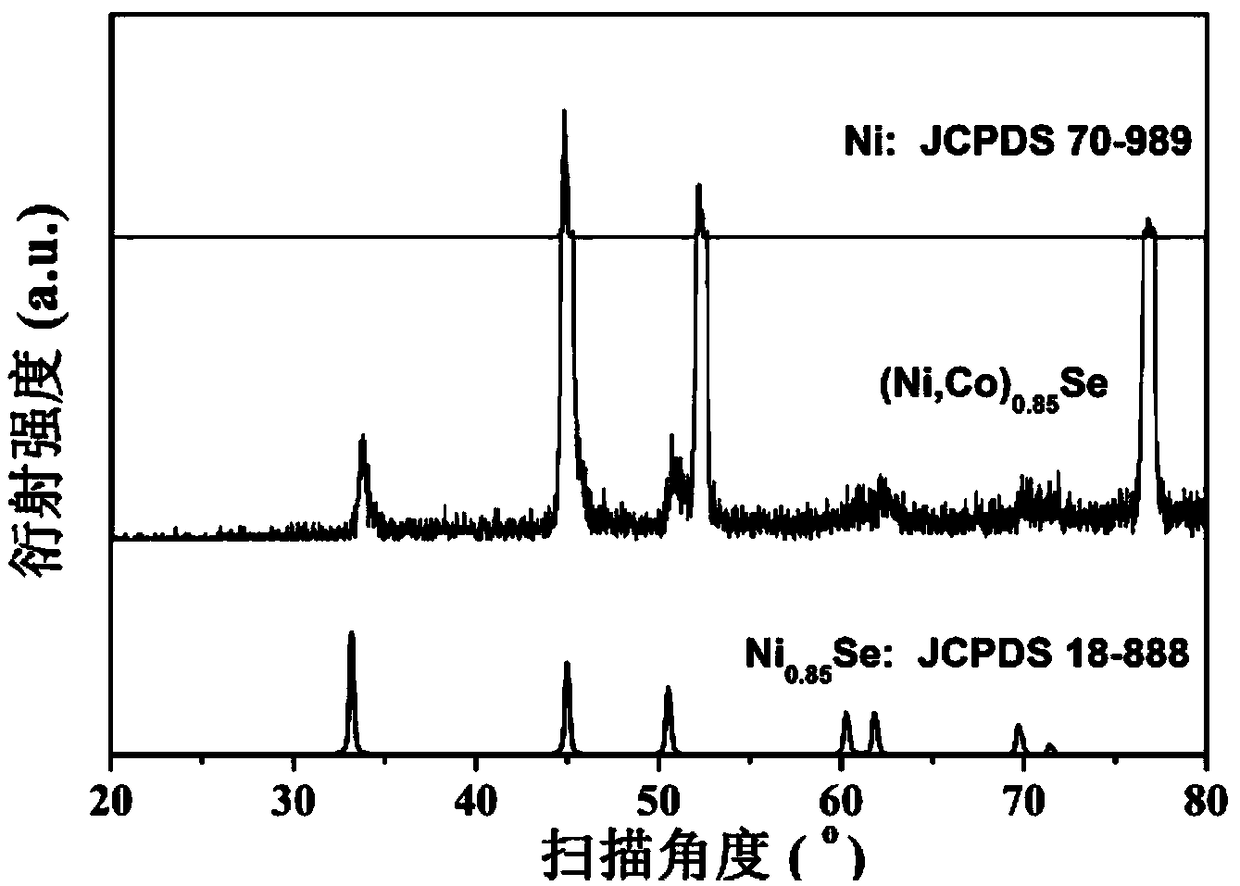

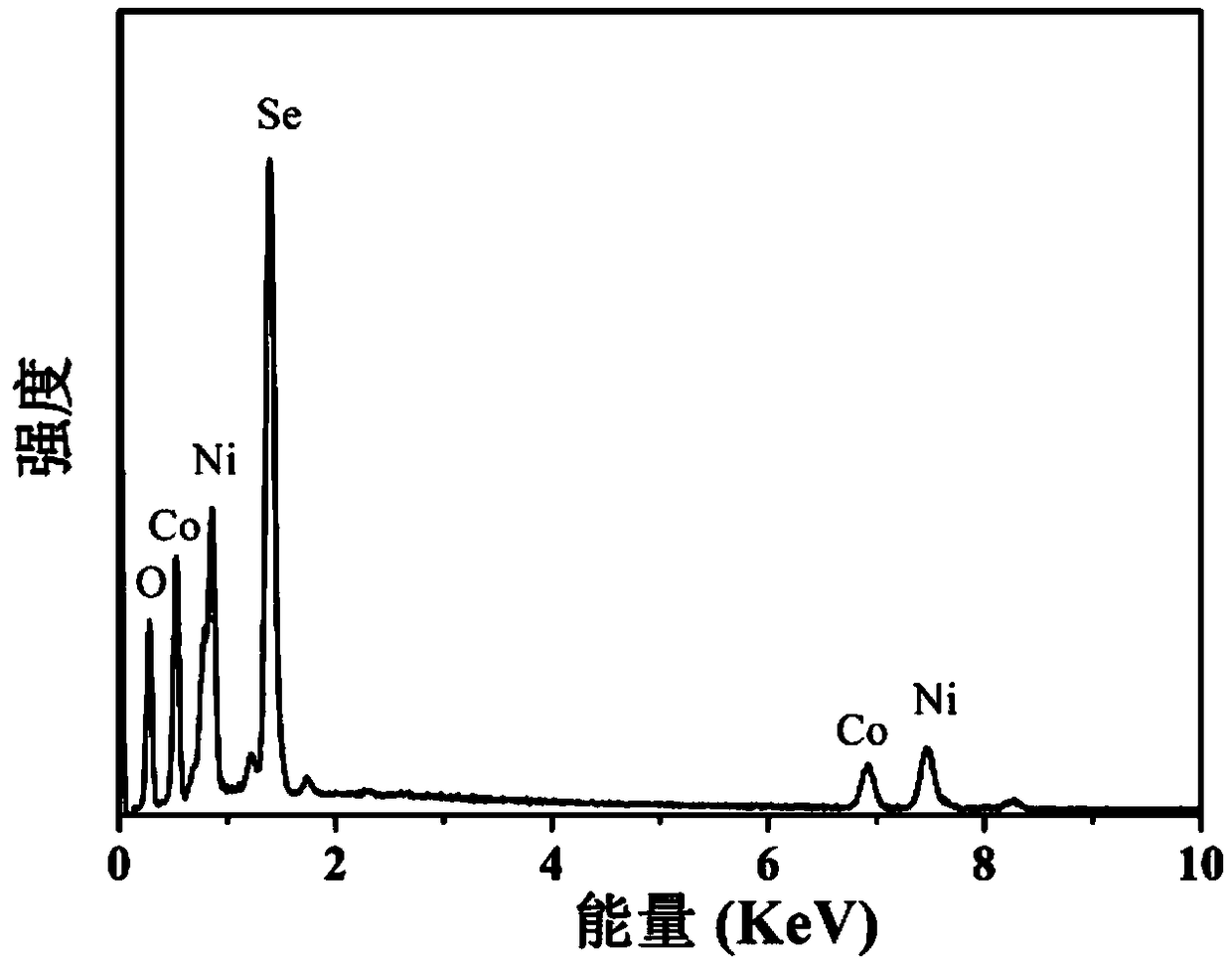

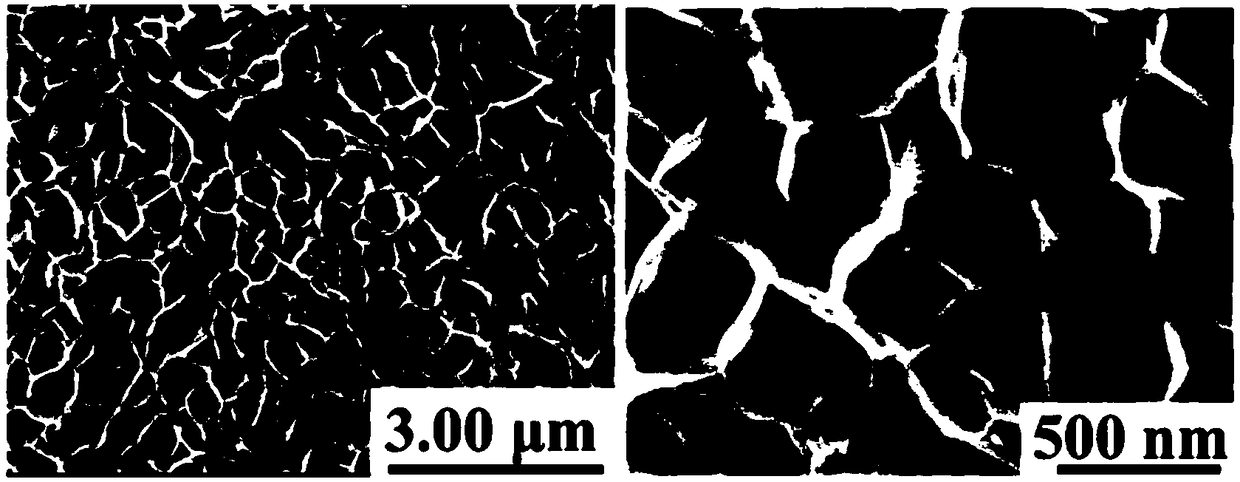

Honeycomb nickel selenide nanosheet array electrode material and preparation method thereof

InactiveCN107818873AEasy accessSave raw materialsHybrid capacitor electrodesHybrid/EDL manufactureCapacitanceReaction temperature

The invention discloses a honeycomb nickel selenide nanosheet array electrode material and a preparation method thereof, and belongs to the technical field of supercapacitor electrode material preparation. The honeycomb nickel selenide nanosheet array electrode material is prepared according the steps of mixing Se powder and an Na2SO3 solution, and preparing an Na2SeSO3 solution with certain concentration through heating and refluxing; adding the prepared Na2SeSO3 solution into a high-pressure reactor, then adding preprocessed foamed nickel into the N2SeSO3 solution, controlling the reaction temperature and time, and acquiring a honeycomb nickel selenide nanosheet array. The acquired electrode material has excellent electrochemical performance, the specific capacitance can reach up to 3105F / g when the current density is 1.0A / g, and the specific capacitance can still reach up to 1460F / g even if the current density reaches up to 10A / g. The honeycomb nickel selenide nanosheet array electrode material is prepared by adopting a one-step hydrothermal method, and is cheap in raw material, simple to operate, low in cost, high in efficiency, free of impurities and high in purity. The honeycomb nickel selenide nanosheet array electrode material is applicable to supercapacitors.

Owner:ANYANG NORMAL UNIV

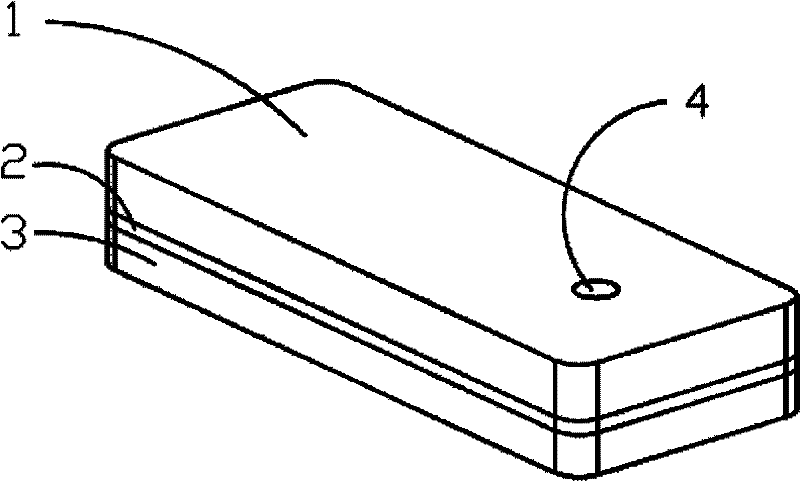

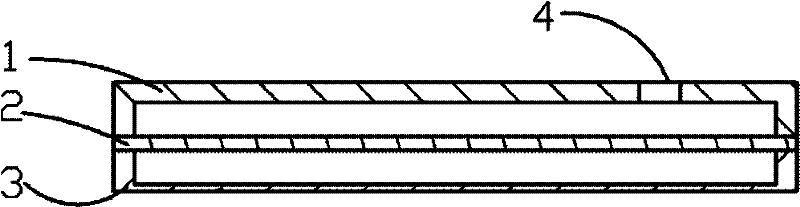

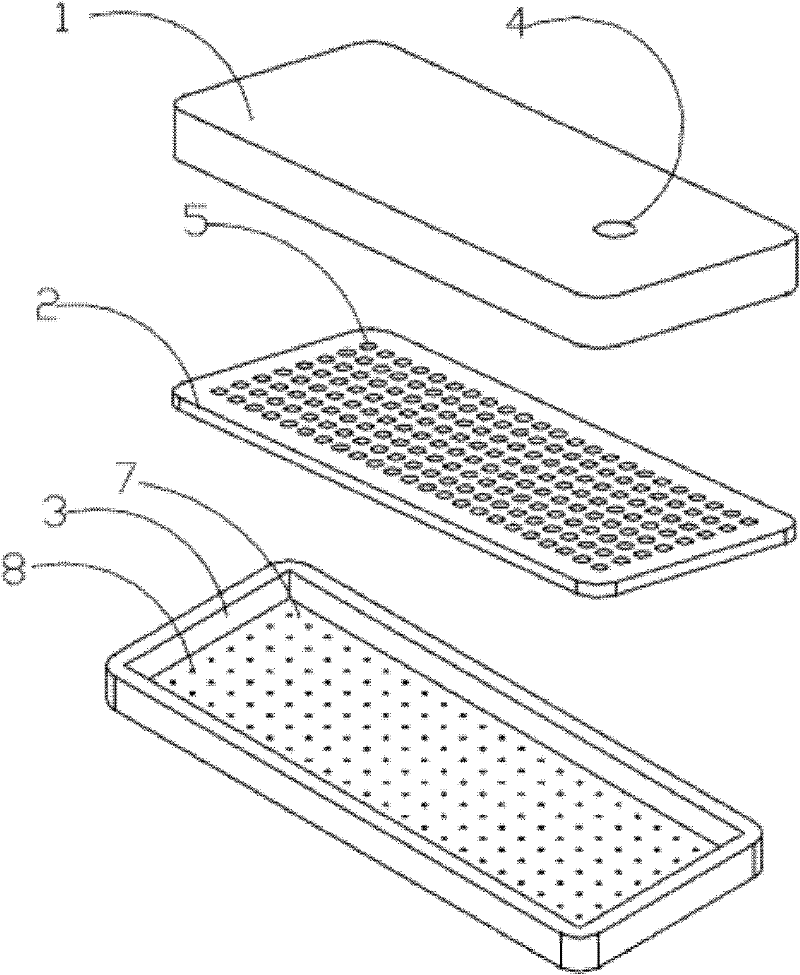

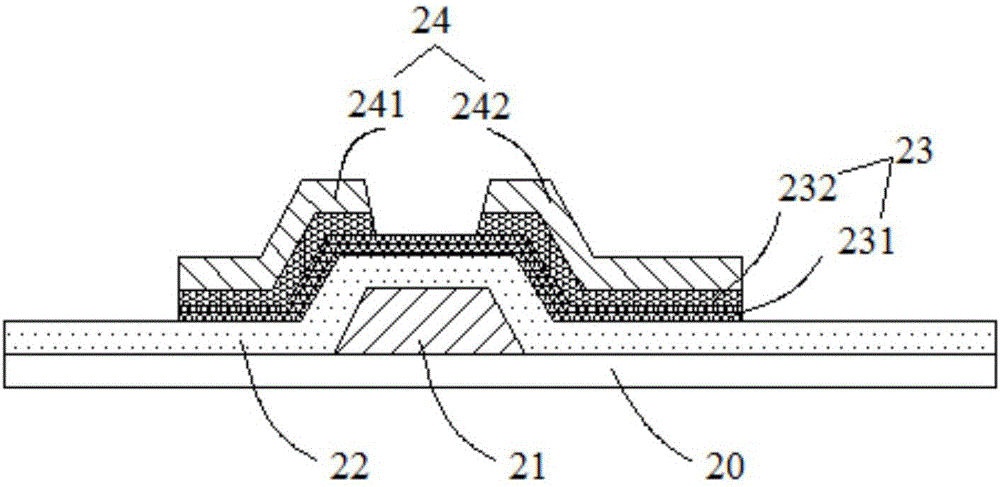

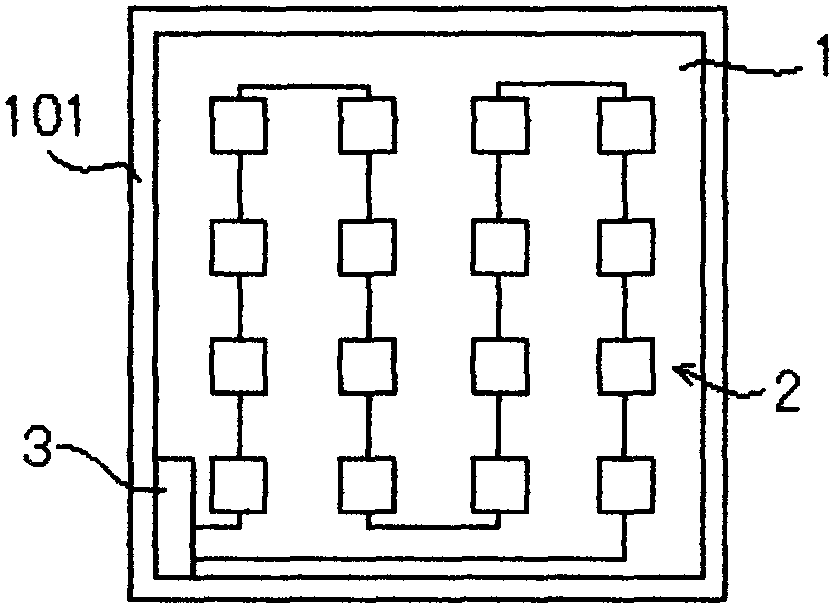

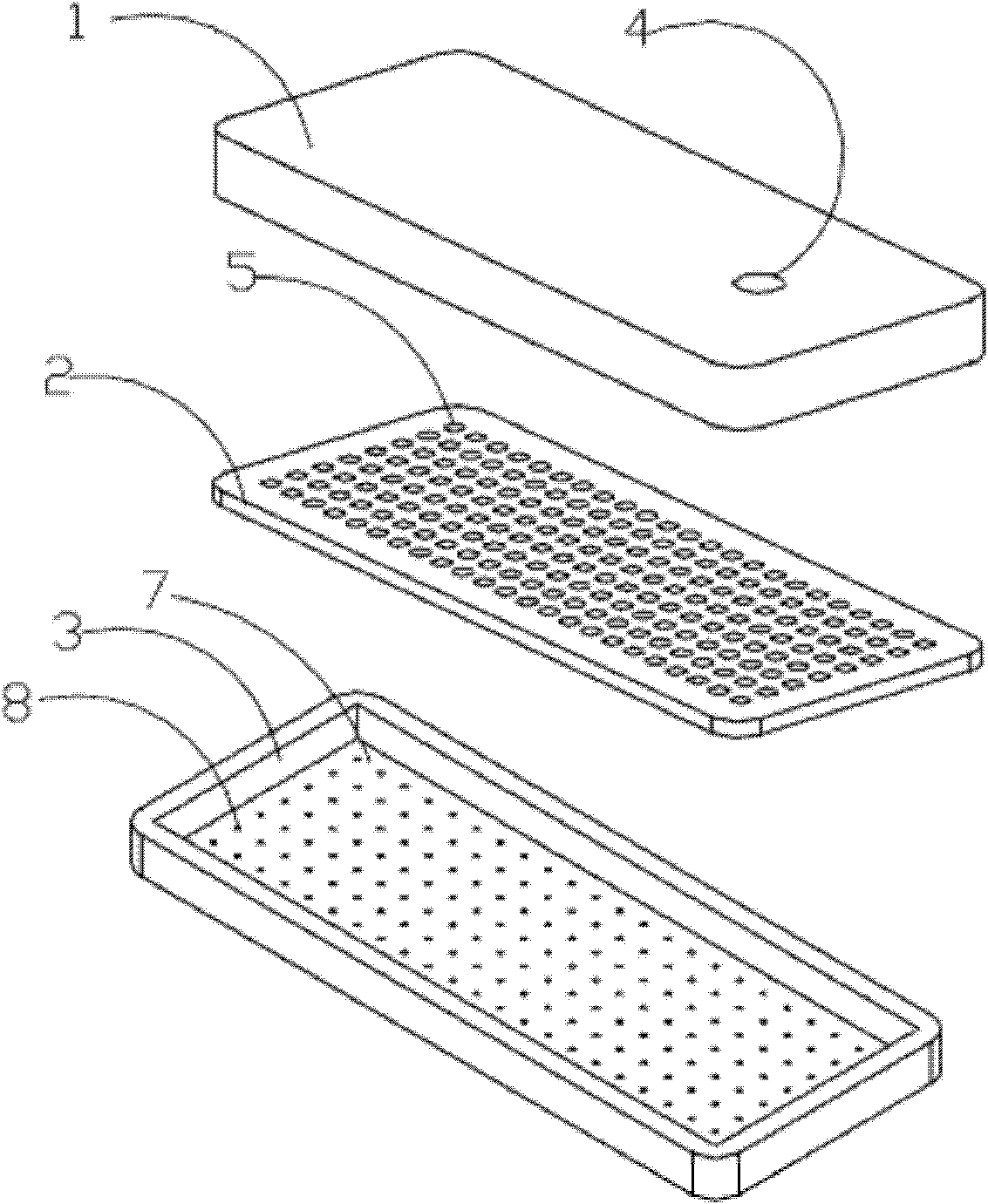

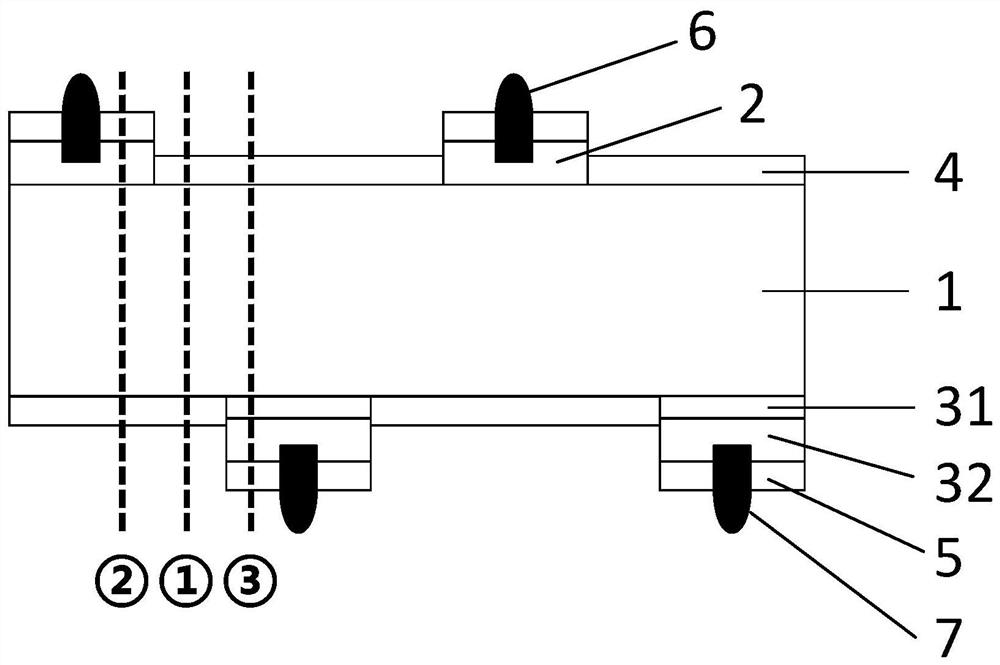

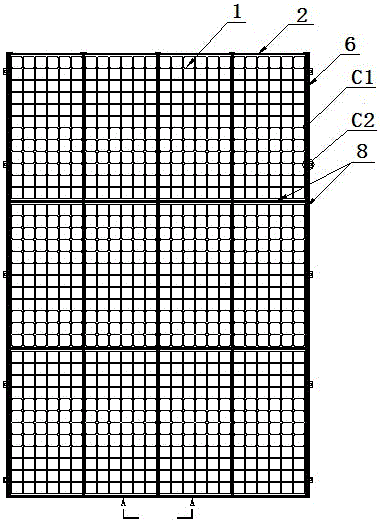

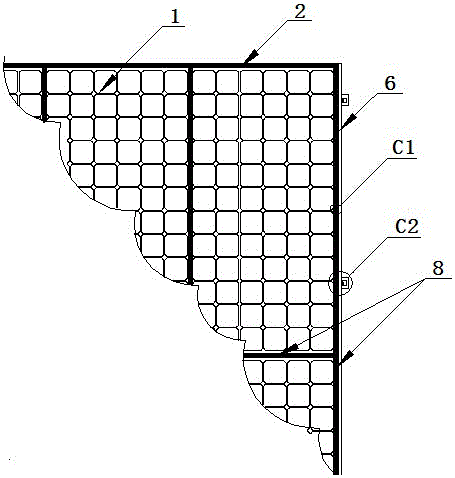

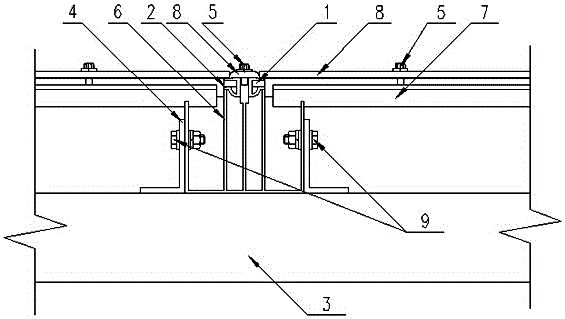

An Arrayed Electrohydrodynamic Jet Printing Head

The invention discloses an array electric fluid power printing head, which comprises an ink box, and a nozzle plate positioned at the middle part of the ink box and used for partitioning the cavity of the ink box into an upper cavity and a lower cavity; nozzle holes are distributed in the nozzle plate in an array mode, and the nozzle holes are communicated with the upper cavity and the lower cavity; the bottom of the lower part of the ink box is provided with ink outlets correspondingly arranged in an array; an upper electrode is arranged at the bottom of the nozzle plate, and a lower electrode is arranged at the bottom of the ink box, so that an electric field is formed in the lower cavity; and the ink in the upper cavity passes through the nozzle holes and enters the lower cavity, the ink forms jet under the action of the electric field of the lower cavity, and the ink is ejected for printing through the ink outlets. Because the electric fluid power printing principle is adopted in the array electric fluid power printing head, the jet diameter can reach 1 to 10 microns, and the jet is not affected by the diameter of a nozzle; and the array electric fluid power printing head has large jet dragging force, is suitable for high-viscosity solution, and does not destroy the material. The array electric fluid power printing head has the characteristics of simple structure, high printing precision and low cost, and has good industrial practicability.

Owner:HUAZHONG UNIV OF SCI & TECH

Liquid hydrogen storage material and preparation method thereof

The invention discloses a liquid hydrogen storage material and a preparation method thereof, and belongs to the technical field of hydrogen storage. The liquid hydrogen storage material comprises a carbazole hydrogen storage component and a hydrogen-rich material corresponding to the carbazole hydrogen storage component, and the carbazole hydrogen storage component is one of carbazole, N-methyl carbazole, N-ethyl carbazole, N-n-propyl carbazole, N-isopropyl carbazole or N-n-butyl carbazole. The hydrogen-rich material corresponding to the carbazole hydrogen storage component is one or a mixture of more of partial or complete hydrogenation products of the carbazole hydrogen storage component. The liquid hydrogen storage material provided by the invention has a lower melting point; due to the special relationship between the added hydrogen-rich material and the carbazole hydrogen storage component, the influence of the added hydrogen-rich material on catalyst selection does not need to be considered, and the catalyst for catalyzing the carbazole hydrogen storage component can be directly used for catalyzing the liquid hydrogen storage material; the selection of a catalyst is not influenced, and expanded production is facilitated.

Owner:陕西氢易能源科技有限公司

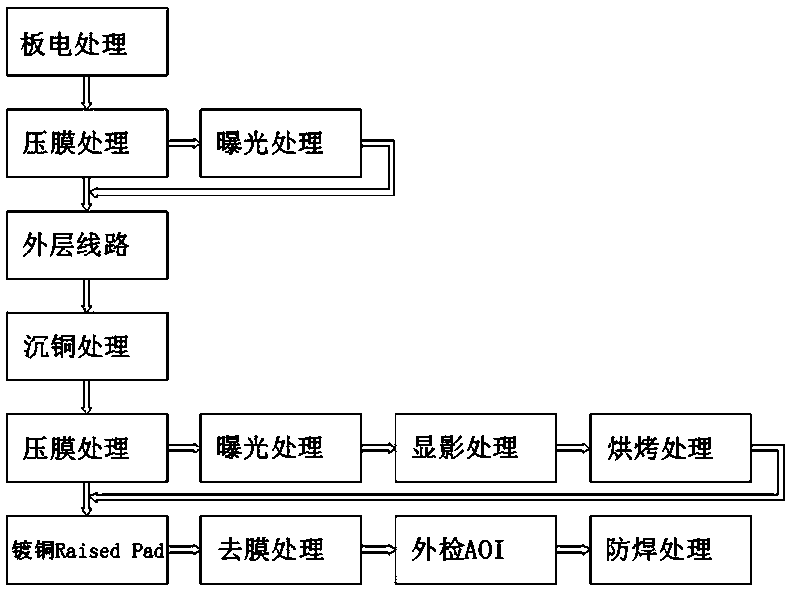

Raised Pad manufacturing method

ActiveCN111511120AOmit the preparation processSimple processPrinted circuit liquid treatmentPrinted circuit secondary treatmentCopper platingElectrical conductor

The invention relates to a Raised Pad manufacturing method, which comprises the steps of manufacturing an outer layer circuit, and the manufacturing of the outer layer circuit comprises the followingsteps of: S1, drilling the inner layer circuit of a PCB, entering a board electrical process, electroplating the whole board in an electroplating mode, and plating a layer of copper on the whole boardsurface and the wall of a drilled hole; S2, pressing a layer of photosensitive anti-corrosion film on the board surface subjected to plate electrification by using a hot roller film pressing machineto ensure the copper plating thickness; S3, manufacturing an outer layer circuit by adopting a developing machine, an etching machine and a film removing machine; S4, depositing a thin copper layer onthe independent units of the outer-layer circuit through copper deposition wires to enable the independent units to be connected together, and providing a conductor for subsequent electroplating; S5,pressing a layer of photosensitive anti-corrosion film on the board surface subjected to plate electrification by using a hot roller film pressing machine for manufacturing a PAD pattern for electroplating; and S6, placing the treated board on a copper plating wire to be subjected to copper plating operation, and obtaining the Raided Pad. The Raised Pad manufacturing method has the advantages ofthe simple process, low cost, high efficiency, the good product yield and the like.

Owner:VICTORY GIANT TECH HUIZHOU CO LTD

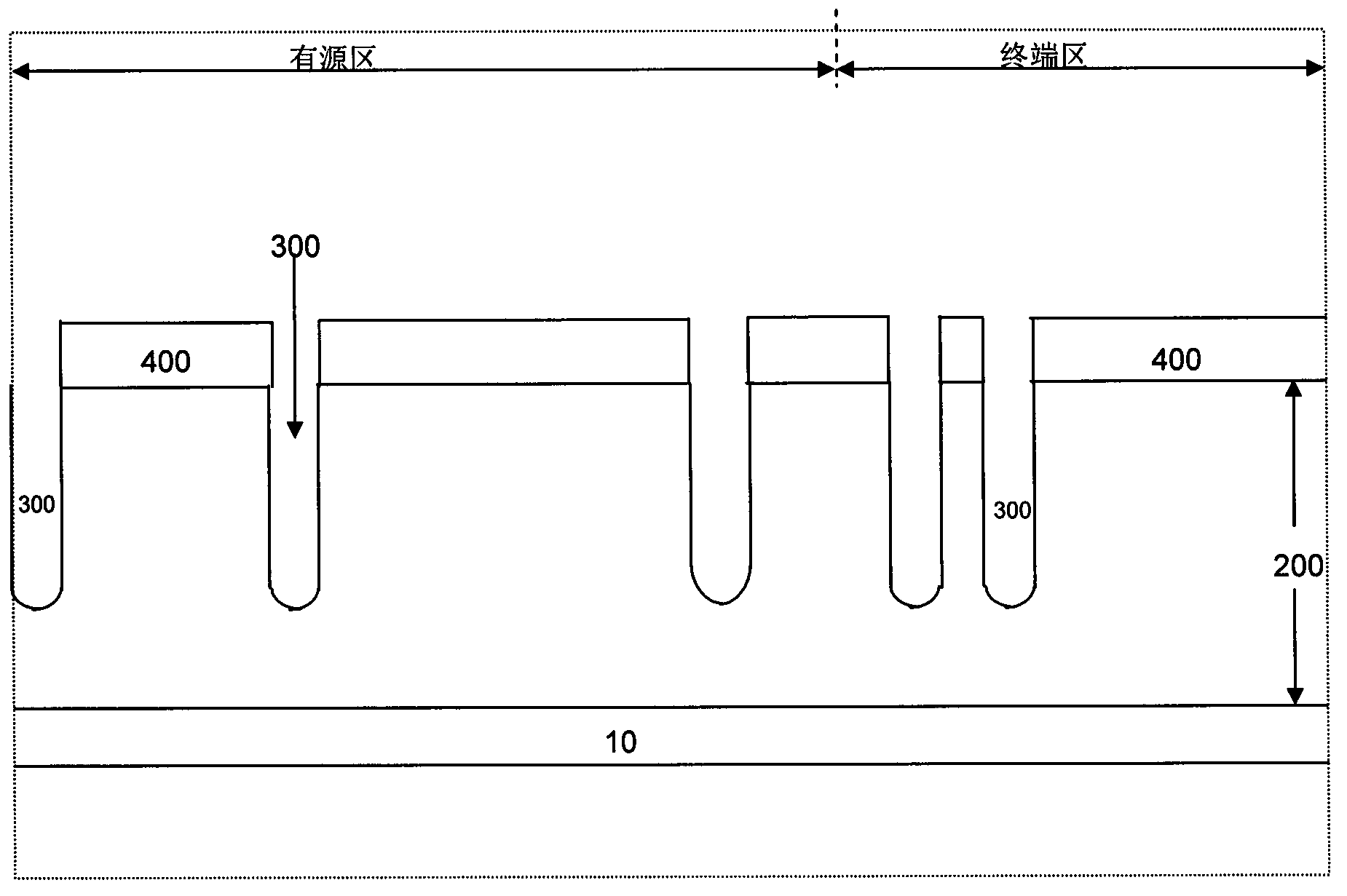

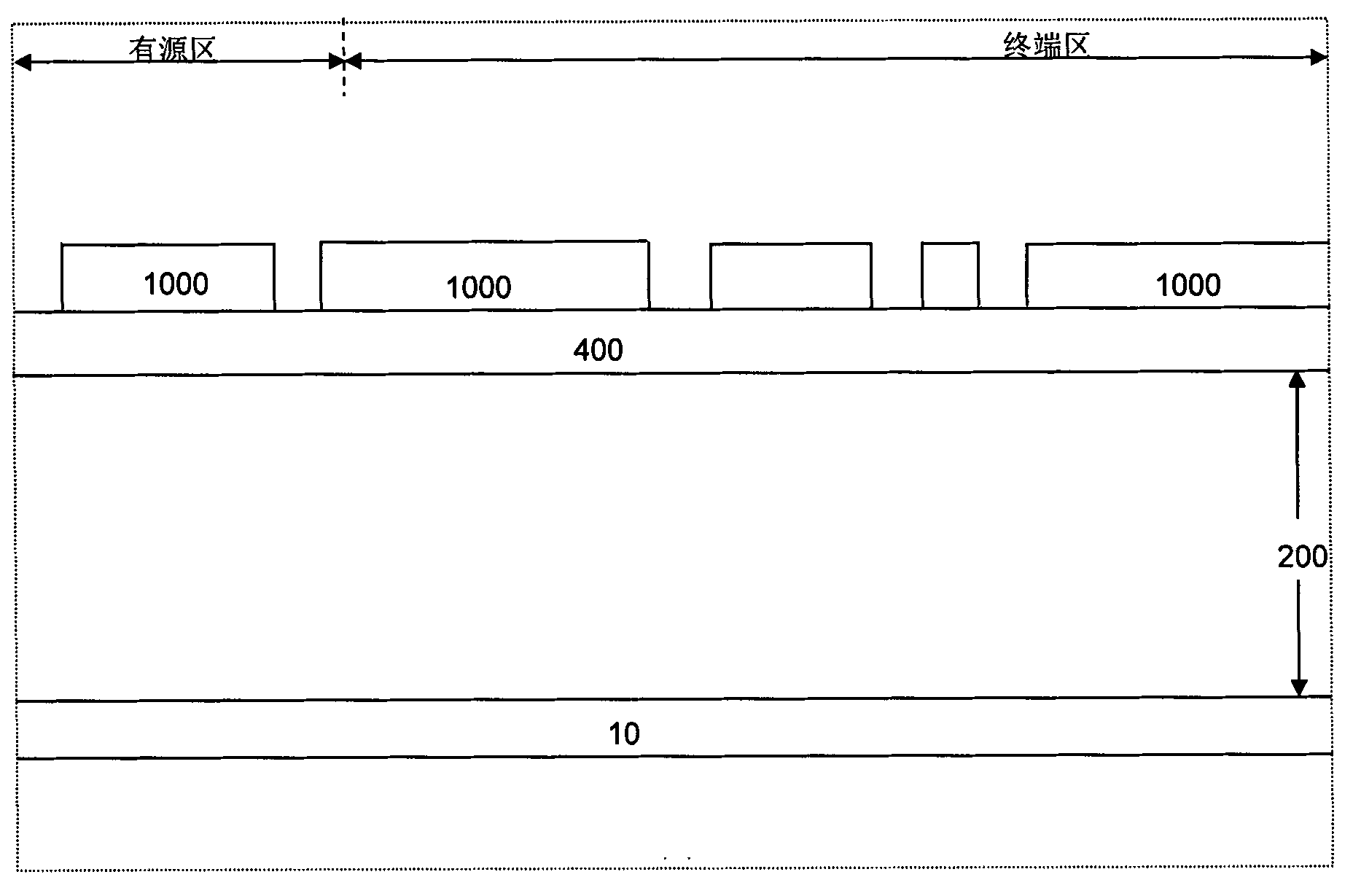

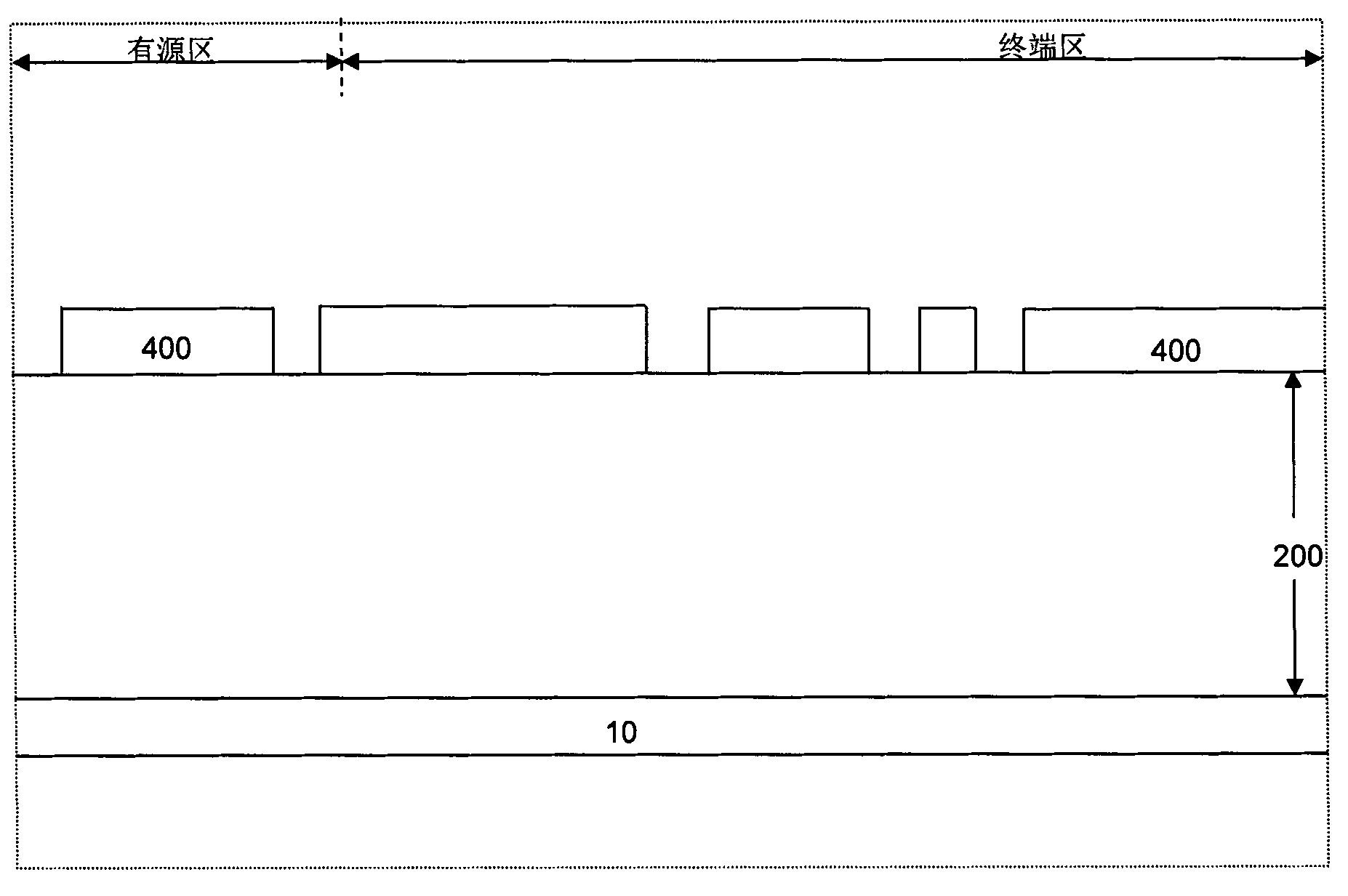

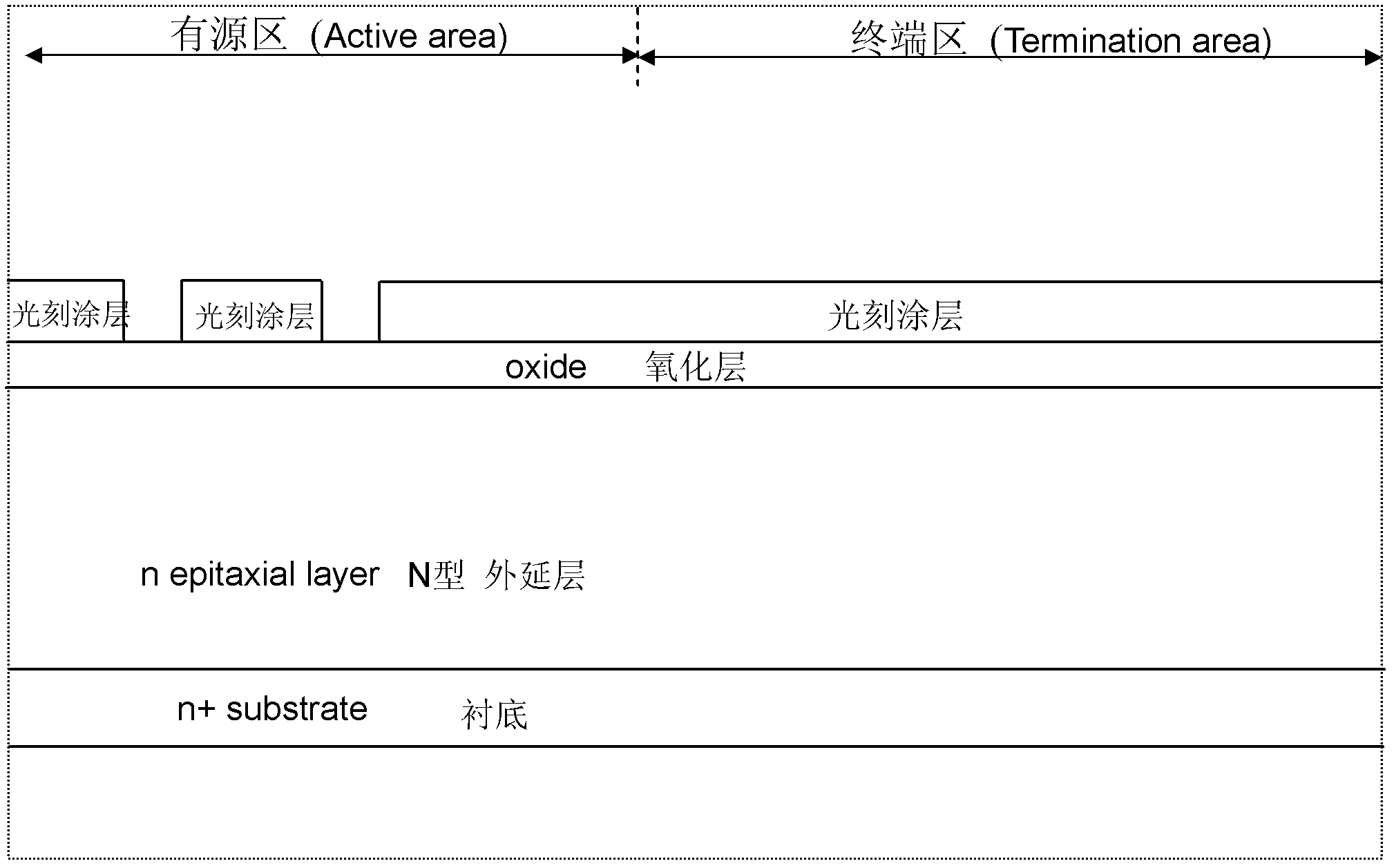

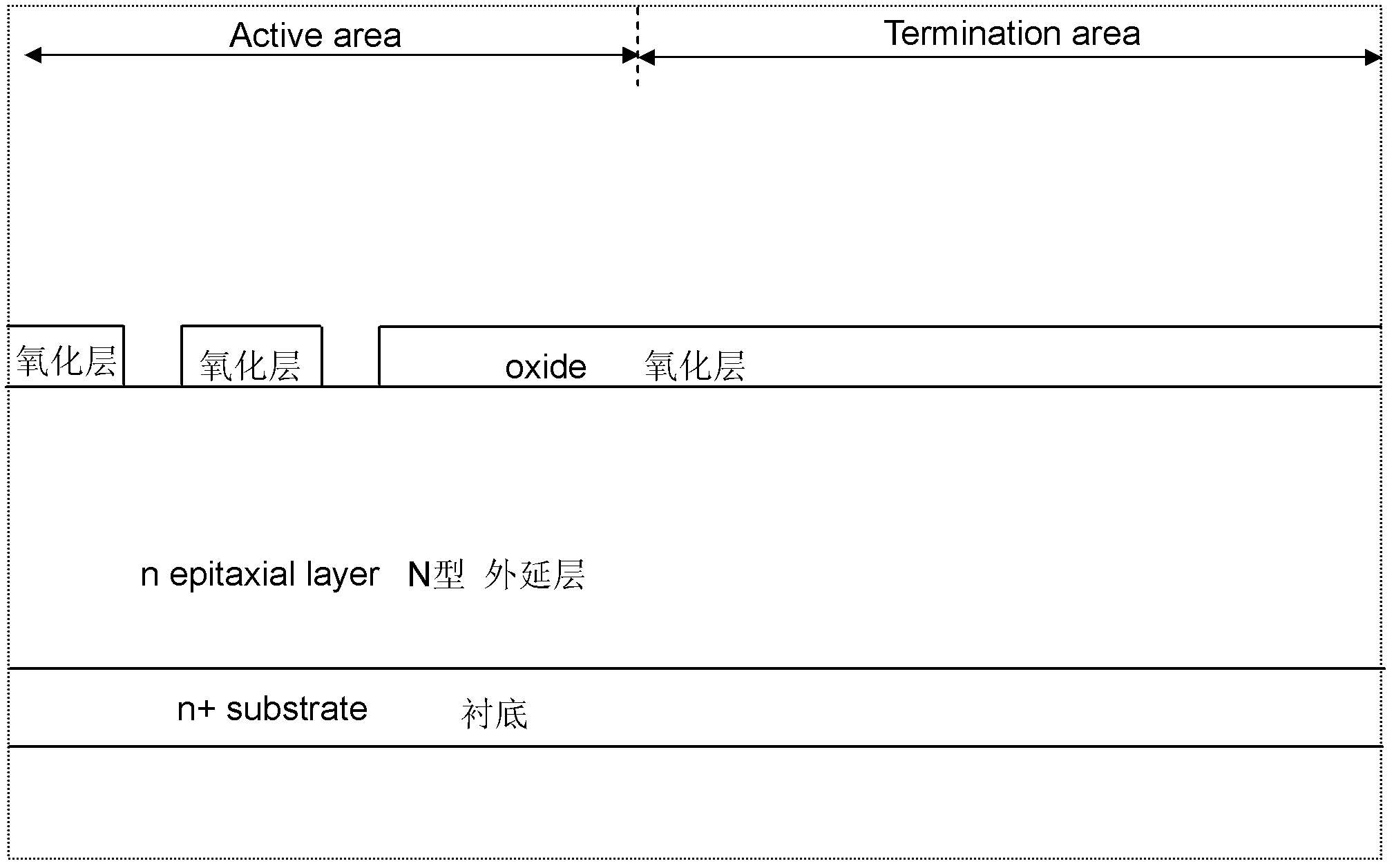

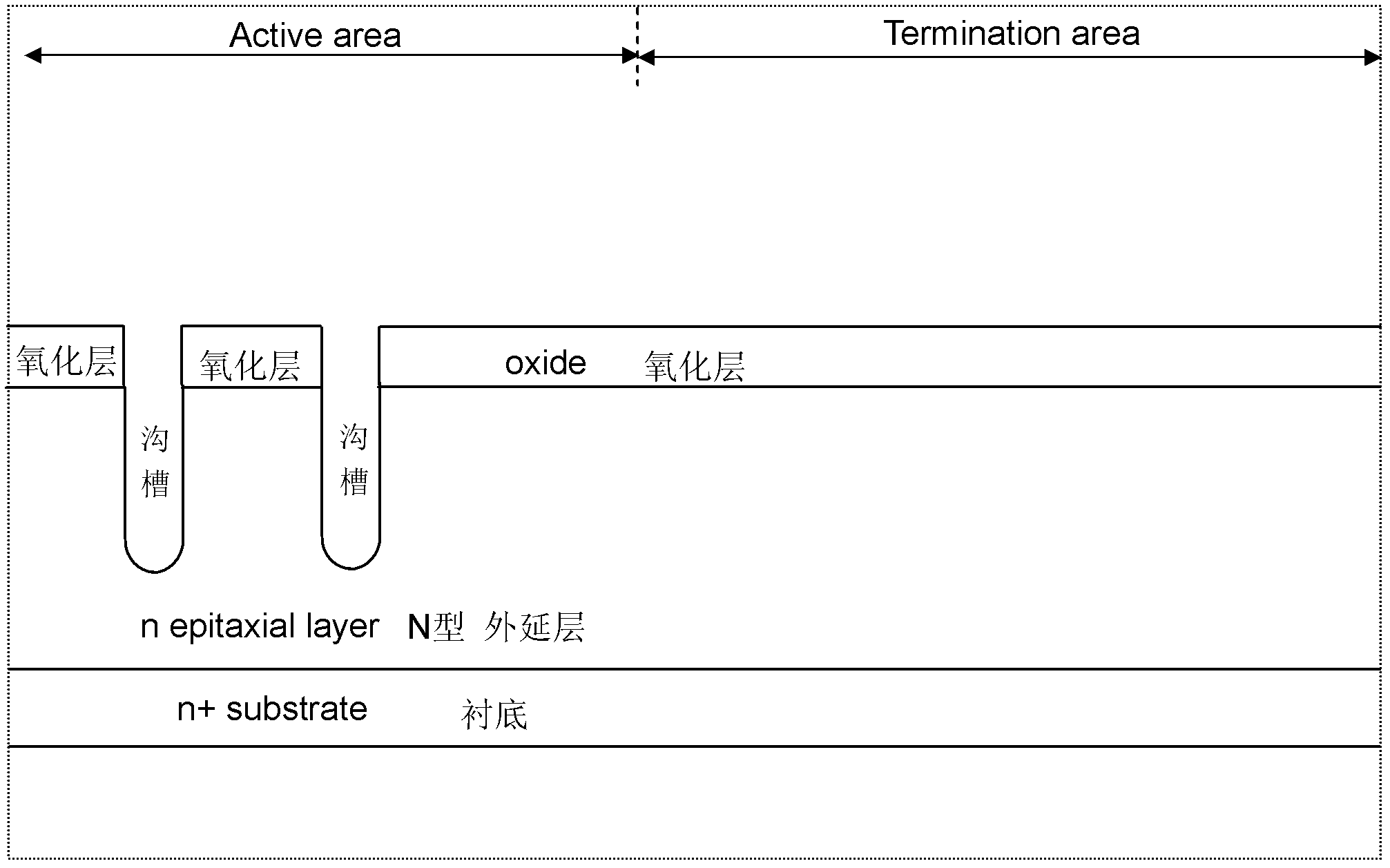

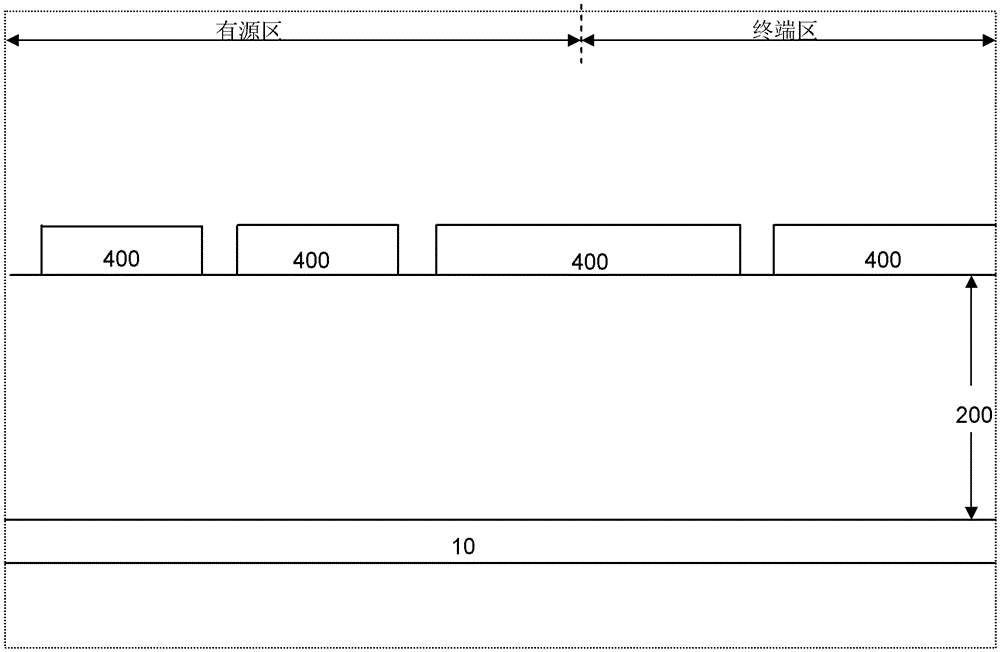

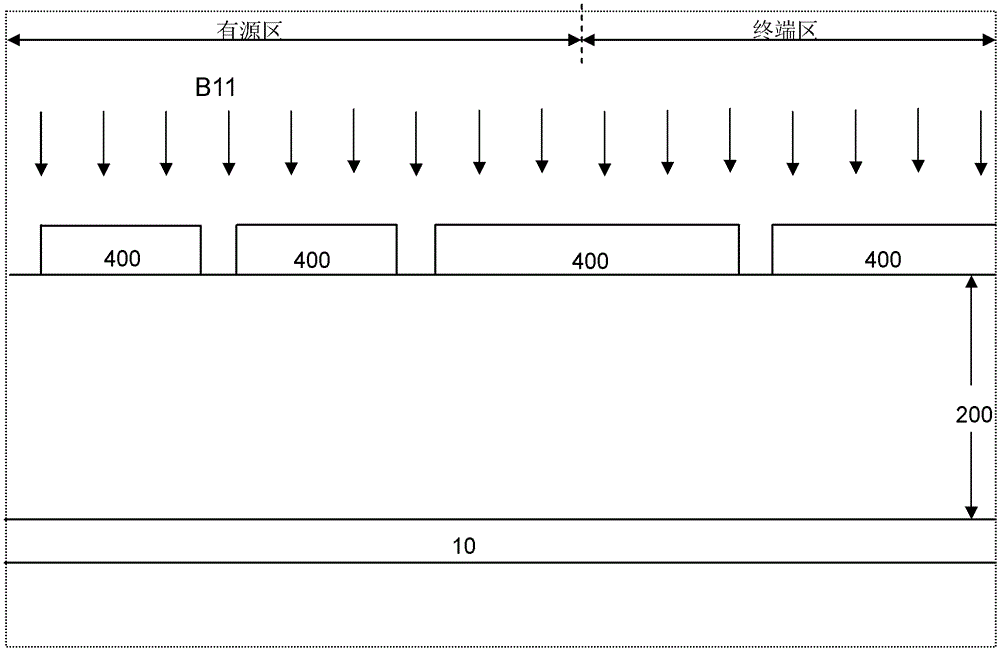

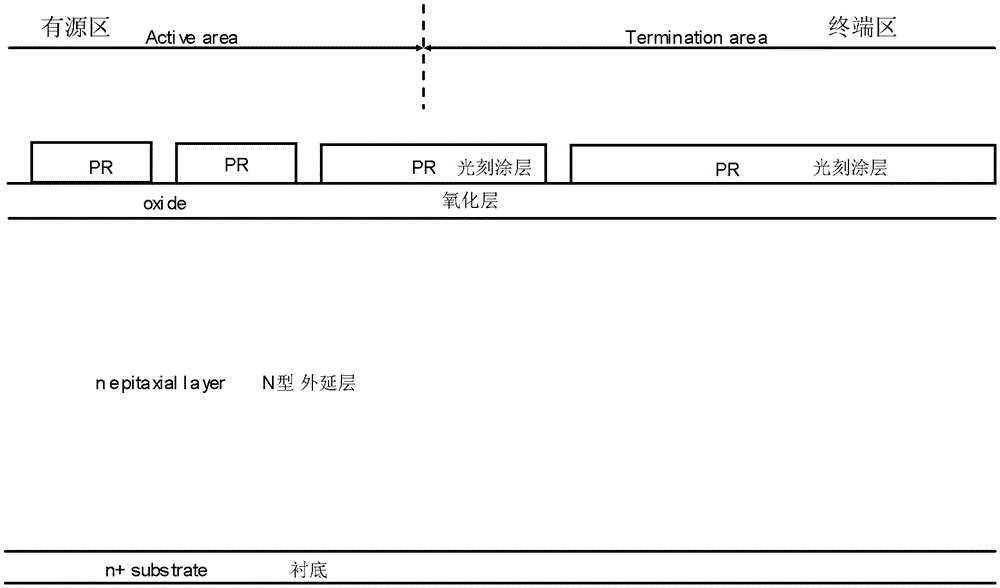

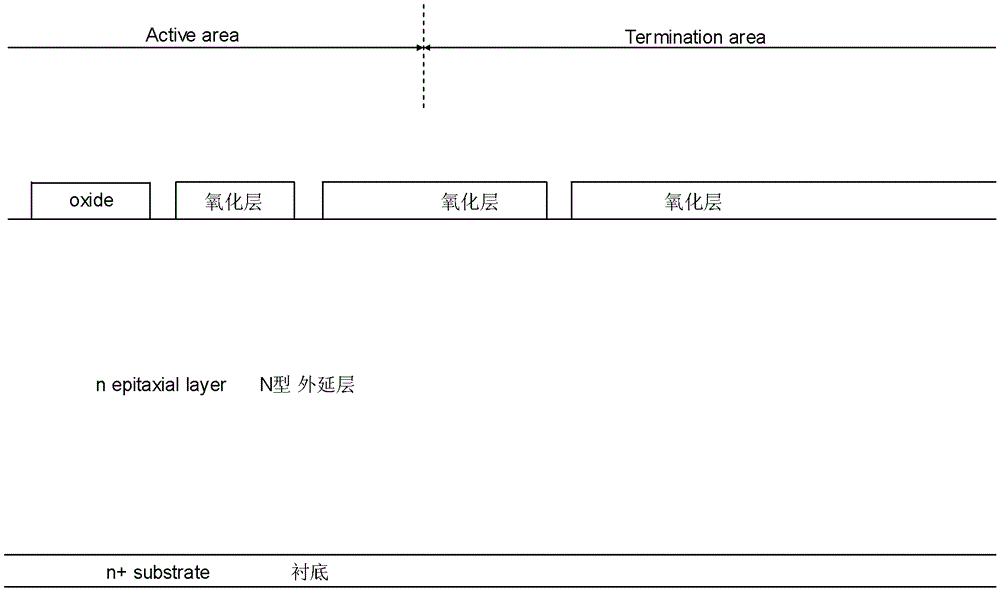

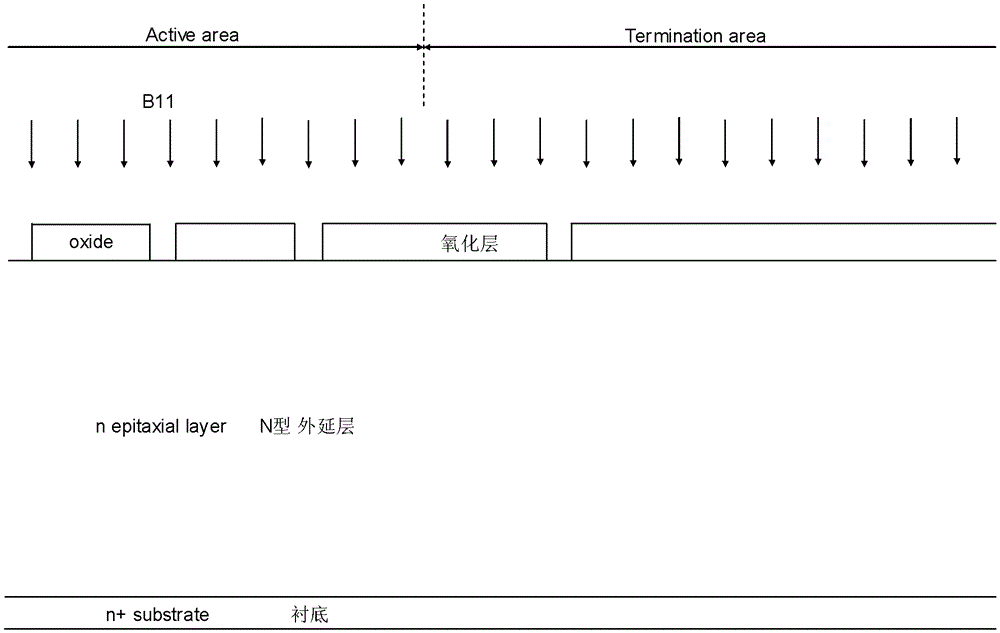

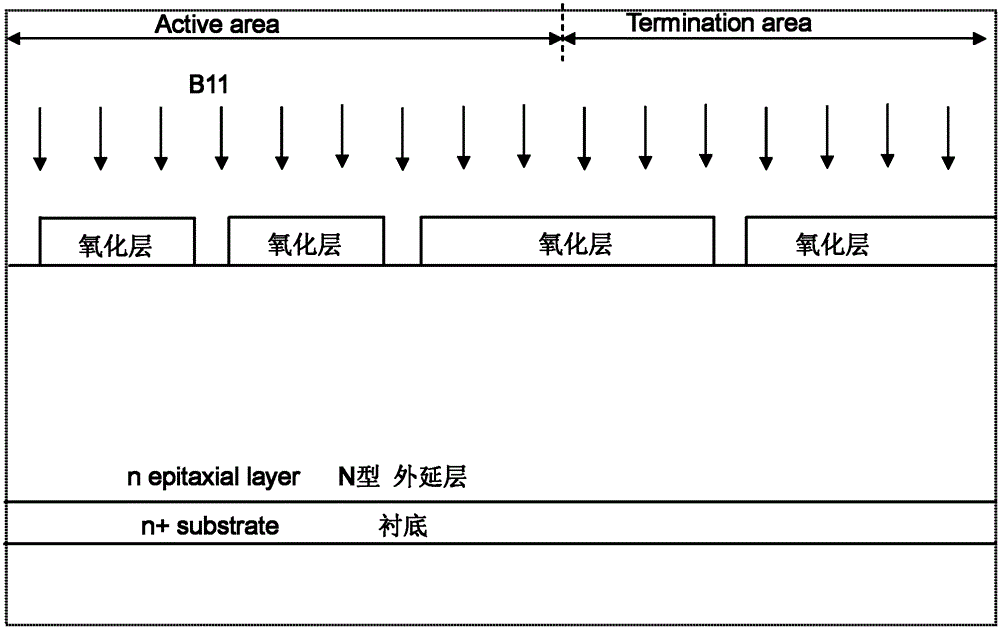

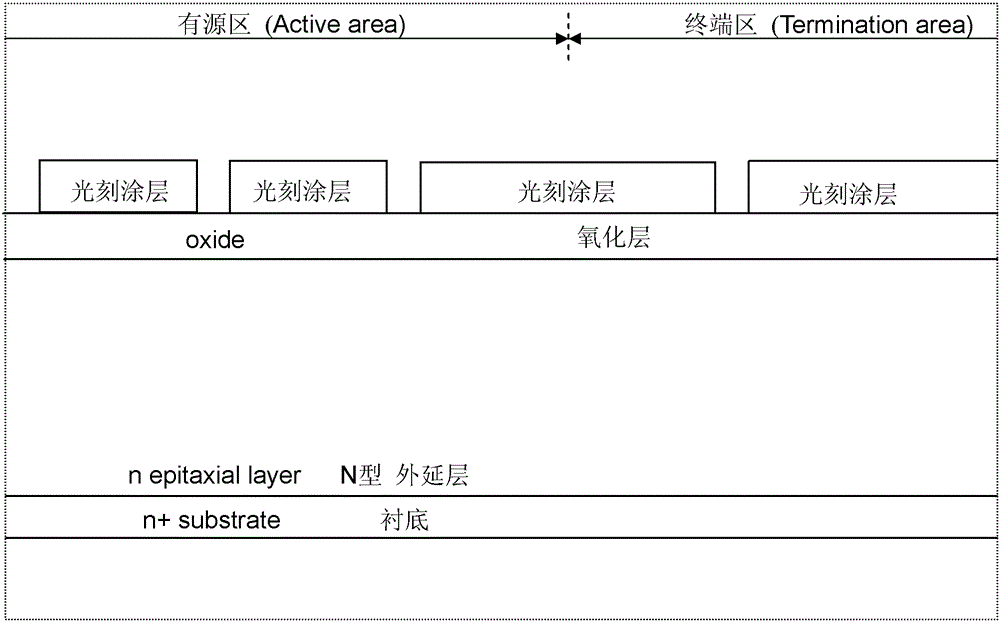

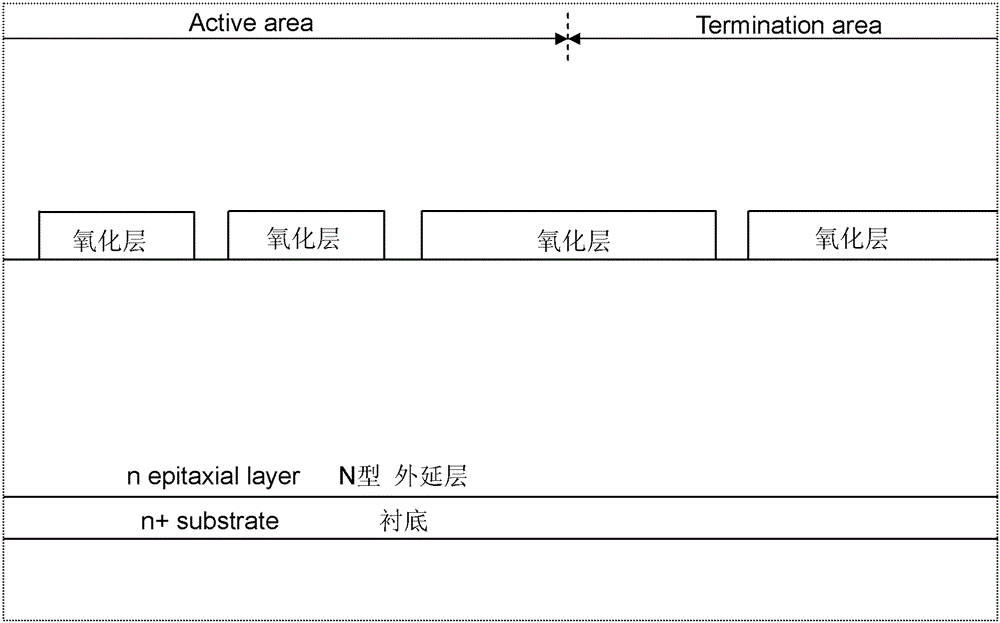

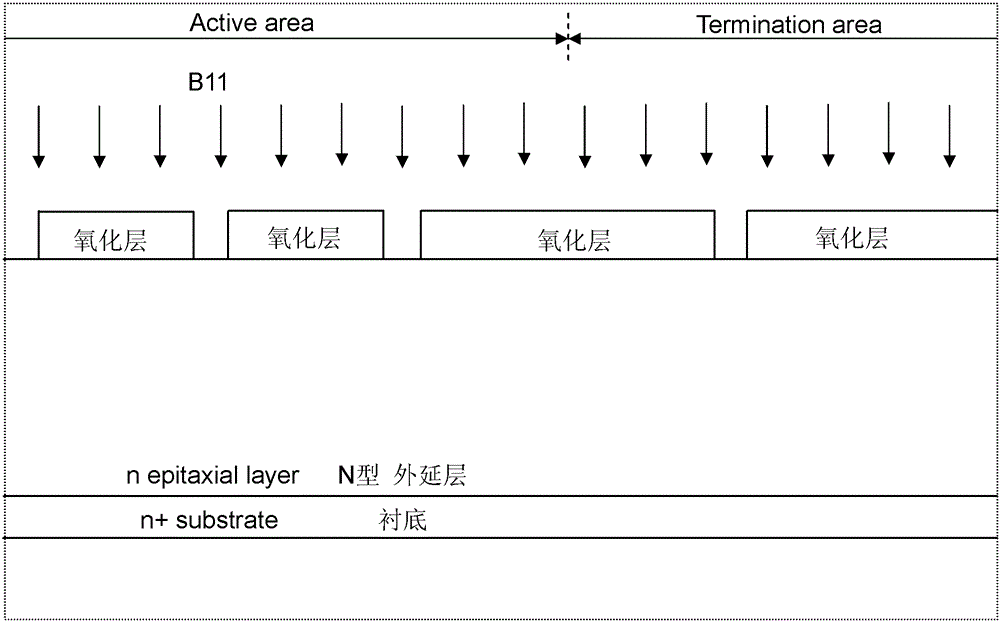

Method of preparing a groove grid-control power device

InactiveCN103632965AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDopantDielectric

The invention discloses a method of preparing a groove grid-control power device, the method comprising the steps of first eroding an epitaxial layer on a substrate by use of a groove mask to form a plurality of grooves; then, injecting a P-type dopant and an N-type dopant into the epitaxial layer to form a P-type base region and an N-type source region respectively, then depositing an interlayer dielectric on the surface of the epitaxial layer, eroding the interlayer dielectric by use of a contact hole mask to form an opening in the interlayer dielectric, eroding the surface of the epitaxial layer later to form a contact hole groove and carrying out metal plugging filling on the contact hole groove; and finally, depositing a metal layer on the surface of a device, and carrying out metal eroding by use of a metal mask to form a metal cushion layer and connection wires. By adopting the method of preparing the groove grid-control power device, preparation procedures of base region masking and source region masking are eliminated, and the preparation cost of the device is greatly reduced.

Owner:SHENZHEN LIZHEN SEMICON

Method of preparing groove semiconductor power device

InactiveCN103632964AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDopant

The invention discloses a method for preparing a groove semiconductor power device, the method comprising the steps of first eroding a P-type epitaxial layer on an N-type substrate by use of a groove mask to form a plurality of grooves; forming a gate oxide layer on an inner side wall of each groove and filling each gate oxide layer with polysilicon; then forming a PSG oxide layer on a side wall at the top of each groove and diffusing an N-type dopant in each PSG oxide layer through high temperature into the epitaxial layer to form an N-type source region 202; then depositing an interlayer dielectric on the surface of the epitaxial layer; eroding the interlayer dielectric by use of a contact hole mask to form an opening in the interlayer dielectric and injecting an N-type dopant to form an N-type source region 203; eroding the surface of the epitaxial layer later to form a contact hole groove; carrying out metal plugging filling on the contact hole groove and depositing a metal layer on the surface of a device; and carrying out metal eroding by use of a metal mask to form a metal cushion layer and connection wires. By adopting the method of preparing the groove semiconductor power device, preparation procedures of base region masking and source region masking are eliminated, and the preparation cost of the device is greatly reduced.

Owner:SHENZHEN LIZHEN SEMICON

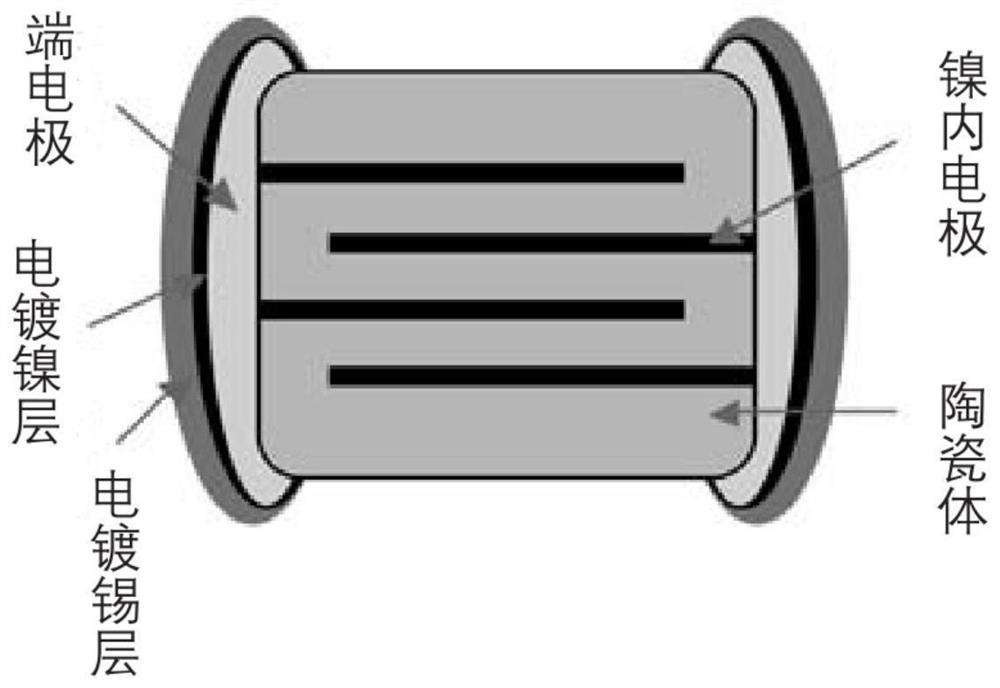

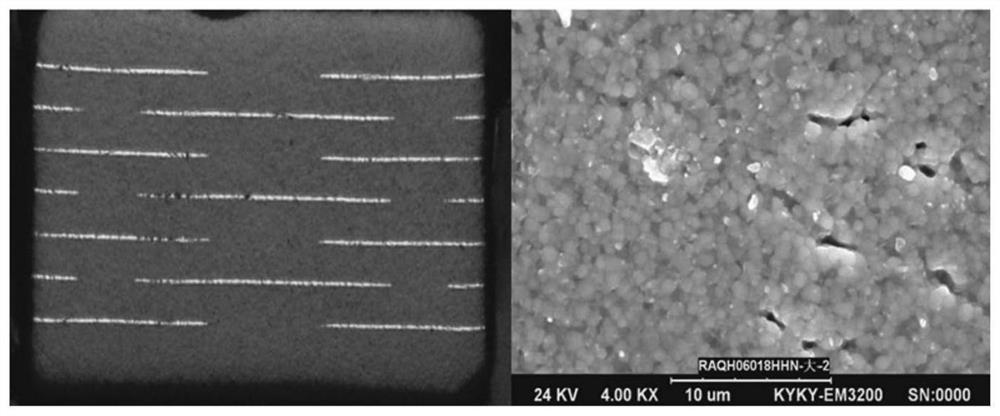

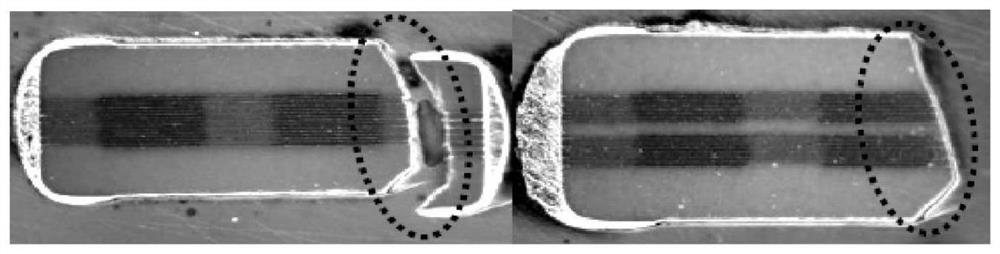

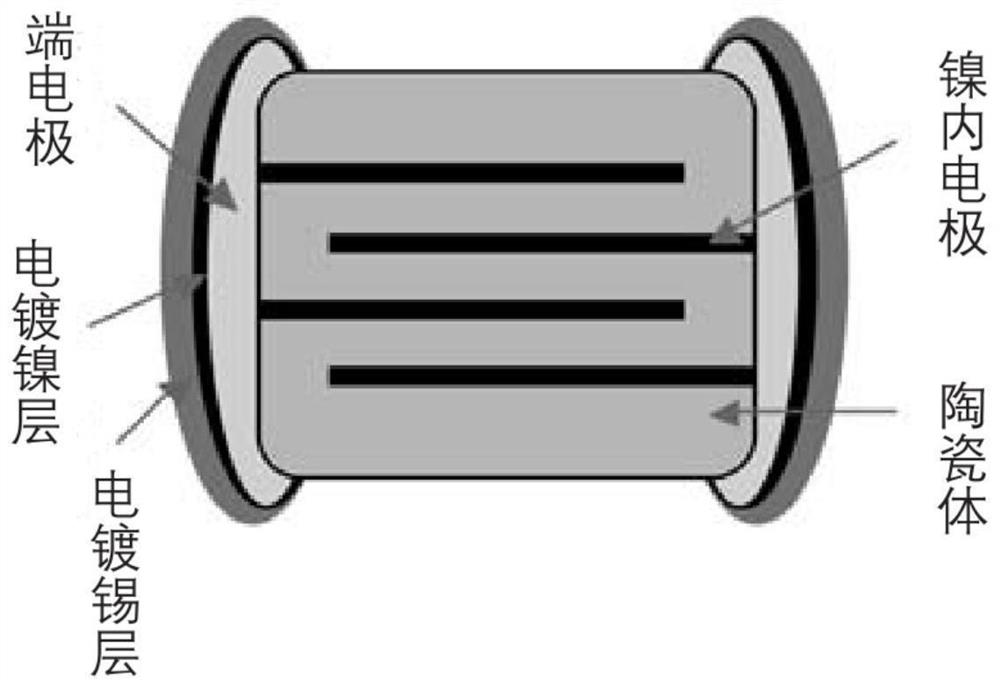

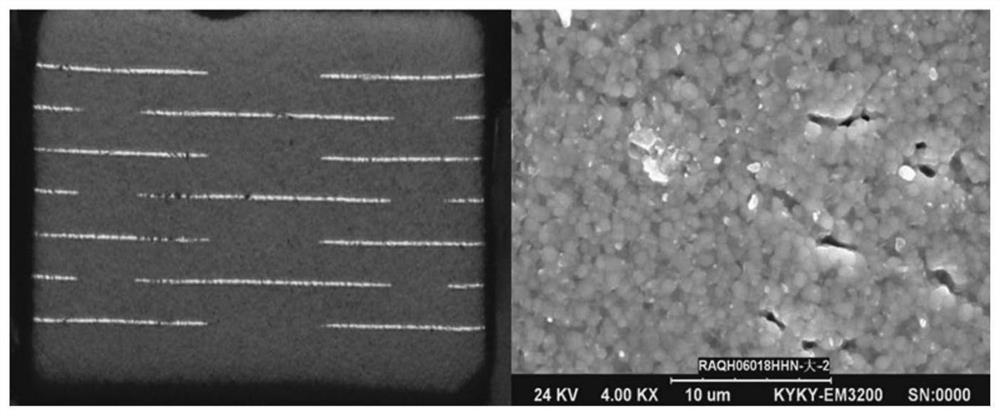

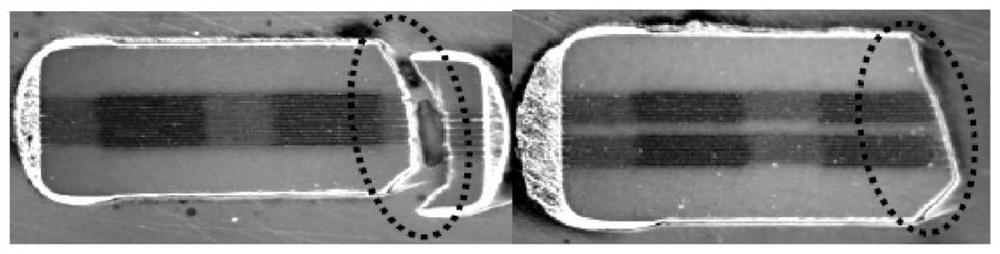

Production method of MLCC capacitor

ActiveCN112885601AHigh bonding strengthOmit the preparation processFixed capacitor dielectricFixed capacitor housing/encapsulationCeramic compositeBarium titanate

The invention discloses a production method of an MLCC capacitor. The method comprises the following steps: (1) coating a copper foil / aluminum foil with a slurry formed by plastic particles and ceramic particles, and drying to obtain a copper foil composite layer / aluminum foil composite layer; (2) sequentially stacking the copper foil composite layers and the aluminum foil composite layers together at intervals, heating to a softening point of plastic, and rolling to obtain a multi-layer ceramic composite body; and (3) putting one end surface of a multi-layer ceramic composite into a diluted hydrochloric acid to dissolve the aluminum foil near the end surface, and leaving the copper foil; putting the other end surface into a concentrated nitric acid to dissolve the copper foil near the end surface, leaving the aluminum foil, and polishing to remove an aluminum passivation layer; and then, welding the two end surfaces with an external electrode by using tin so that the copper foils are mutually connected into a whole, and the aluminum foils are mutually connected into a whole, and obtaining the MLCC capacitor. According to the production method of the MLCC capacitor, the process is simplified, the energy is saved, and the quality problems of a short circuit, open circuit and the like caused by improper sintering of a nickel powder and a barium titanate powder are avoided.

Owner:SUZHOU CHUANGHAO NEW MATERIAL TECH CO LTD

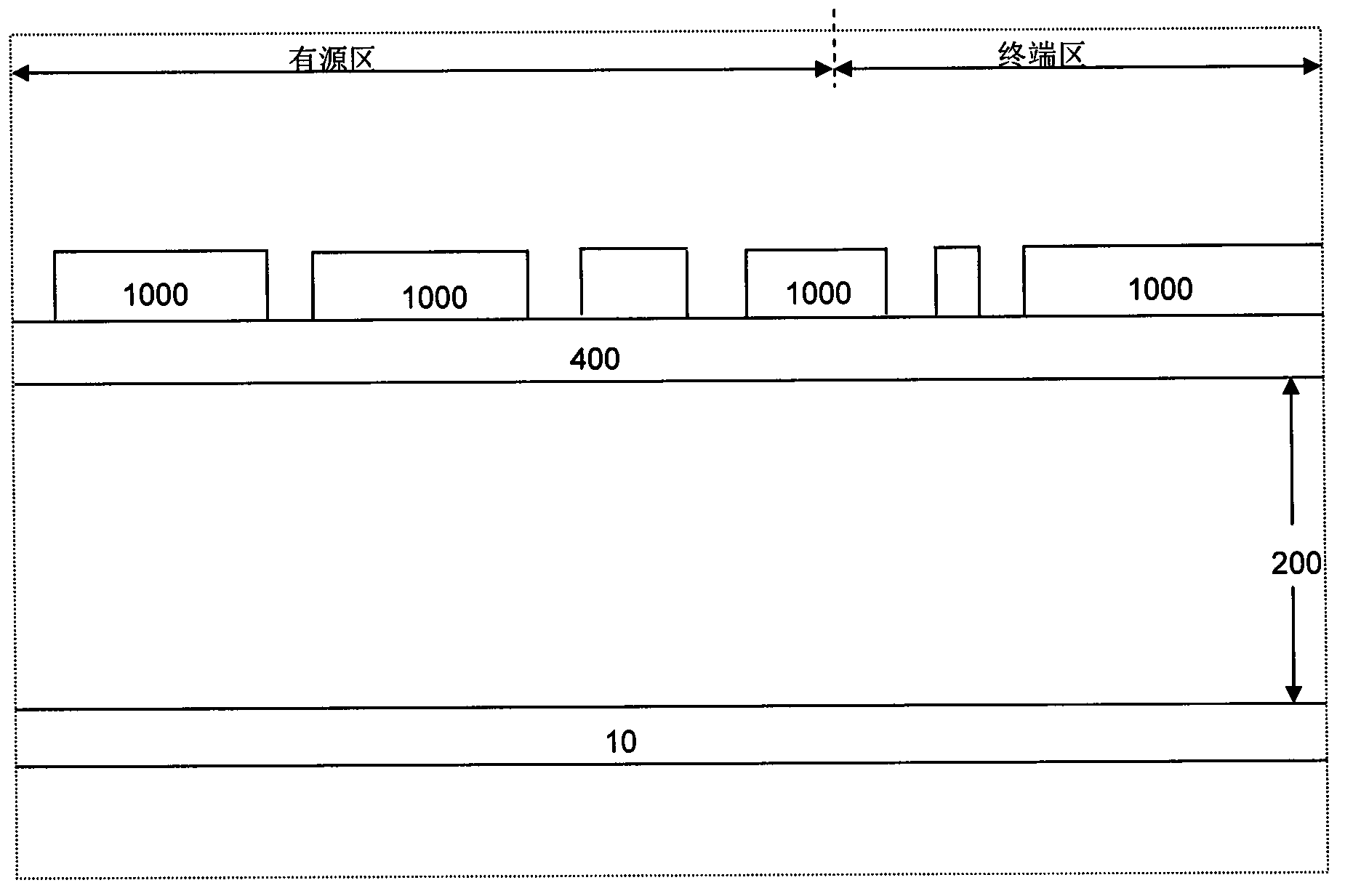

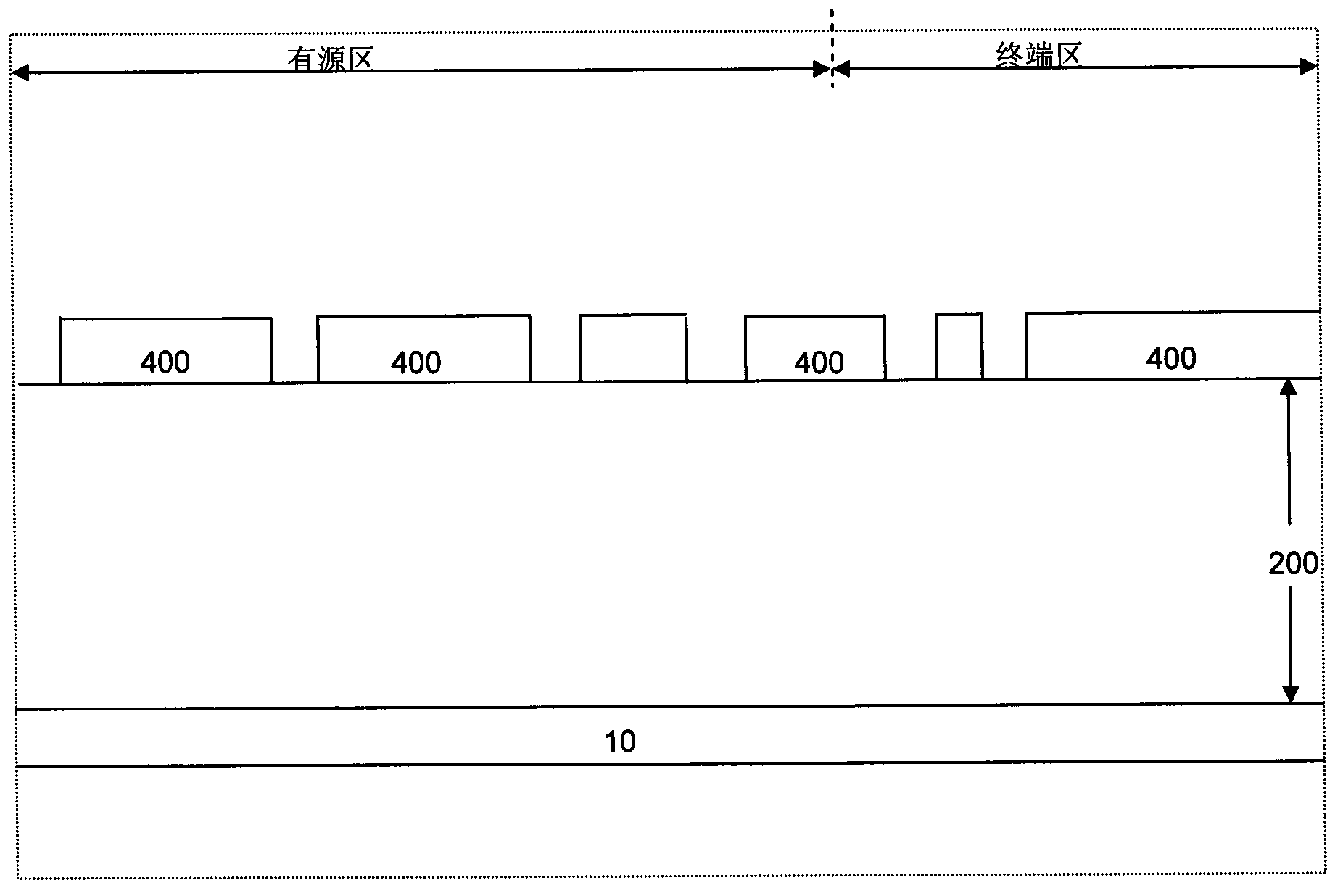

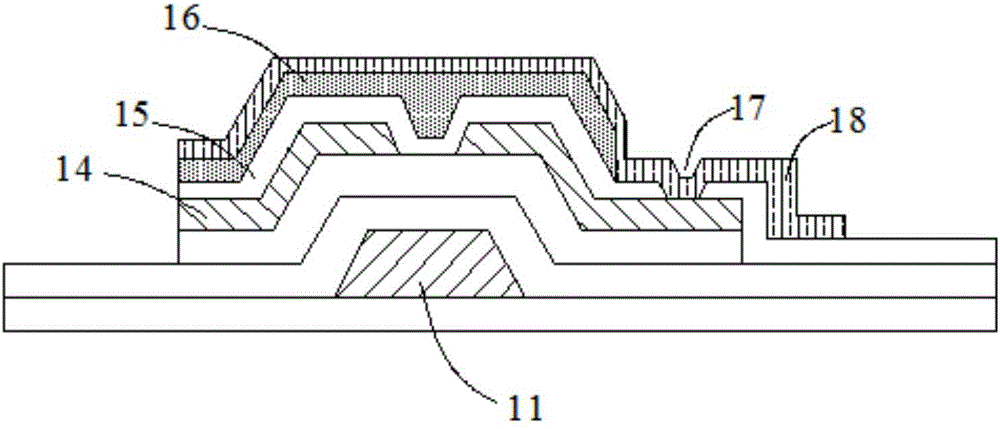

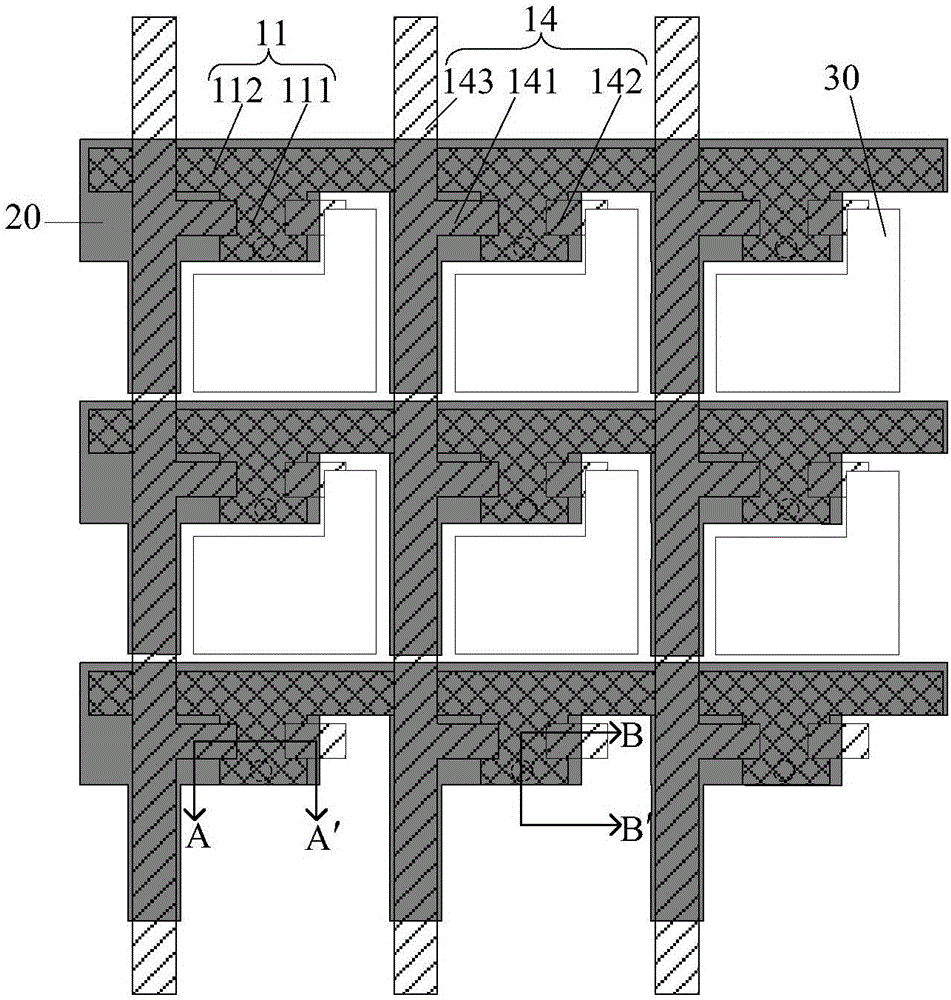

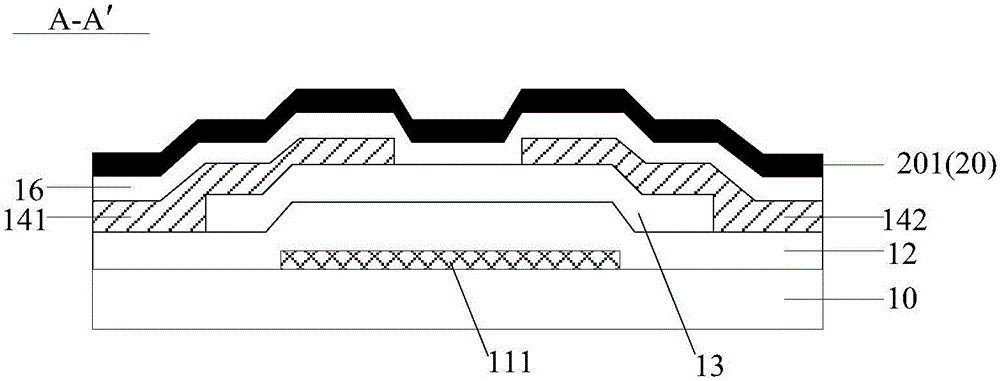

Array substrate and manufacturing method thereof and liquid crystal display panel

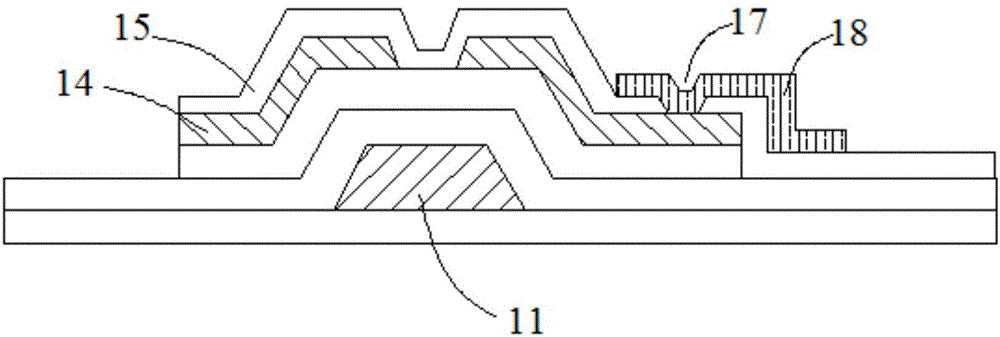

InactiveCN106328587AOmit the preparation processSimplify the manufacturing processSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayActive layer

The invention provides a manufacturing method of an array substrate. The method comprises the following steps of sequentially manufacturing a first metal layer, an insulating layer, an active layer and a second metal layer on the substrate; manufacturing a transparent conductive film on the substrate and covering the second metal layer by the transparent conductive film; coating the transparent conductive film with a third photoresist and covering a third mask on the third photoresist to photoetch a pattern on the third photoresist, wherein the projection of the second metal layer on the third photoresist is included in the pattern; and etching the transparent conductive film to form a transparent electrode layer and covering the second metal layer by the transparent electrode layer. According to the manufacturing method provided by the invention, the manufacturing cost of the array substrate is reduced, the manufacturing procedure of the array substrate is simplified and the production efficiency is improved. The array substrate and a liquid crystal display panel provided by the invention are relatively low in manufacturing cost.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

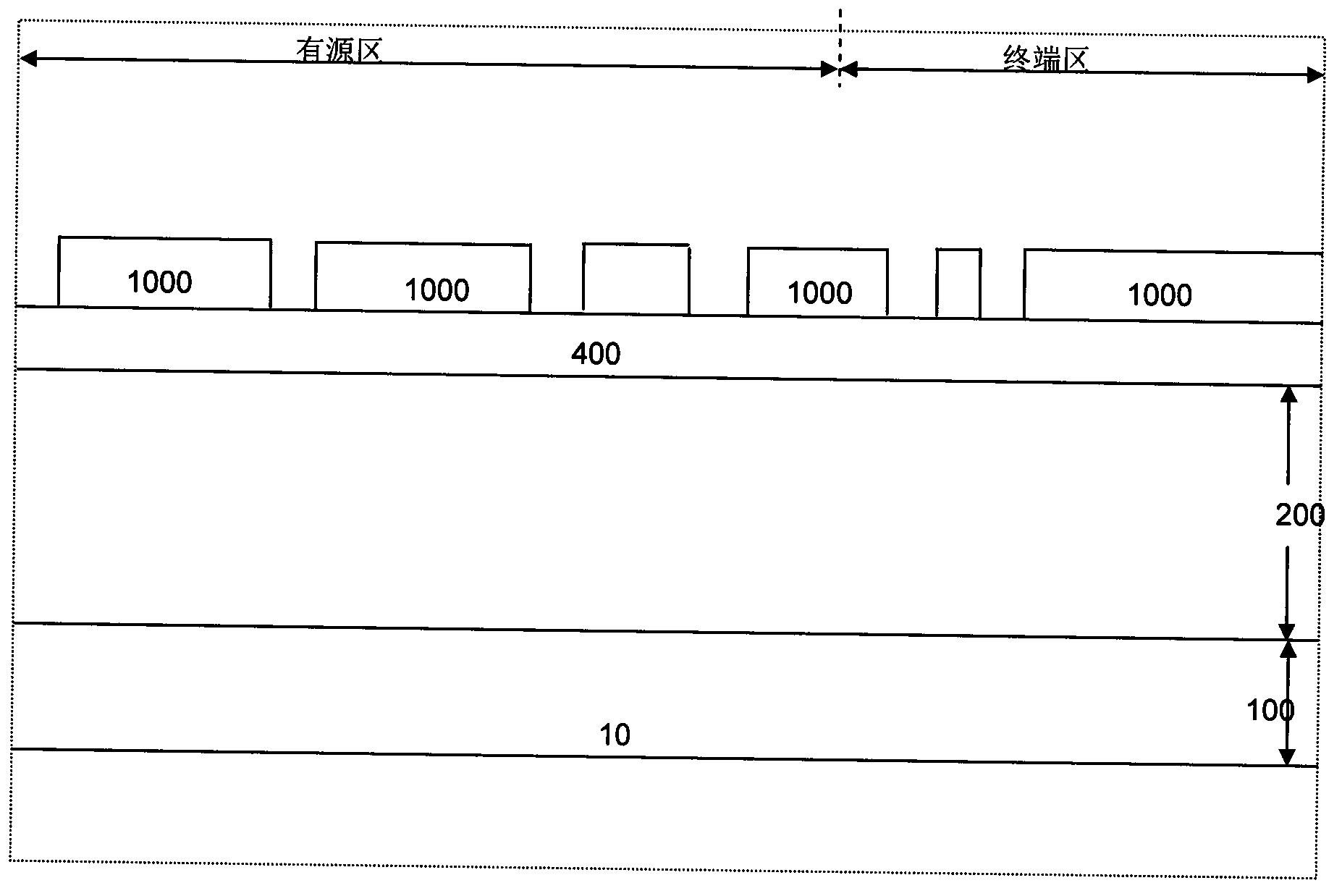

Method of preparing groove grid-control semiconductor power device

InactiveCN103632963AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricDopant

The invention discloses a method of preparing a groove grid-control semiconductor power device. The method comprises the steps of first, injecting an P-type dopant into an epitaxial layer on a substrate by use of a groove mask to form a P-type base region, and eroding on the epitaxial layer to form a plurality of grooves; then injecting an N-type dopant into the epitaxial layer to form an N-type source region, then depositing an interlayer dielectric on the surface of the epitaxial layer, eroding the interlayer dielectric by use of a contact hole mask to form an opening in the interlayer dielectric, eroding the surface of the epitaxial layer later to form a contact hole groove and carrying out metal plugging filling on the contact hole groove; and finally, depositing a metal layer on the surface of a device, and carrying out metal eroding by use of a metal mask to form a metal cushion layer and connection wires. By adopting the method of preparing the groove grid-control semiconductor power device, preparation procedures of base region masking and source region masking are eliminated, and the preparation cost of the device is greatly reduced.

Owner:SHENZHEN LIZHEN SEMICON

Preparation method of trench semiconductor power discrete device

InactiveCN103187281AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantP type doping

The invention discloses a preparation method of a trench semiconductor power discrete device. The preparation method of the trench semiconductor power discrete device includes a first step of injecting P-type dopant into an epitaxial layer arranged on a substrate to form P-type base regions through a trench mask and conducting corrosion on the epitaxial layer to form a plurality of grid trenches; a second step of depositing interlayer mediums on the epitaxial layer, conducting the corrosion on the interlayer mediums through a contact hole mask, forming trenches in the interlayer mediums, injecting N-type dopant to form N-type source regions, conducting the corrosion on the surface of the epitaxial layer to form contact trenches, and conducting metal plugging filling on the contact trenches; and a third step of depositing a metal layer on the surface of the discrete device, conducting metal corrosion through a metal mask and forming a metal substrate layer and a connecting wire. The preparation method of the trench semiconductor power discrete device eliminates preparation procedures of a base region mask and a source region mask, and therefore the manufacturing cost of the discrete device is greatly reduced. In addition, original electrical characteristics of the discrete device cannot be influenced.

Owner:立新半导体有限公司

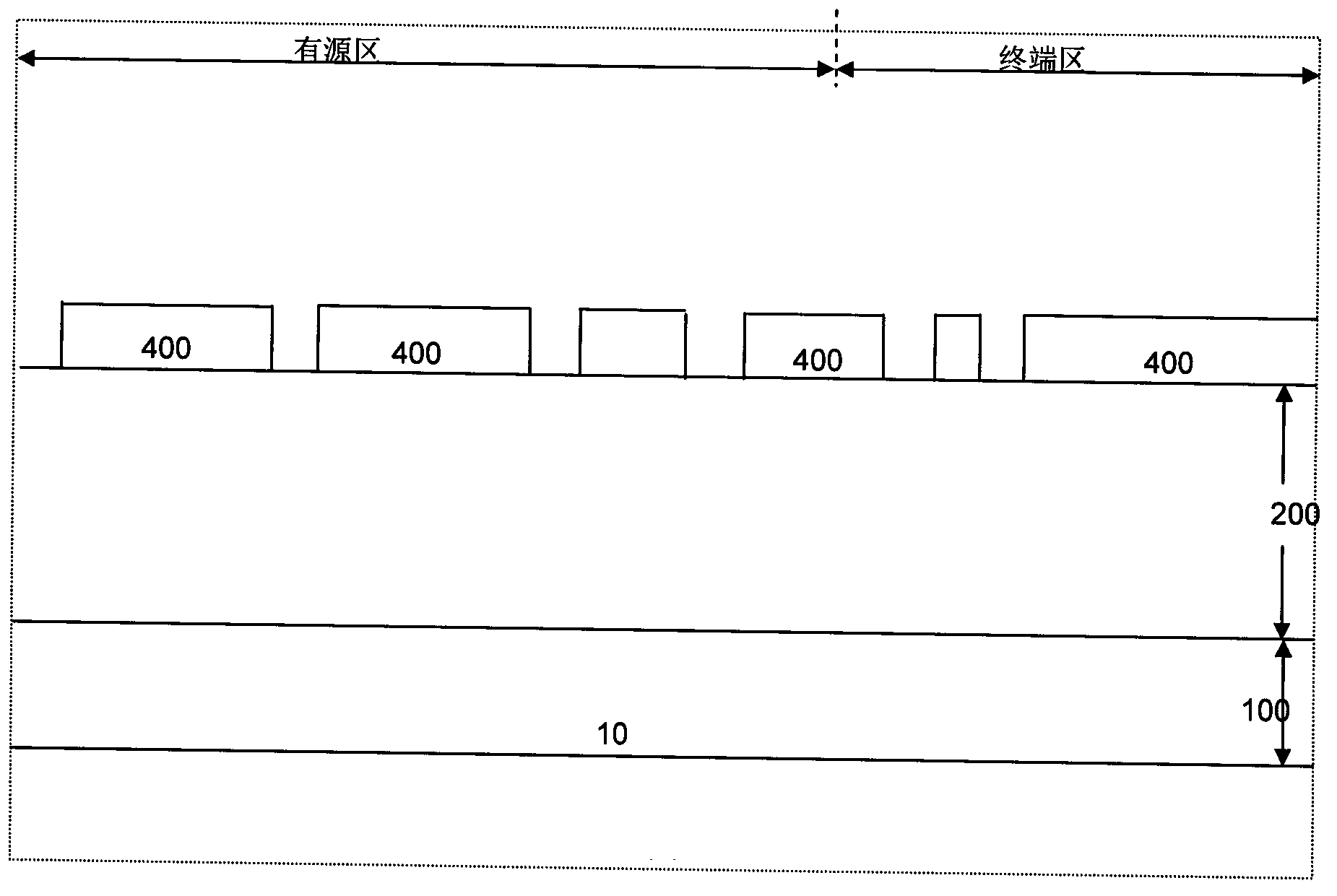

Preparation method for groove semiconductor discrete device

InactiveCN103187287AOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingSource areaElectric properties

The invention discloses a preparation method for a groove semiconductor discrete device. The preparation method for the groove semiconductor discrete device includes the following steps: firstly, eroding an epitaxial layer by utilization of a groove mask to form a plurality of grid electrode grooves; then depositing interlayer medium on the surface of the epitaxial layer, eroding the interlayer medium by utilization of a contact hole mask, open holes are formed in the interlayer medium, injecting p-type and n-type dopant to respectively form a p-type base area and a n-type source area, eroding the surface of the epitaxial layer to form contact grooves, and filling the contact grooves through metal inserting plugs; and finally, depositing a metal layer on the upper surface of the device, and performing metal erosion by utilization of a metal mask to form a metal padding layer and connecting lines. By adoption of the preparation method, the preparation processes of a base area mask and a source area mask are omitted, and manufacturing cost of the device is enabled to be reduced greatly; and meanwhile, original electric properties and reliability of the device can not be affected, and therefore the performance / cost ratio of the device is increased.

Owner:立新半导体有限公司

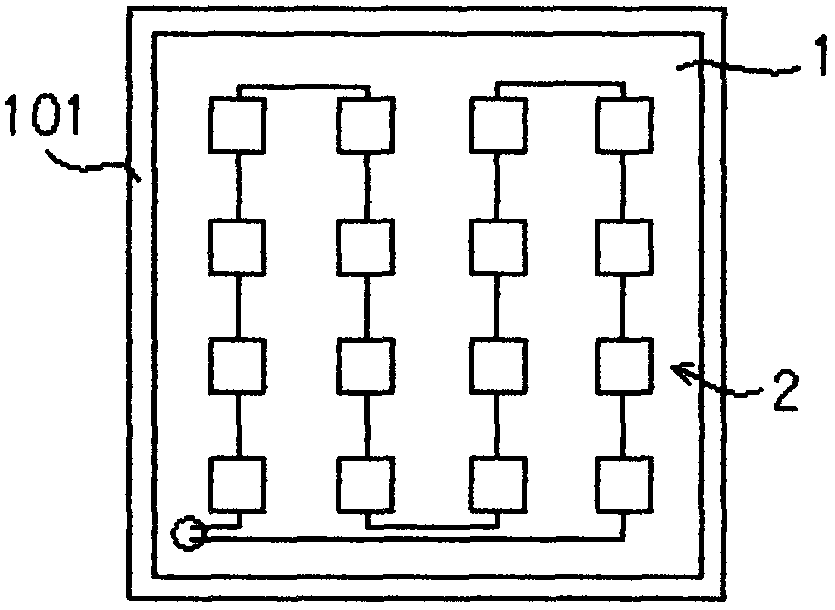

Light-emitting diode (LED) panel lamp and manufacture method thereof

InactiveCN103162134ASave resourcesLow costPoint-like light sourceElectric circuit arrangementsBuilding materialLoad circuit

The invention discloses a light-emitting diode (LED) panel lamp which comprises a base seat, an LED load circuit and a lamp cover, wherein the LED load circuit is formed in a series connection mode or a parallel connection mode, and the lamp cover is made of light-permeable materials. The LED load circuit and the lamp cover are connected on the base seat. The base seat is an aluminum plate which is also used as a suspended ceiling. The LED load circuit is arranged on the surface of the base seat in a printed mode. Two ends of the LED load circuit are connected with a power adaptor. Building materials are combined with the lamp, unessential materials are eliminated, resources are saved, cost is reduced, and meanwhile the weight and the size of the LED panel lamp are reduced. According to integrally forming design, complex manufacture processes are eliminated, and manufacture cost is saved. The base seat with a large area is utilized for assisting heat dissipation, service lives of a power source and a lamp source are prolonged, recycling cost is low, and environment protection is benefited.

Owner:FOSHAN AIDIOU PHOTOELECTRIC TECH CO LTD

Array substrate and display panel

InactiveCN106298814AImprove display qualityOmit the preparation processSolid-state devicesSemiconductor devicesGratingBottom gate

The invention provides an array substrate and a display panel, and relates to the technical field of the display. The technological process of the display panel can be simplified. The array substrate comprises a substrate, and a gate metal layer, a gate insulating layer, a semiconductor active layer, a source drain metal layer, a barrier layer and a light shielding structure which are successively installed on the substrate; the gate metal layer comprises a bottom gate electrode and a grating line; the source drain metal layer comprises a source electrode, a drain electrode and a data line; and the light shielding structure comprises an electric electrode, and the electric electrode is electrically connected with the bottom gate electrode, wherein the light-proof light shielding structure is further used as a black matrix.

Owner:BOE TECH GRP CO LTD +1

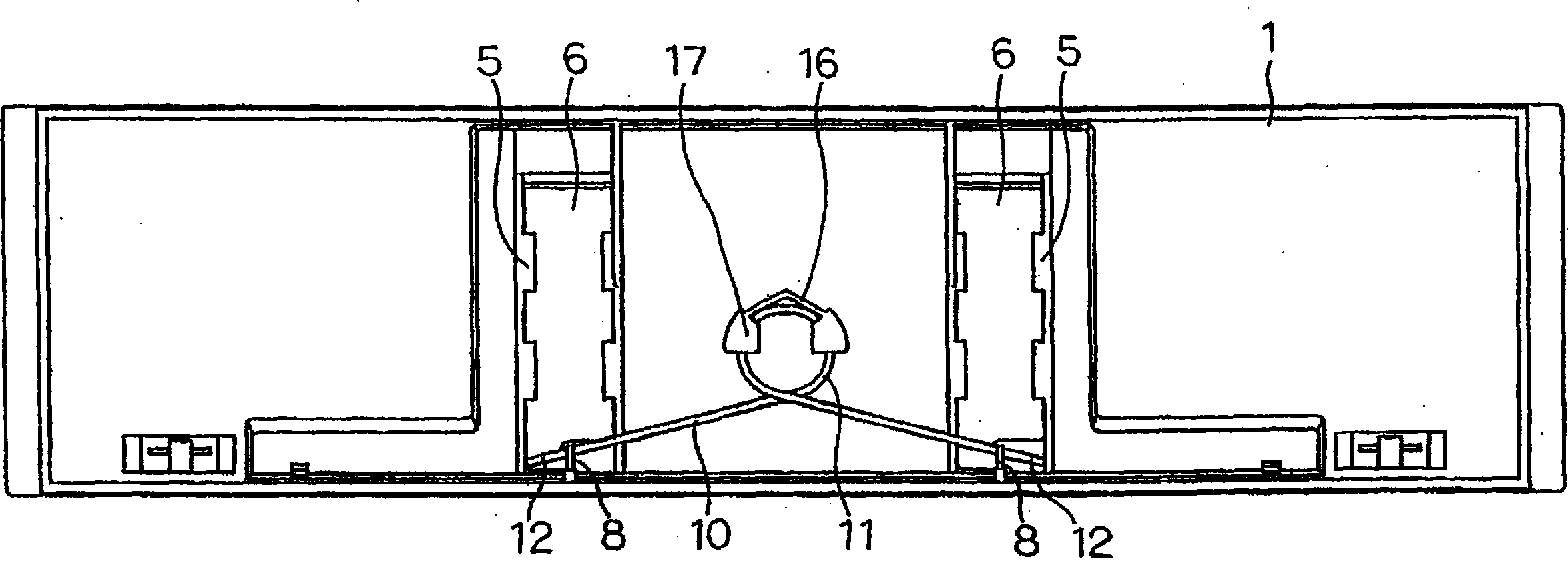

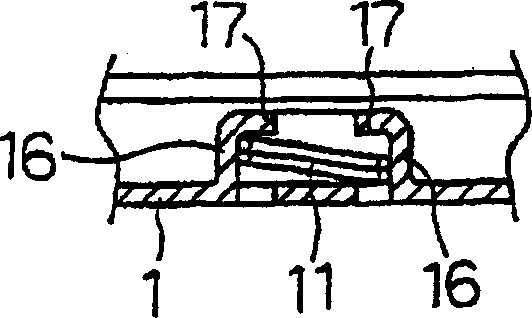

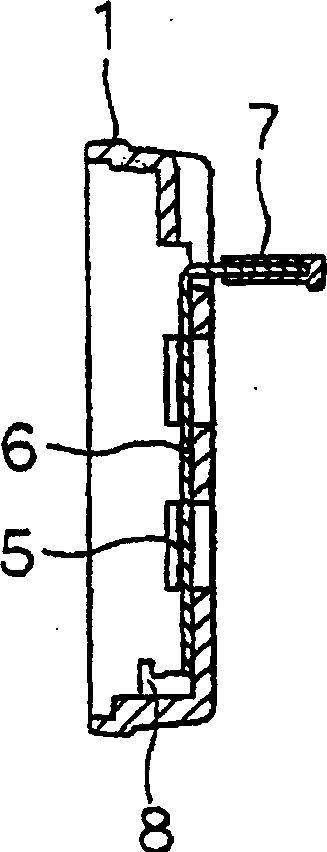

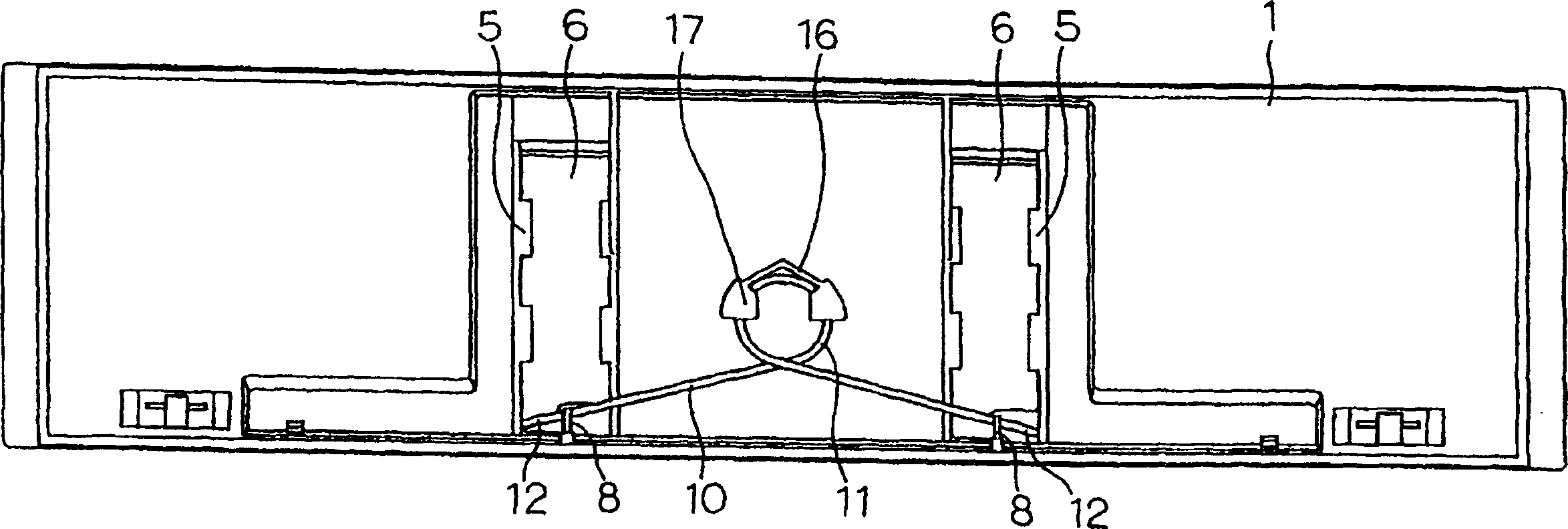

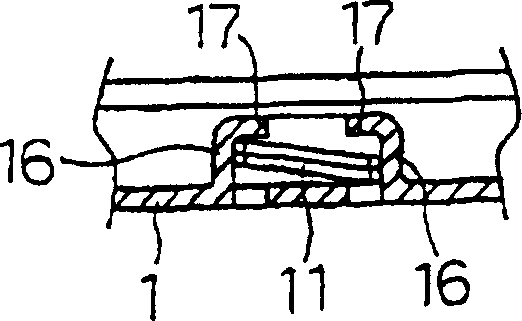

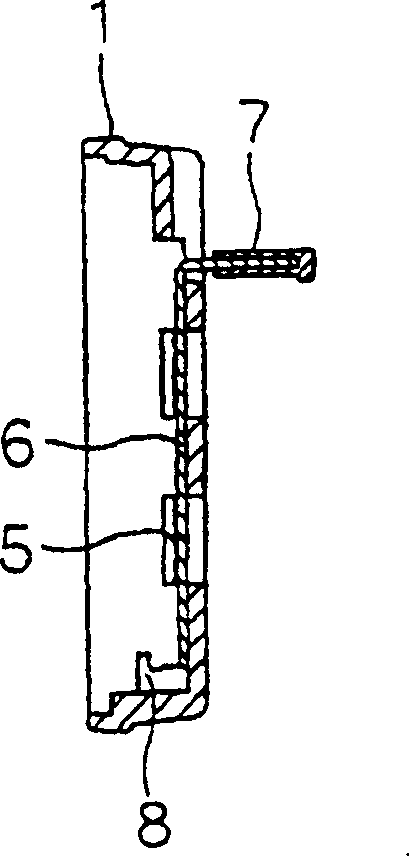

Posteriorly fitted room mirror for automobile

InactiveCN1817689AReduce parts countReduce manufacturing processOptical viewingWing mirrorEngineering

The invention relates to a posteriorly fitted rearview mirror for automobile, which comprises a posteriorly fitted rearview mirror body installed in the front of the existing rearview mirror; a reflection mirror arranged in the front of the rearview mirror body; a jaw section arranged on either the top or the bottom part of the back of the rearview mirror body; a freely movable jaw section arranged on the opposite part of the back of the rearview mirror body; a force applying device for ever-applying a force towards the jaw section to the freely movable jaw section; guide walls respectively arranged on both sides of the surface of at least one of the two jaw sections and with grooves in opposite positions; protrusions arranged on the surface of the jaw sections; and an elastic component provided with protrusions engaging with the grooves on both sides thereof and with recess portions engaging with the protrusions on the lower surface. Compared with conventional posteriorly fitted rearview mirrors, the invention has reduced number of parts and manufacturing procedures.

Owner:CAR MATE MFG

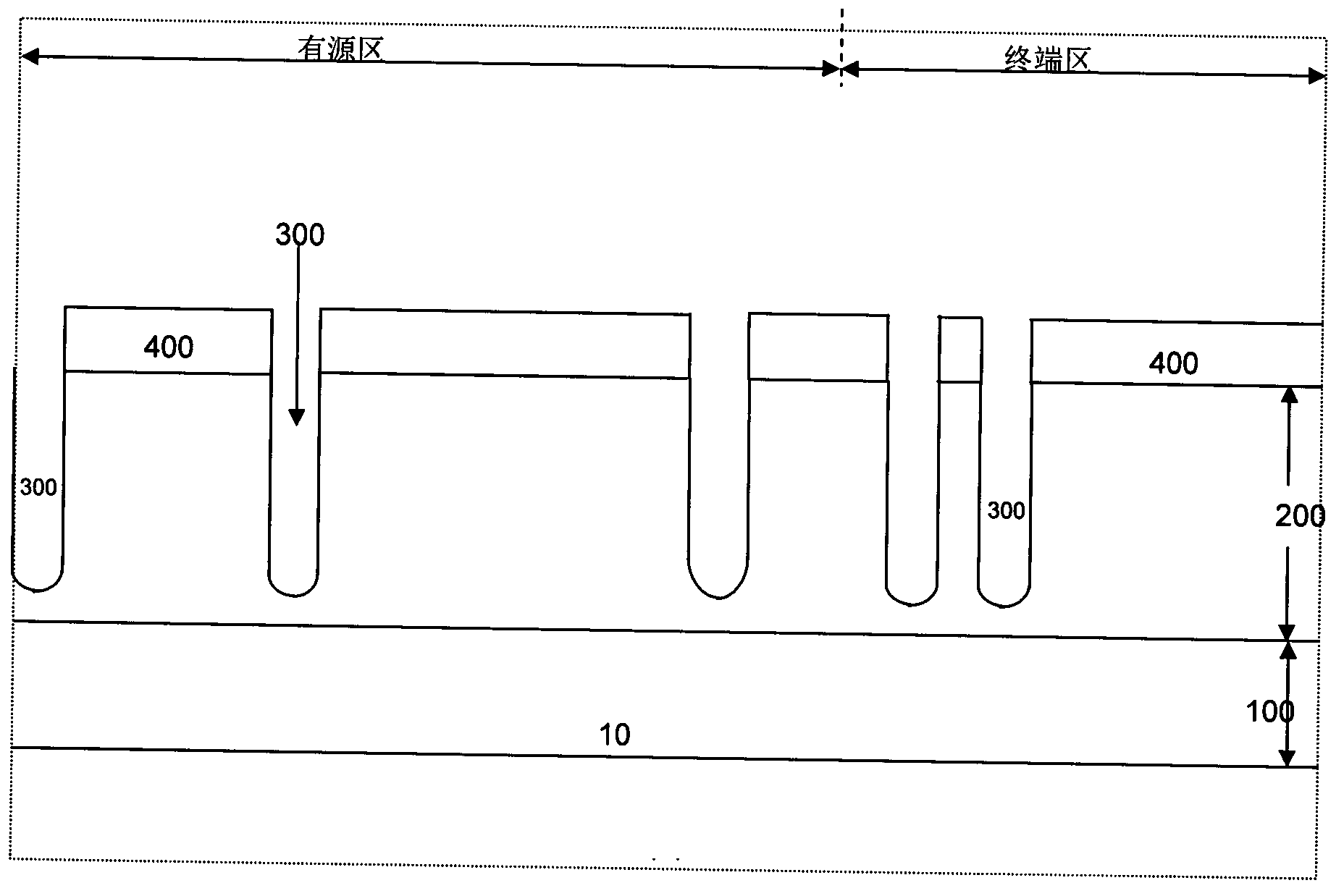

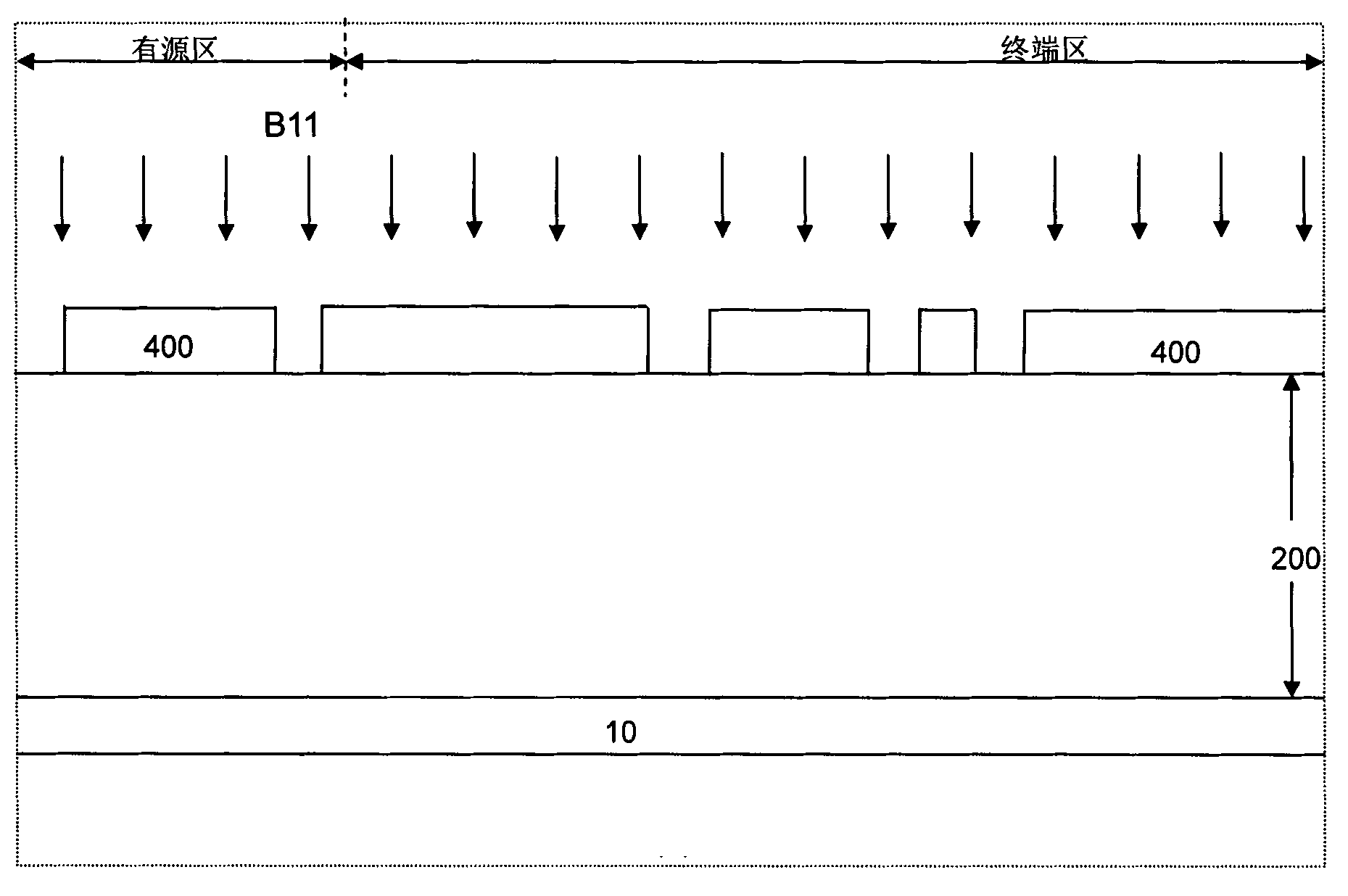

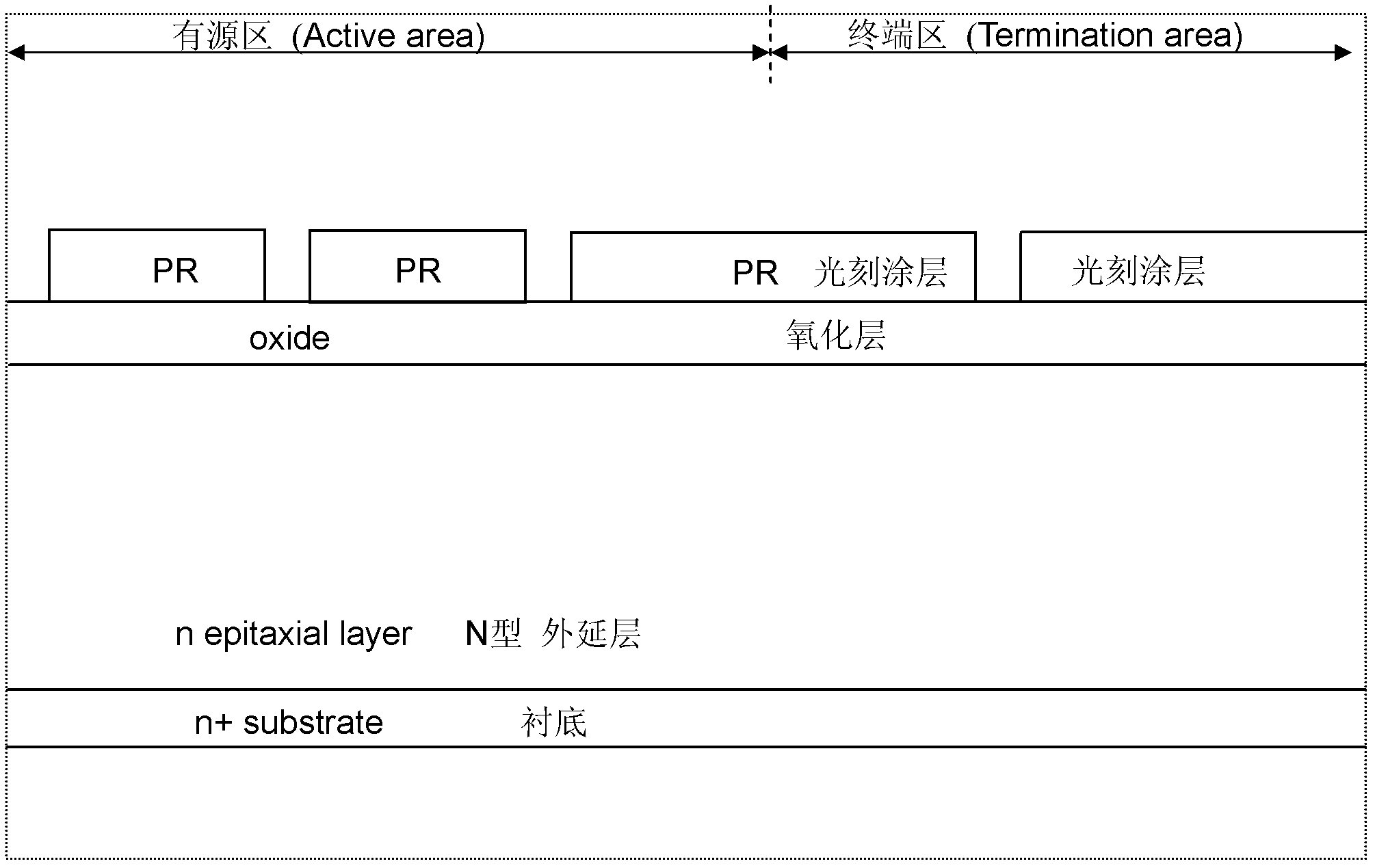

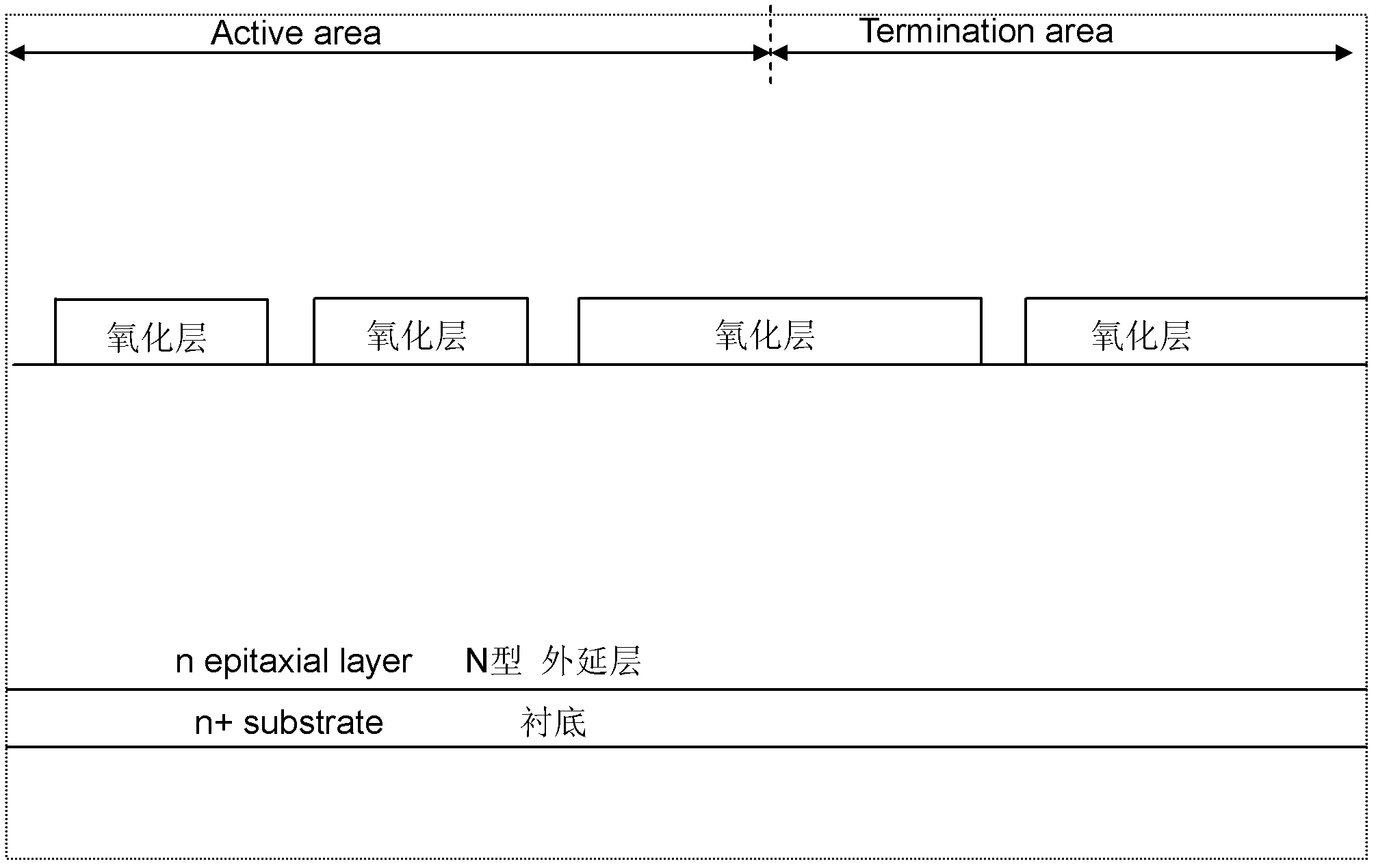

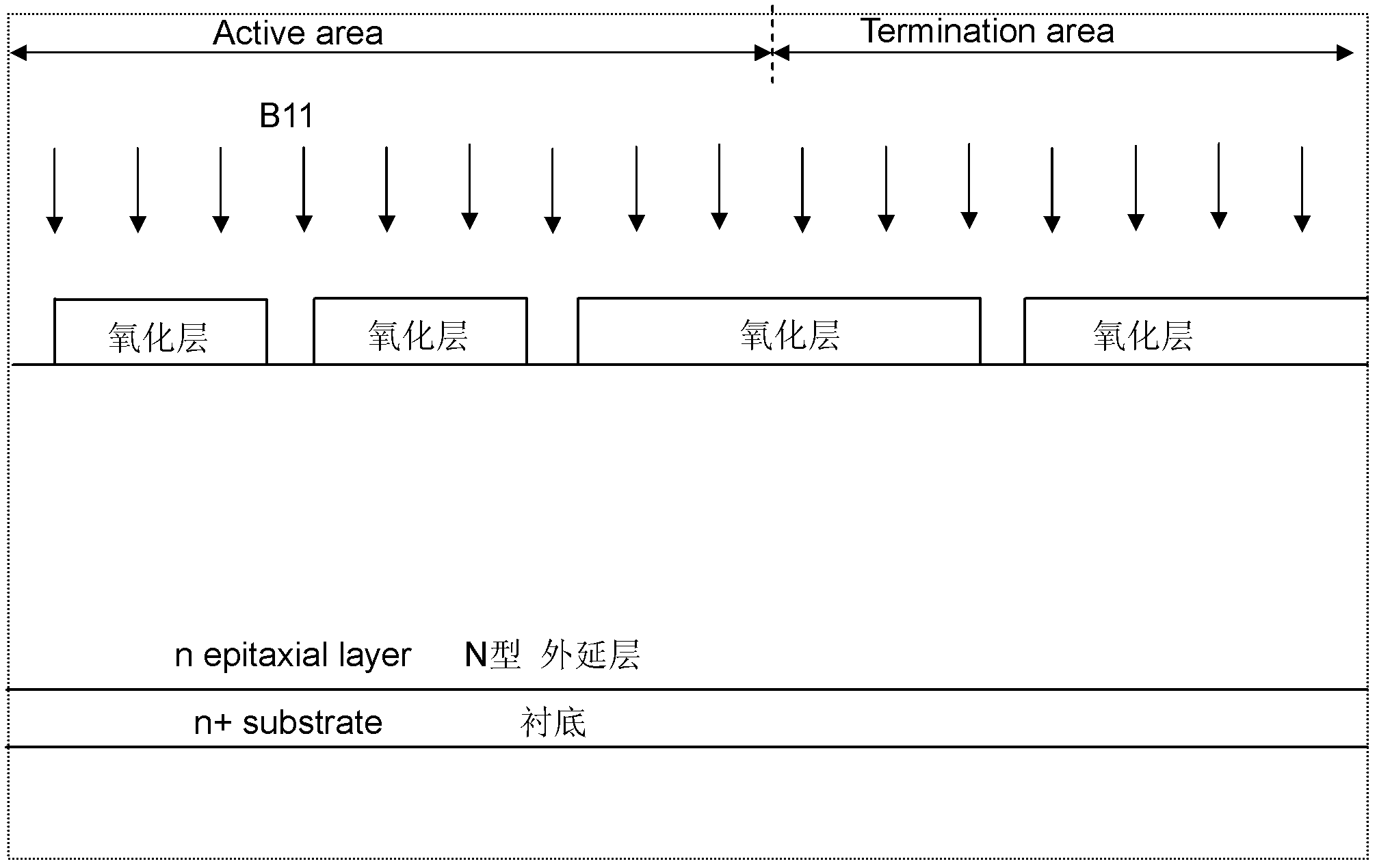

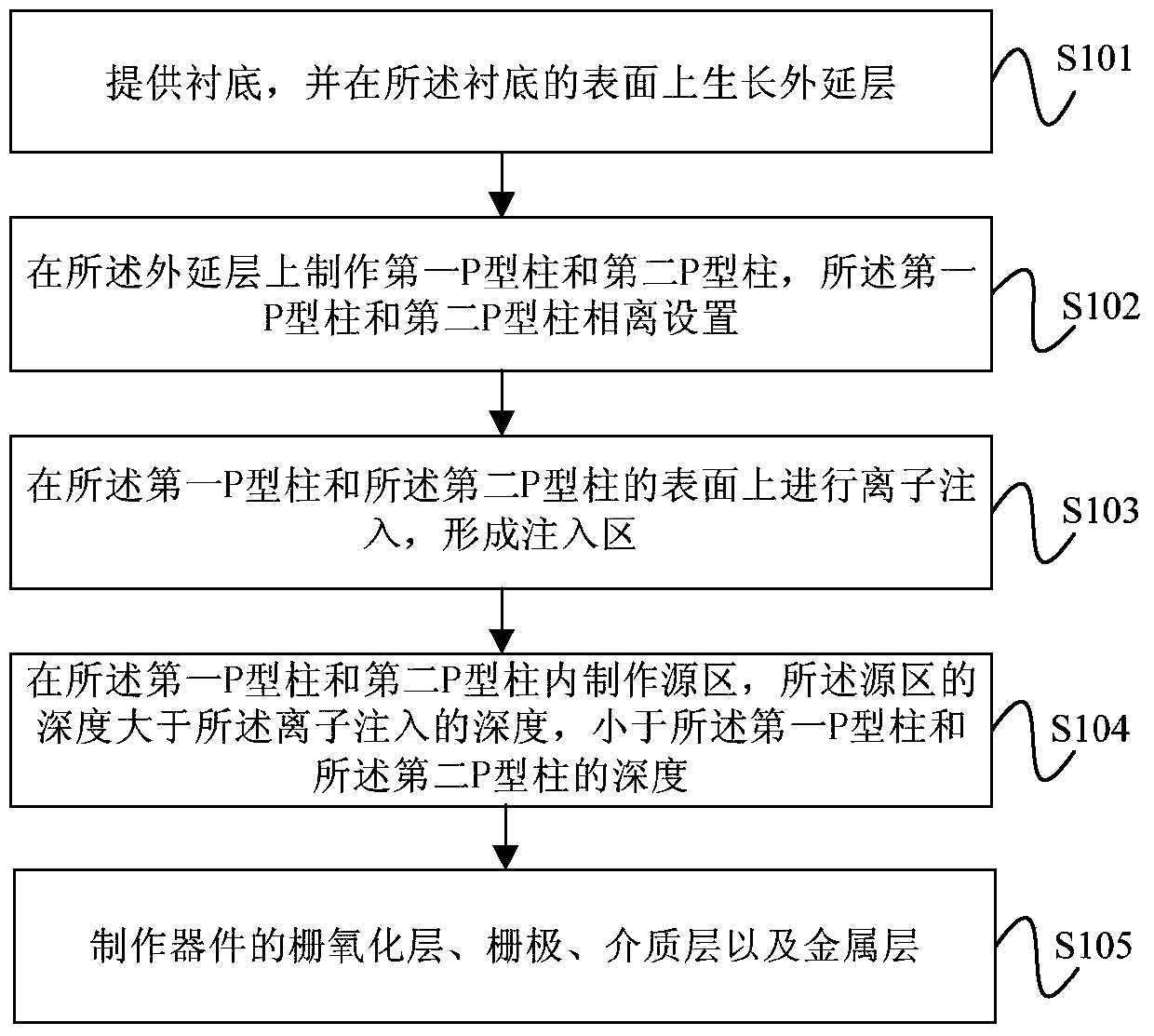

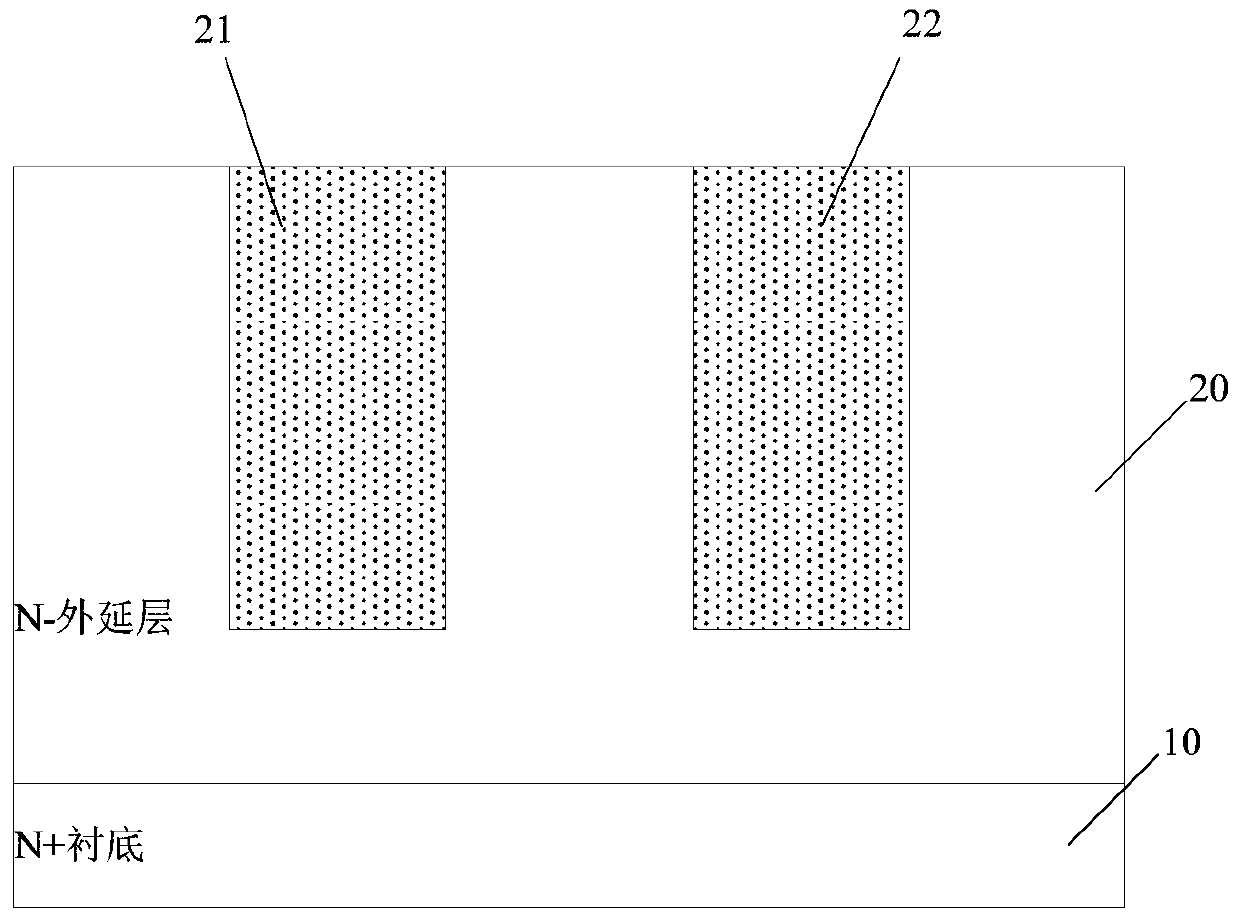

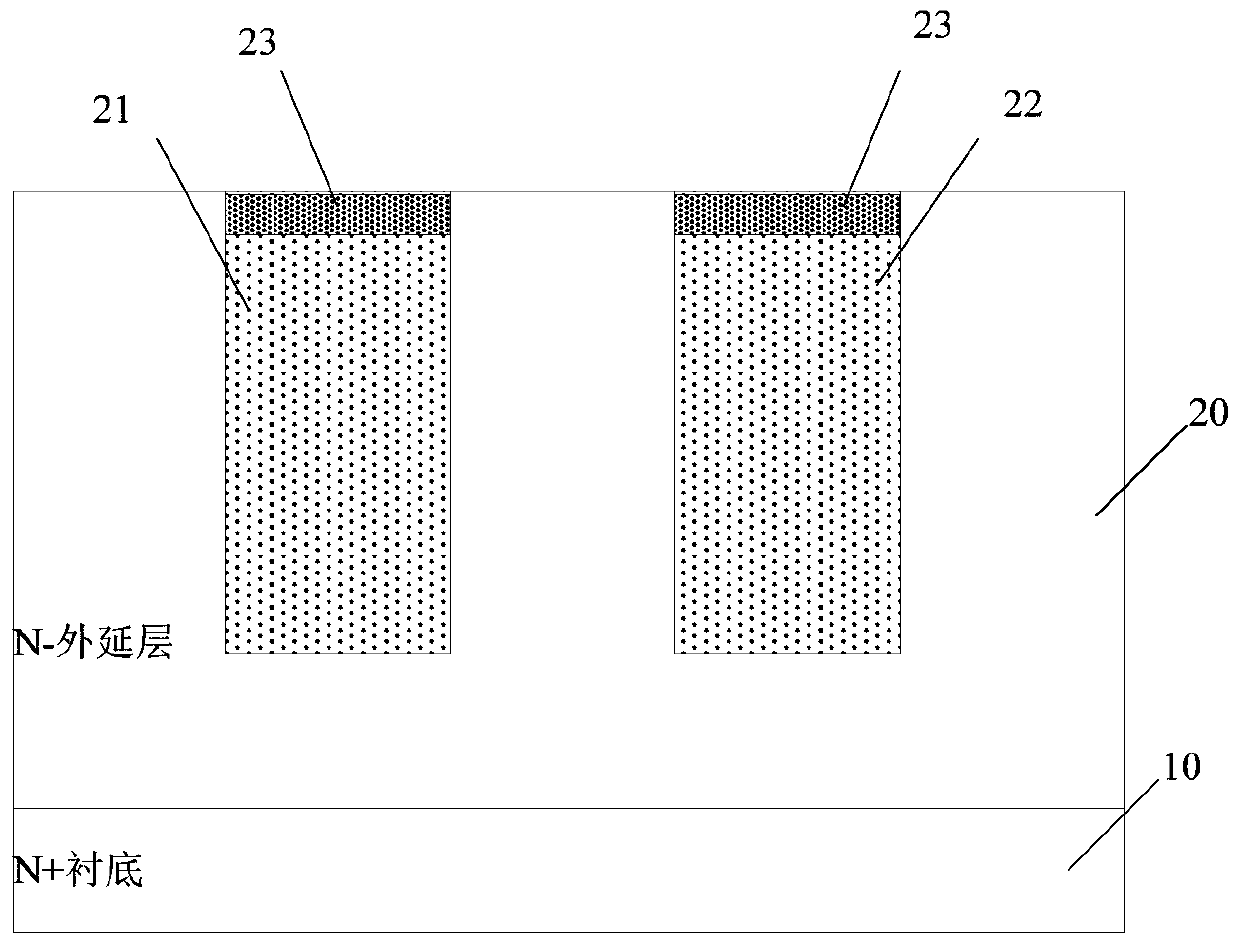

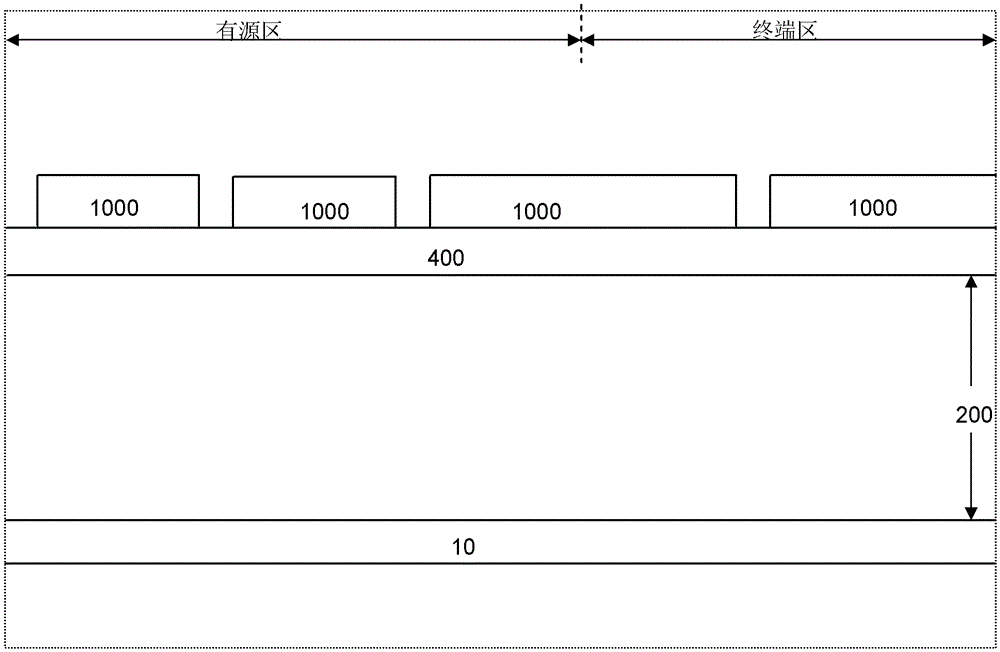

Fabrication method of super junction power device

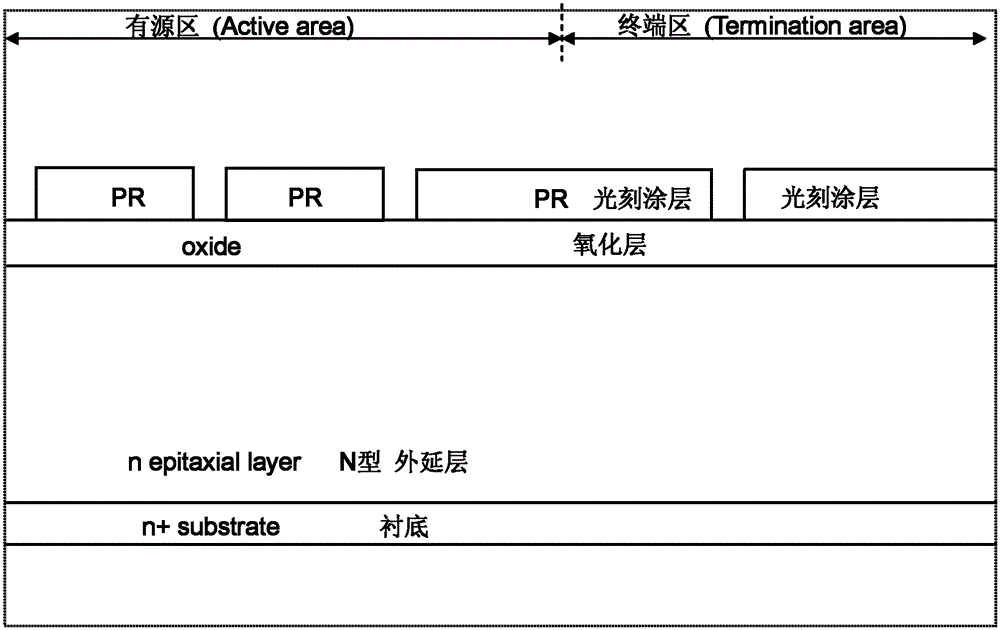

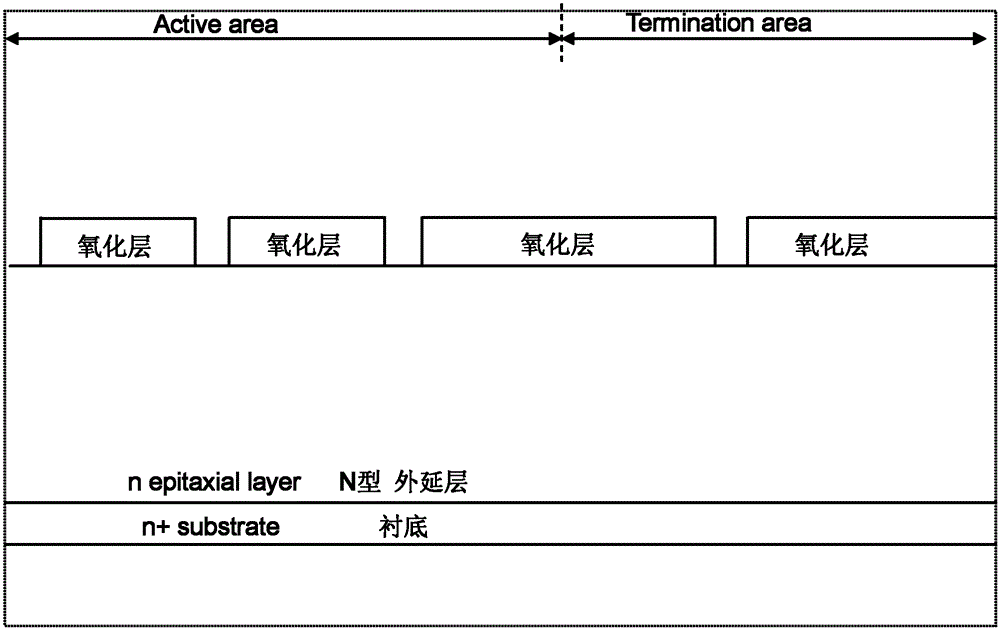

ActiveCN107346738BReduce ion concentrationReduce manufacturing costSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringGate oxide

The embodiments of the present invention provide a fabrication method of a super-junction power device. The method includes the following steps that: a substrate is provided, and an epitaxial layer is grown on the surface of the substrate; a first P-type pillar and a second P-type pillar are fabricated on the epitaxial layer; ion implantation is performed on the surfaces of the first P-type pillar and the second P-type pillar, so that ion concentration on the surfaces of the first P-type pillar and the second P-type pillar can be decreased, and the depth of the ion implantation is smaller than the depth of the first P-type pillar and the second P-type pillar; source regions are fabricated in the first P-type pillar and the second P-type pillar, the depth of the source regions is greater than the depth of the ion implantation and is smaller than the depth of the first P-type pillar and the second P-type pillar; and the gate oxide layer, gate, dielectric layer and metal layer of the device are fabricated. With the method provided by the embodiments of the present invention adopted, the problem of charge imbalance between P-type pillars and an N-type epitaxial layer caused by a high-temperature drive-in process in a conventional process can be avoided, and the withstand voltage performance of the device can be improved.

Owner:FOUNDER MICROELECTRONICS INT

Method for producing nickel powder from pure nickel sulfate solution through direct deposition

The invention provides a method for producing nickel powder from pure nickel sulfate solution through direct deposition. The method comprises the following steps: adjusting the pH value of the pure nickel sulfate solution at a concentration more than 8g / L to between 2.0 and 7.2; and taking a Pb-Ag-Ca lead base alloy as an anode and a stainless steel plate as a cathode, performing electrolysis to deposit the nickel powder on the negative plate, wherein in the electrolysis, the current density is between 1,000 and 4,000A / M2, and the temperature of electrolyte solution is between 20 and 60DEG C.The granularity of the electrolytic nickel powder prepared by the method is less than 200 meshes, and the oxygen content is lower than 0.35 percent. The method has the advantages of simple process, short process flow, low production cost, energy efficiency and environmental protection, is suitable for directly preparing the electrolytic nickel powder from the pure nickel sulfate solution, is alsosuitable for directly preparing the electrolytic nickel powder from nickel solution recovered from nickel waste and purified, has realistic significance of recycling materials and protecting the environment, and is particularly suitable for environment-friendly enterprises in which the nickel-containing waste is subjected to various links of impurity removal to obtain nickel-containing solution.

Owner:CENT SOUTH UNIV

A method for preparing trench semiconductor discrete devices

InactiveCN103219241BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantEngineering

Owner:立新半导体有限公司

A kind of preparation method of trench semiconductor power device

InactiveCN103187282BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantEngineering

The invention discloses a preparation method of a trench semiconductor power device. The preparation method of the trench semiconductor power device includes a first step of injecting dopant into an epitaxial layer arranged on a substrate for two times to form P-type base regions and N-type base regions, and conducting corrosion on the epitaxial layer to form a plurality of grid trenches; a second step of depositing interlayer mediums on the epitaxial layer, conducting the corrosion on the interlayer mediums through a contact hole mask, conducting the corrosion on the interlayer mediums and the surface of the epitaxial layer through a contact hole mask to form contact trenches, and conducting metal plugging filling on the contact trenches; and a third step of depositing a metal layer on the surface of the discrete device, conducting metal corrosion through a metal mask and forming a metal substrate layer and a connecting wire. The preparation method of the trench semiconductor power device eliminates preparation procedures of a base region mask and a source region mask, and therefore the manufacturing cost of the power device is greatly reduced. In addition, original electrical characteristics of the power device cannot be influenced. The cost-performance ratio of the power device is improved. The performance, the quality and the reliability of the trench semiconductor power device are not influenced.

Owner:立新半导体有限公司

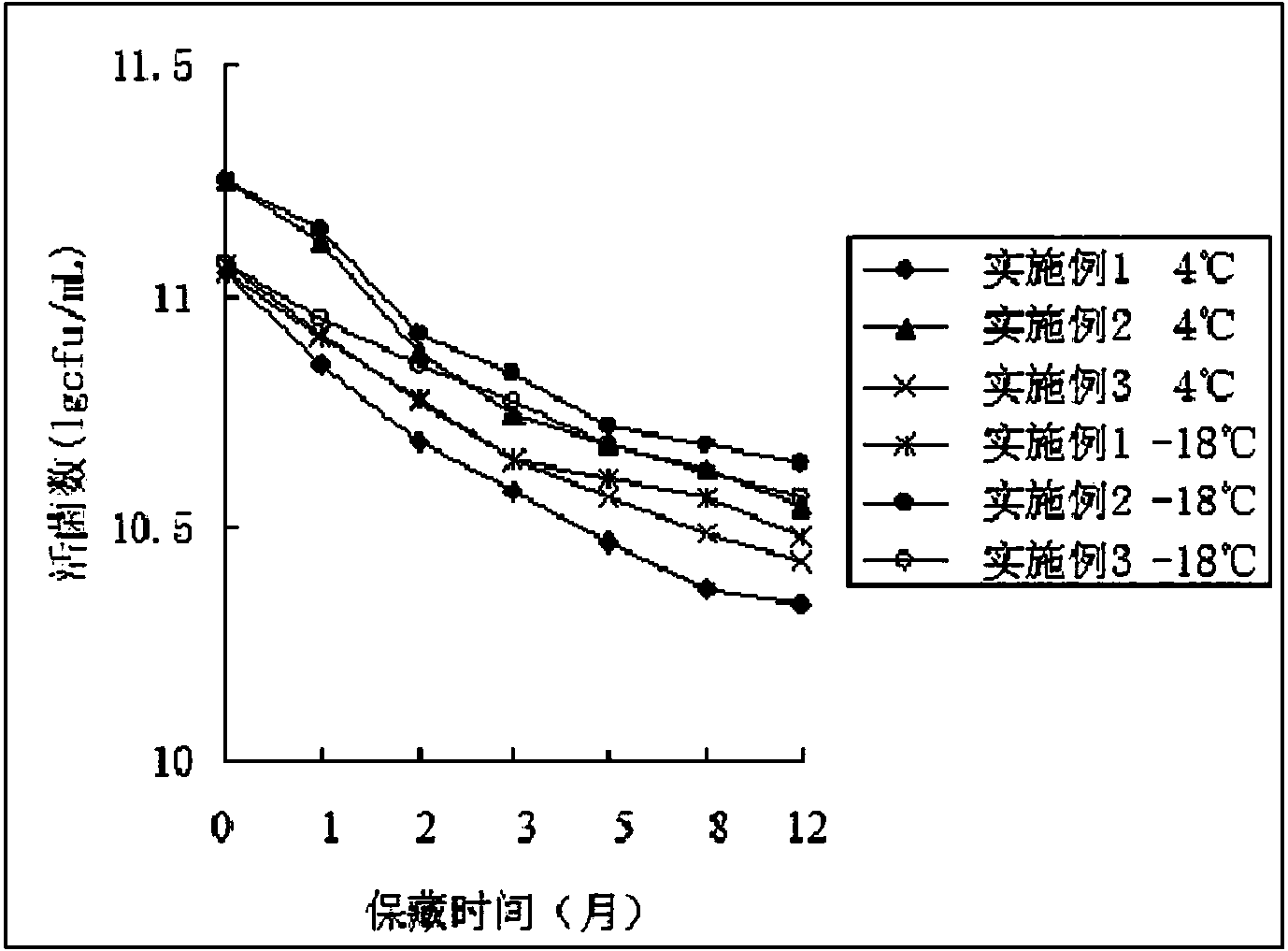

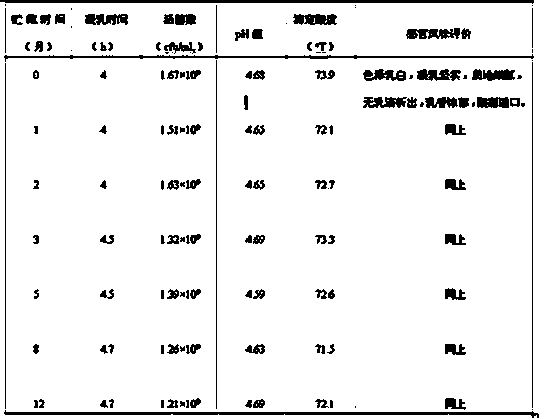

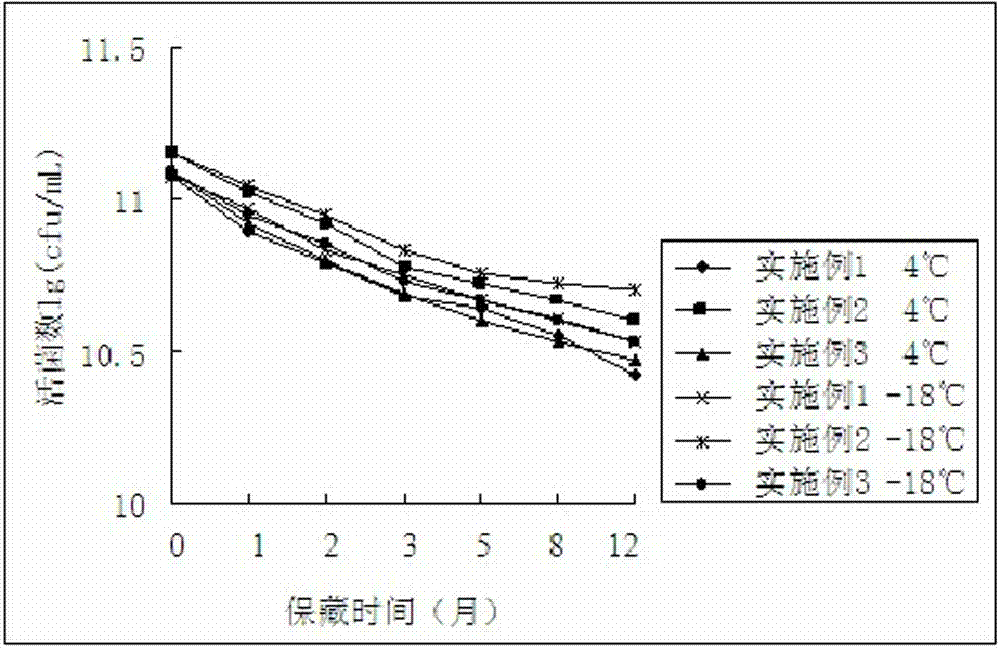

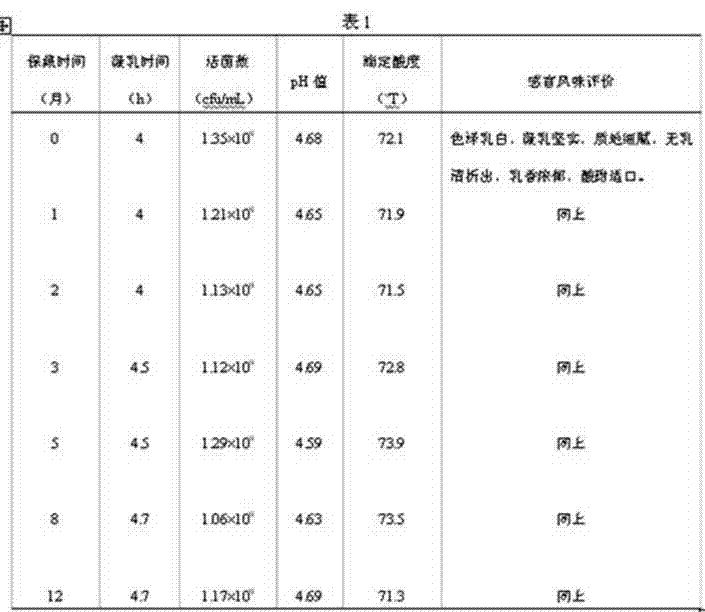

Preparation method of lactobacillus rhamnosus soybean milk direct vat set starter

ActiveCN103141722BHigh fermentation activitySmall amount of inoculumBacteriaMicroorganism based processesLactobacillus rhamnosusDissolution

The invention discloses a preparation method of lactobacillus rhamnosus soybean milk direct vat set starter. Lactobacillus rhamnosus is subjected to high-density culture by a low-price enrichment medium, centrifugal concentration and separation, mixed dissolution with high-efficiency composite protective agent and lyophilization to prepare the lactobacillus casei soybean milk direct vat set starter. According to the preparation method, the viable organism of the prepared starter is over 1*10<11>cfu / g; after the starter is sealed under normal pressure and preserved at 4 DEG C for 1 year, the content of the viable organism is still over 10<10>cfu / g, and a higher fermentation activity is stilled maintained; and soybean milk is fermented at 37 DEG C with the inoculum size being lower than one ten-thousandth, and the milk can be cured after 4 to 5 hours, wherein the soybean yoghurt product fermented by the starter has the acidity being between 70oT and 80oT, the pH value being about 4.6, and good sense and flavor. The starter can be used in the fermented dairy products industry and vegetable protein processing industry.

Owner:HEBEI AGRICULTURAL UNIV.

Array electric fluid power printing head

Owner:HUAZHONG UNIV OF SCI & TECH

A kind of preparation method of trench semiconductor power discrete device

InactiveCN103187281BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDopantP type doping

Owner:立新半导体有限公司

Automobile indoor rear-viewing mirror

Owner:CAR MATE MFG

A method for preparing trench semiconductor power discrete devices

InactiveCN103187291BOmit the preparation processReduce manufacturing costSemiconductor/solid-state device manufacturingDielectricP type doping

The invention discloses a method of preparing a trench semiconductor power discrete device. The method comprises the following steps of firstly injecting P-type doping agents into an epitaxial layer on a substrate through a trench mask to form P-type base regions, and then eroding the epitaxial layer to form a plurality of grid trenches; injecting N-type doping agents into side walls of the tops of the trenches to form N-type source regions; then, settlinginterlayer dielectric on the surface of the epitaxial layer, eroding the interlayer dielectric and the surface of the epitaxial layer to form contact trenches by means of a contact hole mask, and filling the contact trenches with metal plugs; and finally, settling a metal layer on the upper surface of the device, and conducting metal erosion through a metal mask to form a metal cushion layer and a connection line. By means of the preparing method, preparing processes of a base-region mask and a source-region mask are omitted, and therefore manufacturing cost of the device is greatly lowered; and meanwhile, original electrical characteristics of the device is not influenced, and therefore the price performance ratio of the device is increased.

Owner:立新半导体有限公司

Ternary cobalt-nickel selenide nano-sheet array electrode material and preparation method thereof

InactiveCN109003824ANo gainEasy accessMaterial nanotechnologyHybrid capacitor electrodesCapacitanceCation exchange reaction

The invention discloses a ternary cobalt-nickel selenide nanometer sheet array electrode material and a preparation method thereof, belonging to the technical field of electrode material preparation.It is prepared by the following method: Co (CH3COO) 2-4H2O is added into the mixed solvent of anisole and methanol, and the mixture is magnetically stirred to be completely dissolved; Co (CH_3COO) _ 2solution is adde into a high-pressure reaction kettle, and then that precursor template of the honeycomb nickel selenide nano-sheet array is put into the high-pressure reaction kettle, and the reaction temperature and time are controlled to obtain the ternary cobalt nickel selenide nano-sheet array, wherein the precursor template of the honeycomb nickel selenide nano-sheet array is adde into thehigh-pressure reaction kettle. The obtained electrode materials have excellent electrochemical properties at 1.0 Ag-1, the specific capacitance can reach 3917 F g-1, even at current densities up to 10A g-1, the specific capacitance can still reach 2150 F g-1. The cation exchange reaction is simple, no by-product, controllable, high efficiency and high purity. The material is suitable for supercapacitors.

Owner:ANYANG NORMAL UNIV

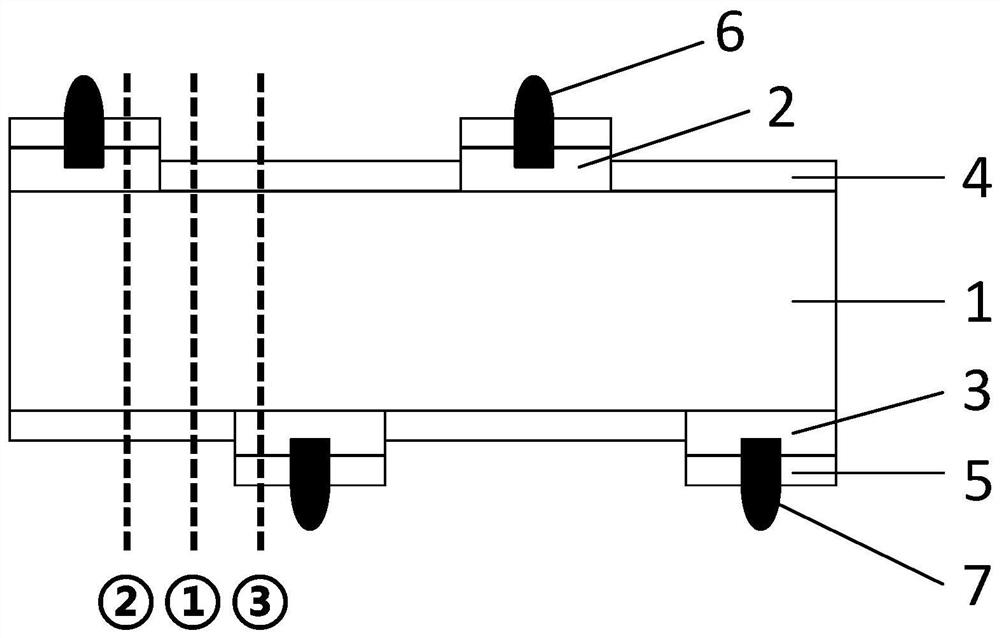

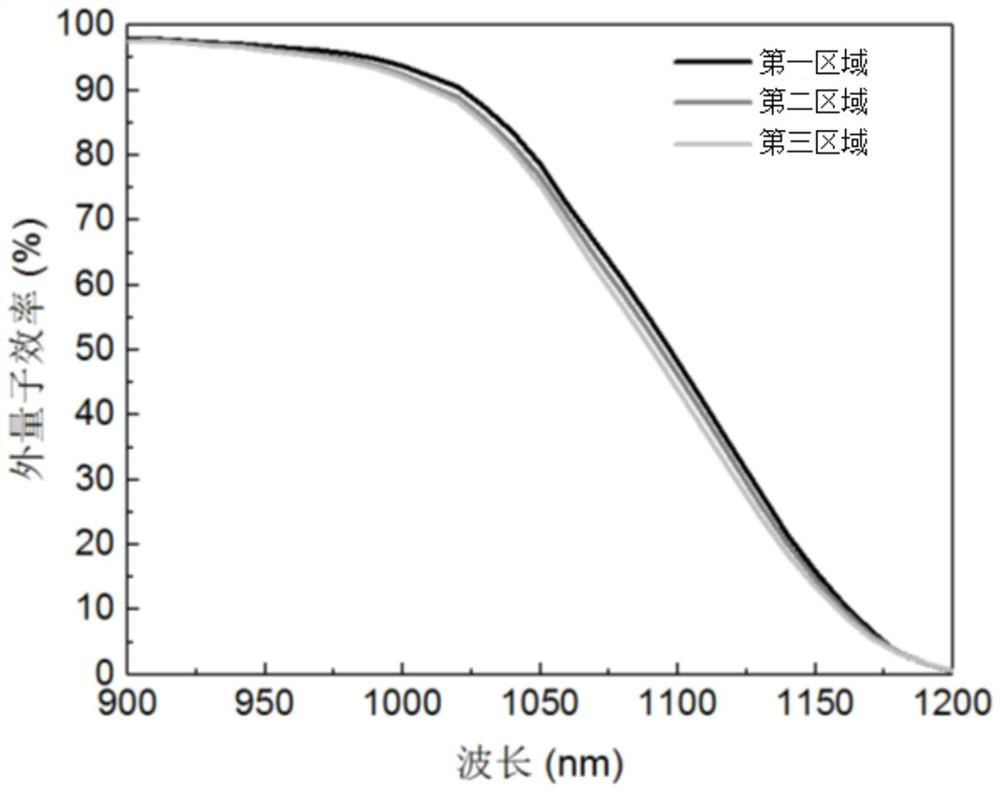

Method for testing free carrier absorption loss and battery sample

PendingCN114675199AAdapt to the requirements of mass rapid testingOmit the preparation processMaterial analysis by optical meansPhotovoltaic energy generationQuantum efficiencyParticle physics

The invention belongs to the technical field of solar cells, and provides a method for testing free carrier absorption loss and a cell sample, and the method comprises the steps: preparing a cell sample with a specific structure, the battery sample comprises a first region, a second region and a third region; the first region is provided with a first heavily-doped layer on the front surface and then a second heavily-doped layer on the rear surface; the third region is provided with a second heavily-doped layer on the front surface and then a second heavily-doped layer on the rear surface; testing the external quantum efficiency of the first area, the second area and the third area in the near-infrared band; obtaining integral current density values of the first region, the second region and the third region according to the external quantum efficiency and the AM1.5 G spectrum of the first region, the second region and the third region; and obtaining the free carrier absorption loss according to the integral current density values of the first region, the second region and the third region. The method is simpler in test, short in time consumption and low in cost, and can quickly and accurately realize quantitative detection of free carrier absorption loss.

Owner:TAIZHOU ZHONGLAI PHOTOELECTRIC TECH CO LTD

A kind of preparation method of mlcc capacitor

ActiveCN112885601BHigh bonding strengthOmit the preparation processFixed capacitor dielectricFixed capacitor housing/encapsulationCeramic compositeBarium titanate

The invention discloses a method for preparing an MLCC capacitor, comprising: (1) coating a slurry formed of plastic particles and ceramic particles on copper foil / aluminum foil, and drying to obtain a copper foil composite layer / aluminum foil composite layer; 2) Lay the copper foil composite layer and the aluminum foil composite layer together at intervals, heat to the softening point of the plastic, and then roll to obtain a multilayer ceramic composite body; (3) place one end of the multilayer ceramic composite body into dilute hydrochloric acid to dissolve the aluminum foil near the end face, and leave the copper foil; put the other end face into concentrated nitric acid to dissolve the copper foil near the end face, leave the aluminum foil, and polish to remove the aluminum passivation layer; then, the two end faces Solder with external electrodes with tin respectively, so that the copper foils are connected with each other and the aluminum foils are connected with each other as a whole to obtain an MLCC capacitor. The preparation method of the MLCC capacitor of the present invention not only simplifies the process, saves energy, but also avoids quality problems such as improper sintering of nickel powder and barium titanate powder, resulting in short circuit and open circuit.

Owner:SUZHOU CHUANGHAO NEW MATERIAL TECH CO LTD

Preparation method of lactobacillus casei soybean milk direct vat set starter

ActiveCN103141723BHigh fermentation activityLow costBacteriaMicroorganism based processesHigh densityDissolution

The invention discloses a preparation method of lactobacillus casei soybean milk direct vat set starter. Lactobacillus casei is subjected to high-density culture by a low-price enrichment medium, centrifugal concentration and separation, mixed dissolution with high-efficiency composite protective agent and lyophilization to prepare the lactobacillus casei soybean milk direct vat set starter. According to the preparation method, the viable organism of the prepared starter is over 1*10<11>cfu / g; after the starter is sealed under normal pressure and preserved at 4 DEG C for 1 year, the content of the viable organism is still over 10<10>cfu / g, and a higher fermentation activity is stilled maintained; and soybean milk is fermented at 37 DEG C with the inoculum size being lower than one ten-thousandth, and the milk can be cured after 4 to 5 hours, wherein the soybean yoghurt product fermented by the starter has the acidity being between 70 oT and 80oT, the pH value being about 4.6, and good sense and flavor. The starter can be used in the fermented dairy products industry and vegetable protein processing industry.

Owner:HEBEI AGRICULTURAL UNIV.

High flatness integrated solar power integral roof and rapid integration method

ActiveCN104372899BEasy to operateSave on packaging materialsPhotovoltaic supportsRoof covering using slabs/sheetsWater leakageWater channel

Owner:烟台鼎城新能源光伏有限公司

Packaging substrate as well as manufacturing method

ActiveCN101989592BSimple manufacturing processAvoid wastingSemiconductor/solid-state device detailsSolid-state devicesEngineeringDielectric layer

The invention discloses a packaging substrate as well as a manufacturing method and a base material thereof. The manufacturing method of the packaging substrate comprises the following steps: two metal layers are mutually laminated, and a dielectric layer is utilized to clad the two metal layers; next, layer increasing line structures are respectively formed at the two sides of the dielectric layer; and finally, the layer increasing line structures at the two sides of the dielectric layer are separated along the interface of the two metal layers so that two packaging substrates are formed. Inthe invention, the adhesion characteristics of the dielectric layer is utilized so that the two metal layers in the middle cannot be separated in the course of forming the layer increasing line structures in the initial stage, and the dielectric layer part around the two metal layers is cut off to successfully separate the two metal layers so that the manufacturing process is simplified, and the two metal layers in the middle can form a line layer, a metal lug or a supporting structure through the pattering manufacturing process and have no waste.

Owner:UNIMICRON TECH CORP