Preparation method for groove semiconductor discrete device

A discrete device and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of complex steps, poor terminal structure of semiconductor devices, and difficult to generate, so as to reduce manufacturing costs and increase performance prices. the effect of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

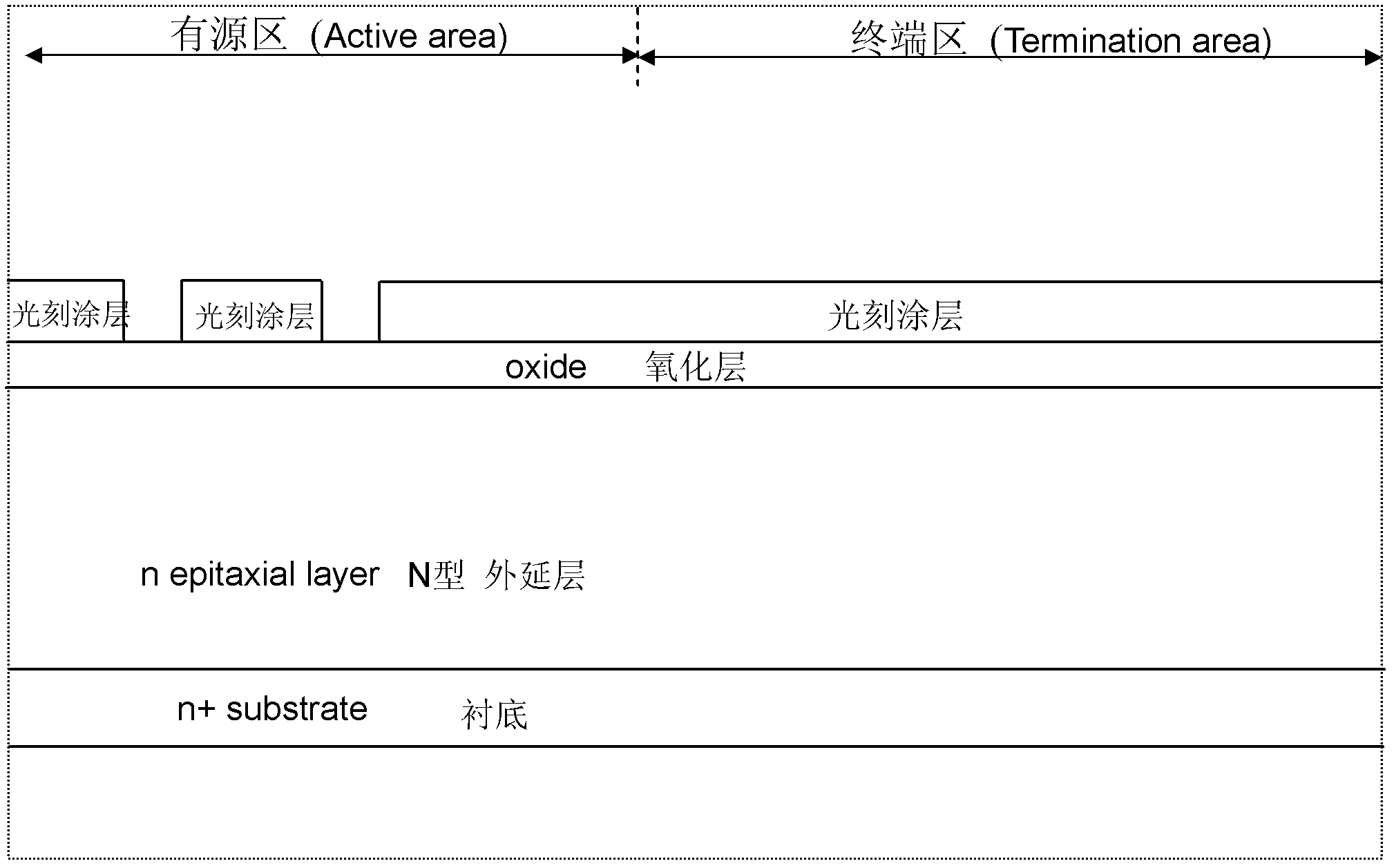

[0068] Such as figure 1 As shown, the epitaxial layer is placed above the substrate. First, an oxide layer (a hard oxide mask with a thickness of 0.3um to 1.5um) is formed on the epitaxial layer by deposition or thermal growth, and then a layer of oxide is deposited on the oxide layer. A photolithographic coating is then patterned through a trench mask to expose portions of the oxide layer.

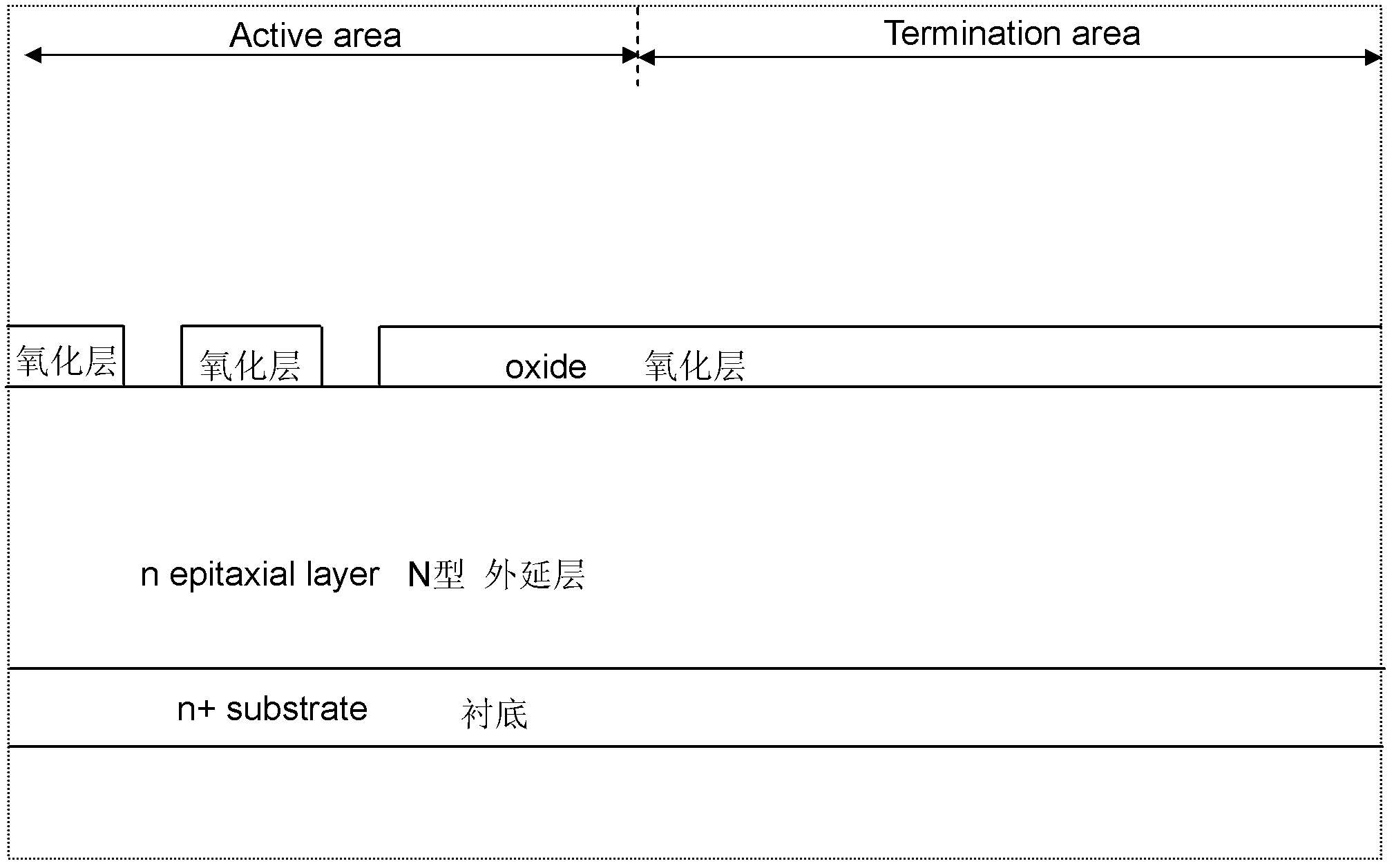

[0069] Such as figure 2 As shown, after dry etching the oxide layer exposed by patterning the trench mask, the epitaxial layer is exposed, and then the photolithographic coating is removed.

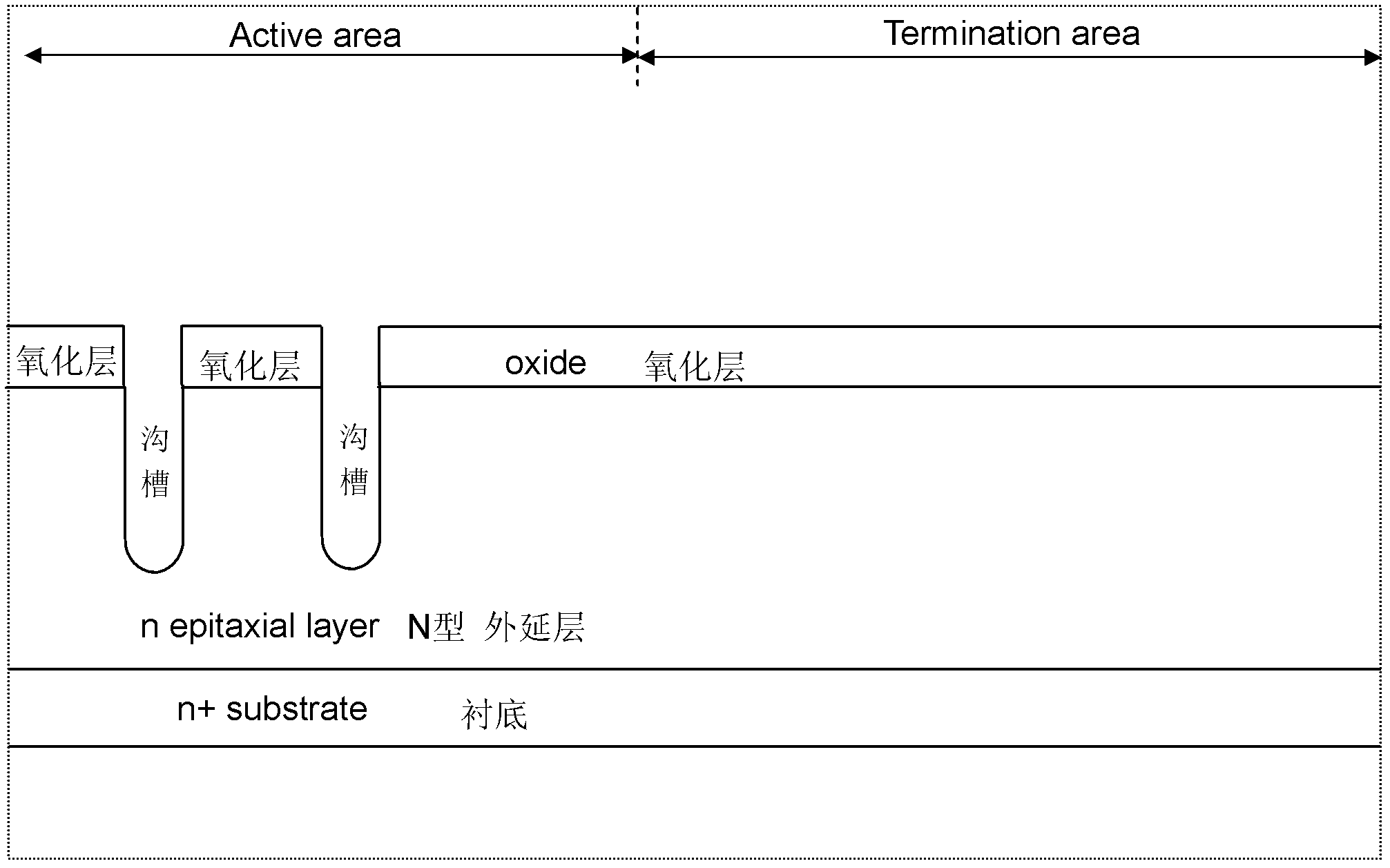

[0070] Such as image 3 As shown, a trench (1.0um to 7.0um in depth and 0.2um to 2.0um in width) is formed by etching, and the trench extends to the N-type epitaxial layer.

[0071] Such as Figure 4 As shown, after the trench is formed, the trench is sacrificially oxidized (10 minutes to 100 minutes at a temperature of 1000° C. to 1200° C.) to eliminate the silicon layer damaged by the plasma d...

Embodiment 2

[0088] It is an embodiment of the present invention.

[0089] Step and embodiment 1 are by Figure 1 to Figure 17 same, then:

[0090] Such as Figure 20 As shown, a layer of LPCVD oxide layer is deposited.

[0091] Such as Figure 21 As shown, the oxide layer is then dry-etched to remove the oxide layer on the opening and expose the epitaxial layer on the opening of the interlayer dielectric.

[0092] Such as Figure 22 As shown, the epitaxial layer containing the dopant is etched through the opening of the interlayer dielectric, so that the contact hole trench (0.4um to 1.0um in depth and 0.2um to 1.2um in width) passes through the N-type source region Enter the P-type base region, and then inject a P-type high dopant into the contact hole trench (dopant concentration is 10 14 up to 5×10 15 / cm 3 ) to reduce the contact resistance between the P-type base region and the metal plug, which effectively increases the safe use area of the device. Such as Figure 23 As ...

Embodiment 3

[0095] It is a variant of the present invention.

[0096] Step and embodiment 1 are by Figure 1 to Figure 17 same, then:

[0097] Such as Figure 24 As shown, a layer of LPCVD oxide layer is deposited, and the opening width of the contact hole mask in the interlayer dielectric is sealed from 0.2um to 0.6um. The width of the sealed opening can be 0.2um, or 0.3um um or 0.4um or 0.5um or 0.6um, depending on the preparation method, and then dry-etch the oxide layer to remove the oxide layer in the unsealed interlayer dielectric openings, exposing the Epitaxial layer: Etching the epitaxial layer containing dopants through opening holes in the interlayer dielectric, so that the contact hole trench (0.4um to 1.0um in depth and 0.2um to 1.0um in width) passes through the N-type source region Enter the P-type base region, and then inject a P-type high dopant into the contact hole trench (dopant concentration is 10 14 up to 5×10 15 / cm 3 ) to reduce the contact resistance between...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More