Packaging substrate as well as manufacturing method

A technology for packaging substrates and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of complexity, packaging substrate discarding, release layer or adhesive layer waste manufacturing process, etc., to avoid waste , improve the yield rate, and omit the effect of the manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0094] see Figure 2A to Figure 2F , is a schematic cross-sectional view of the first embodiment of the packaging substrate and its manufacturing method of the present invention.

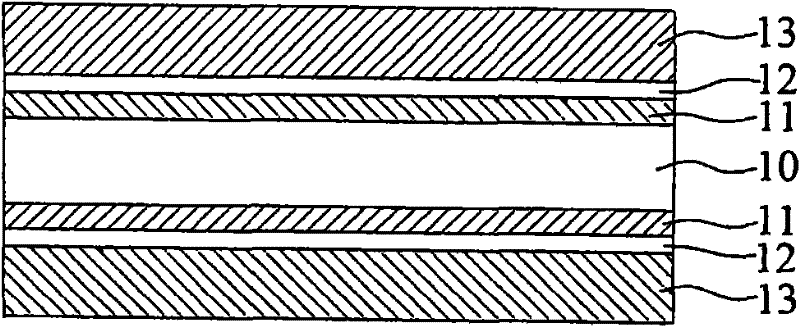

[0095] Such as Figure 2AAs shown, firstly, two first metal layers 20a, 20b are respectively provided with opposite first surfaces 201a, 201b and second surfaces 202a, 202b and are superimposed with the first surfaces 201a, 201b. The first auxiliary dielectric layer 21a, 21b on the second surface 202a, 202b of the first metal layer 20a, 20b, and the two second metal layers respectively disposed on the exposed surface of the first auxiliary dielectric layer 21a, 21b Layers 22a, 22b, and the second metal layer 22a, 22b may be thicker than the first metal layer 20a, 20b to provide sufficient rigidity.

[0096] In this embodiment, the first surface 201a, 201b may be a smooth surface, and the second surface 202a, 202b may be a rough surface.

[0097] Such as Figure 2B As shown, these first metal lay...

no. 2 example

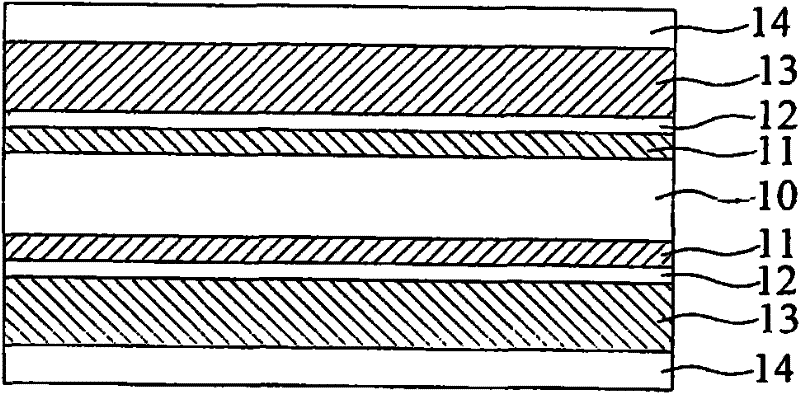

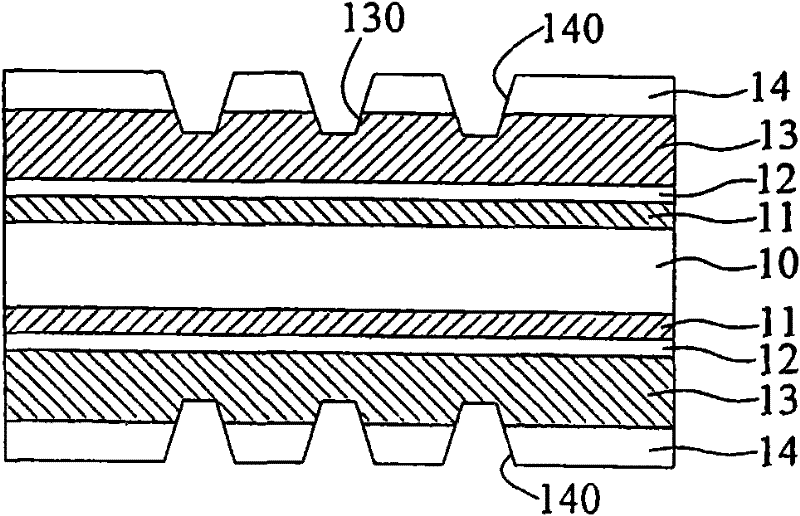

[0106] see Figure 3A to Figure 3D , is a schematic cross-sectional view of a second embodiment of the packaging substrate and its manufacturing method of the present invention.

[0107] Such as Figure 3A shown, continued from Figure 2C In the manufacturing method, the first circuit layer 232a, 232b of the outermost layer of the build-up structure 23a, 23b also has a plurality of first electrical contact pads 234a, 234b; and then on the outermost layer of the build-up structure 23a, 23b Form the first insulating protective layers 25a, 25b, such as solder resist layers, and the first insulating protective layers 25a, 25b are respectively formed with a plurality of first insulating protective layers correspondingly exposing each of the first electrical contact pads 234a, 234b. Layer openings 250a, 250b.

[0108] Such as Figure 3B As shown, the trimming is along the edges of the monolithic structure, and the trimming edge 24 passes through the first metal layer 20a, 20b. ...

no. 3 example

[0112] see Figure 4A to Figure 4F , is a schematic cross-sectional view of the third embodiment of the packaging substrate and its manufacturing method of the present invention, wherein, the Figure 4E' and Figure 4F' It is another implementation form of this embodiment.

[0113] Such as Figure 4A shown, continued from Figure 2B According to the manufacturing method, the second metal layer 22a, 22b is subjected to a patterned manufacturing process to form inner layer circuit layers 301a, 301b, and a plurality of electrical connections to the inner layer circuit layers are formed in the first auxiliary dielectric layer 21a, 21b layers 301a, 301b and the inner layer conductive blind holes 302a, 302b of the first metal layer 20a, 20b, and build-up structures 23a, 23b are formed on the first auxiliary dielectric layer 21a, 21b and the inner layer circuit layer 301a, 301b , the build-up structure 23a, 23b includes at least one first dielectric layer 231a, 231b, a first circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More