A kind of preparation method of trench semiconductor power device

A power device and semiconductor technology, applied in the field of trench semiconductor power device preparation, can solve problems such as complex steps, poor device breakdown voltage and reliability, and poor terminal structure of semiconductor devices, so as to reduce manufacturing costs and increase performance and price Compared with the effect of omitting the preparation process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

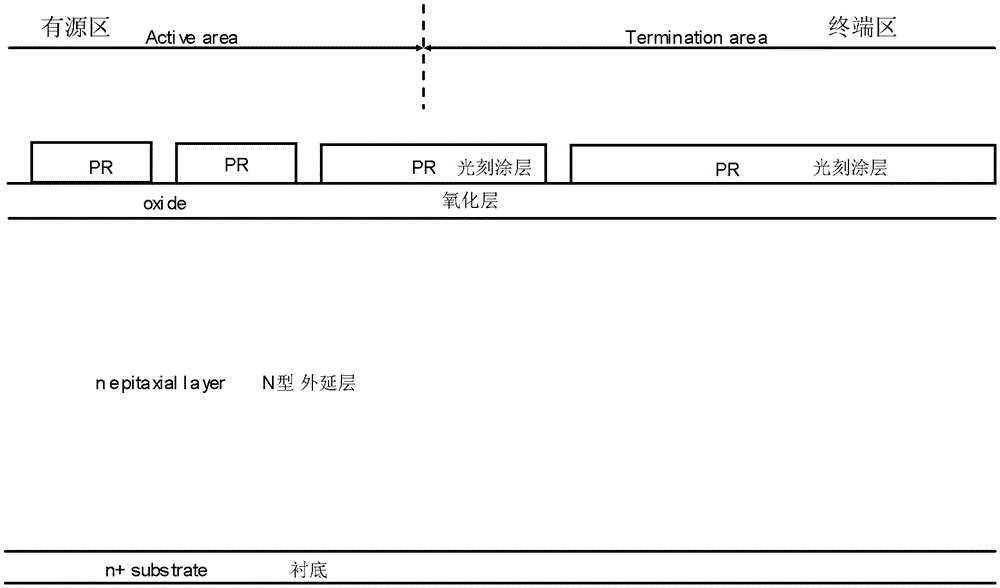

[0076] Such as figure 1 As shown, the N-type epitaxial layer is grown above the substrate. First, an oxide layer (hard oxide mask with a thickness of 0.3 μm to 1.5 μm) is formed on the epitaxial layer by deposition or thermal growth, and then deposited on the oxide layer. A photolithographic coating is then patterned through a trench mask to expose portions of the oxide layer.

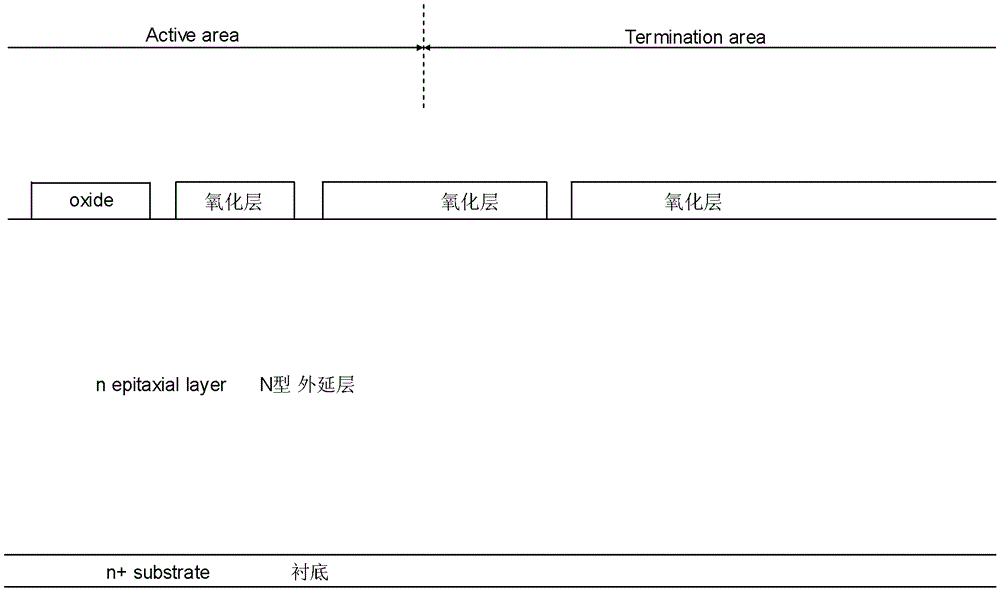

[0077] Such as figure 2 As shown, after dry etching the oxide layer exposed by forming the pattern of the trench mask, the epitaxial layer is exposed, and a plurality of trench mask openings are formed on the oxide layer, and the opening width of the plurality of trench masks is different. Again, the width ranges from 0.2 μm to 2.0 μm, and then the photoresist coating is removed.

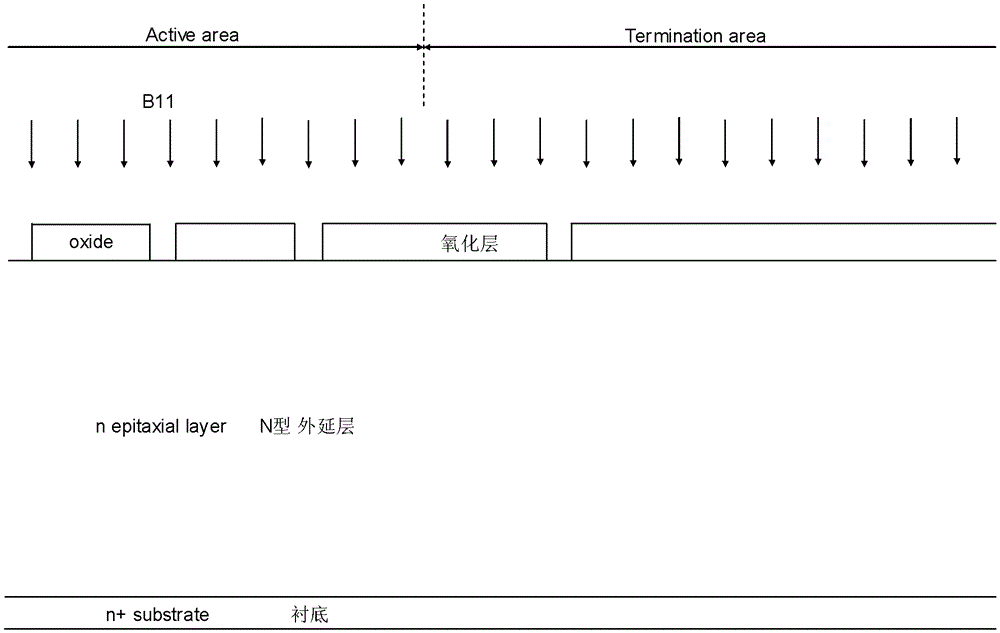

[0078] Such as image 3 As shown, implant P-type dopants on the surface of the device (the dose is 8e12 / cm 3 to 2e14 / cm 3 ), the part covered by the oxide layer is not implanted, and the part not covered by the oxide l...

Embodiment 2

[0090] Such as Figure 14a , 14b As shown, a thin oxide layer (padoxide with a thickness of 0.01 μm to 0.03 μm) is formed on the epitaxial layer by deposition or thermal growth, and a layer of polysilicon (0.5 μm to 1.2 μm in thickness) and a layer of polysilicon are deposited on it. layer silicon nitride (thickness 0.02μm to 0.2μm), such as Figure 15a As shown, a photoresist coating is deposited on the outermost surface, and then a part of the silicon nitride layer is exposed by patterning through a trench mask.

[0091] Such as Figure 15b As shown, after dry etching the part of the silicon nitride layer exposed by forming the pattern of the trench mask, dry etching is performed on the polysilicon exposed after the dry etching of the silicon nitride layer until the oxide pad layer under the polysilicon is exposed, The photoresist coating is then removed.

[0092] Such as Figure 16 As shown, implant P-type dopants on the surface of the device (the dose is 8e12 / cm 3 to...

Embodiment 3

[0107] The technical scheme of the present embodiment is roughly the same as that of embodiment 1, and its difference only lies in:

[0108] In the above example 1 Figure 7 Before etching the trench, deposit an oxide layer and seal the trench mask openings in the oxide layer with a width ranging from 0.2 μm to 0.6 μm. The sealed opening width can be 0.2 μm, Or 0.3μm or 0.4μm or 0.5μm or 0.6μm, depending on the preparation method. The advantage of this step is that some trench mask openings are implanted with P-type and N-type dopants but not opened. Out of the trench, the terminal structure of the device is better, so the breakdown voltage of the device is higher and more stable, and then the oxide layer is dry-etched to remove the oxide layer on the opening, exposing the epitaxial layer on the opening; At this time, only those openings that are not sealed by the precipitated oxide layer are opened. The trench (1.0μm to 7.0μm in depth and 0.2μm to 2.0μm in width) passes thro...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More