GaN-based enhancement/depletion mode heterojunction field effect transistor with buried gate structure

A heterojunction field effect, gallium nitride-based technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of material reliability, difficulty in realizing P-type GaN materials, and high activation energy, so as to avoid disadvantages effect, high maximum saturation leakage current, simple manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

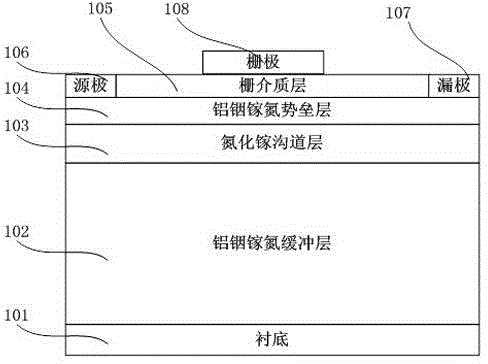

[0037] figure 1 It is a prior art GaNHFET structure, mainly including substrate 101, aluminum indium gallium nitride (Al x In y Ga z N) buffer layer 102, gallium nitride (GaN) channel layer 103, aluminum indium gallium nitride (Al x In y Ga z N) Barrier layer 104, gate dielectric layer 105, aluminum gallium nitride (Al x In y Ga z N) The source electrode 106 and the drain electrode 107 formed on the barrier layer 104, and the gate electrode 108 formed on the barrier dielectric layer 105, wherein the source electrode 106 and the drain electrode 107 are combined with aluminum indium gallium nitride (Al x In y Ga z N) The barrier layer 104 forms an ohmic contact, and the gate 108 forms a Schottky contact with the gate dielectric layer 105 .

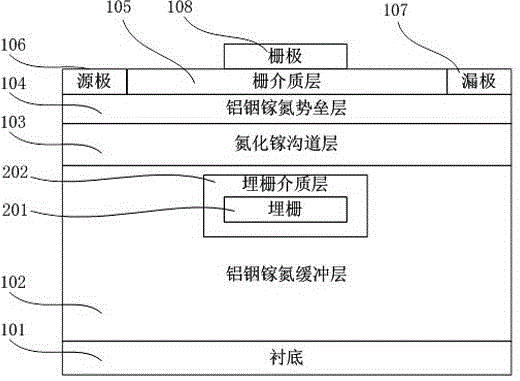

[0038] figure 2 The structure schematic diagram of GaN-based enhanced depletion heterojunction field effect transistor with buried gate structure provided by the present invention mainly consists of substrate 101, AlInGaN buffer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More