Method for Compensating Wafer Stress in 3d NAND Hybrid Bonding Process

A hybrid bond and wafer technology, applied in the manufacture of electrical components, circuits, semiconductor/solid-state devices, etc., can solve the problems of interface dislocation, uneven deformation, bonding failure, etc., to reduce the dislocation, improve the bonding power, Avoid damaging effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

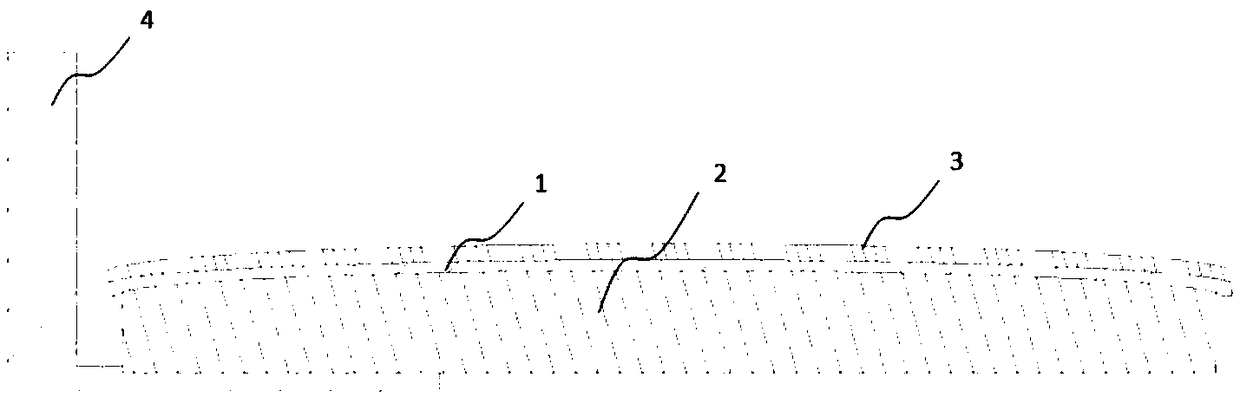

[0033] Exemplary embodiments of the present disclosure will be described in more detail below with reference to the accompanying drawings. Although exemplary embodiments of the present disclosure are shown in the drawings, it should be understood that the present disclosure may be embodied in various forms and should not be limited by the embodiments set forth herein. Rather, these embodiments are provided for more thorough understanding of the present disclosure and to fully convey the scope of the present disclosure to those skilled in the art.

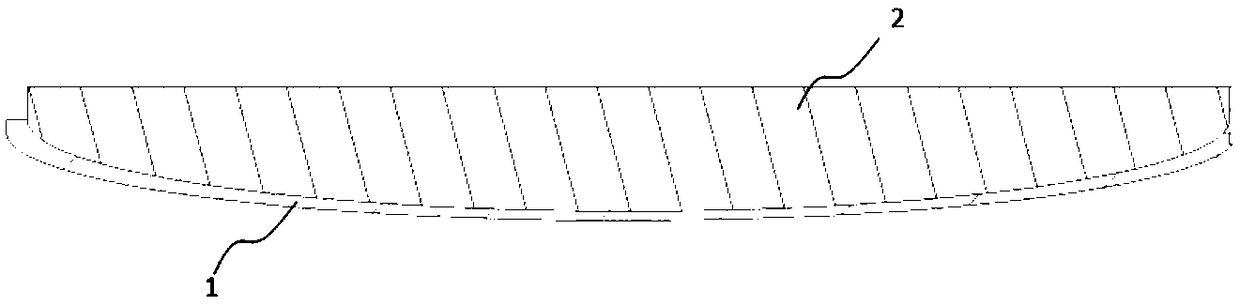

[0034] In the semiconductor manufacturing process, a wafer 1 is provided first, at this stage, the wafer 1 is flat, however when deep trench capacitors are formed on the front side of the wafer 1, the material of the deep trench capacitors is deposited under high temperature conditions And has a different coefficient of thermal expansion from the wafer 1 . When wafer 1 cools, the material filling the deep trench capacitors shrinks ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More