Semiconductor package

A semiconductor and active surface technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as high packaging failure rate and collapse, and achieve the effect of avoiding excessive collapse

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

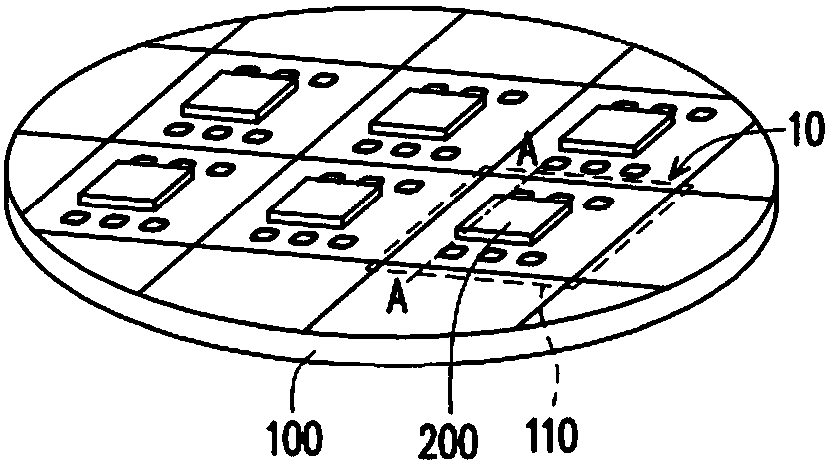

[0036] Figure 1A is a schematic diagram of a semiconductor package according to an embodiment of the present invention. Please see first Figure 1A , Figure 1A It shows a plurality of semiconductor packages 10 that have not been cut, and a wafer 100 located below includes a plurality of first chips 110 arranged in an array, and a plurality of second chips 200 are respectively flip-chip configured on the first chips 110 of the wafer 100 superior.

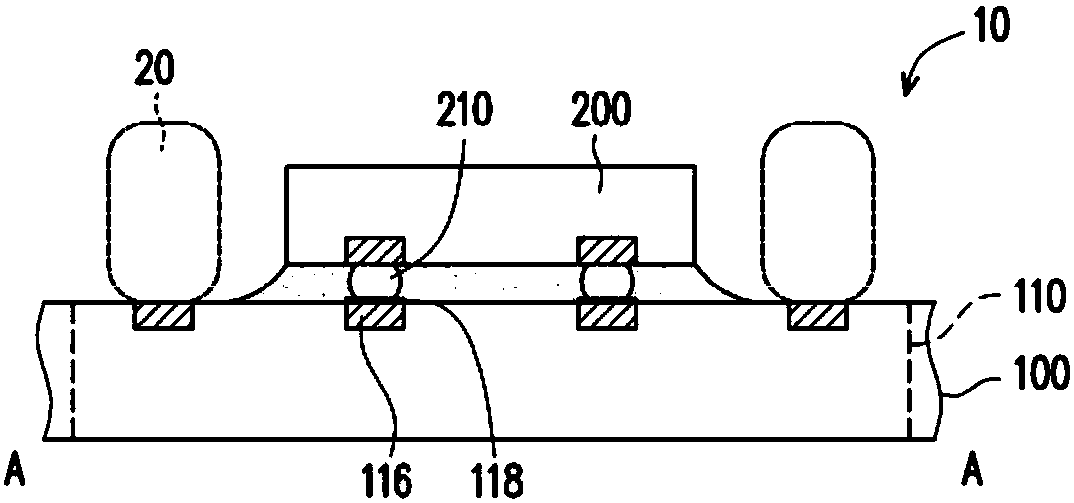

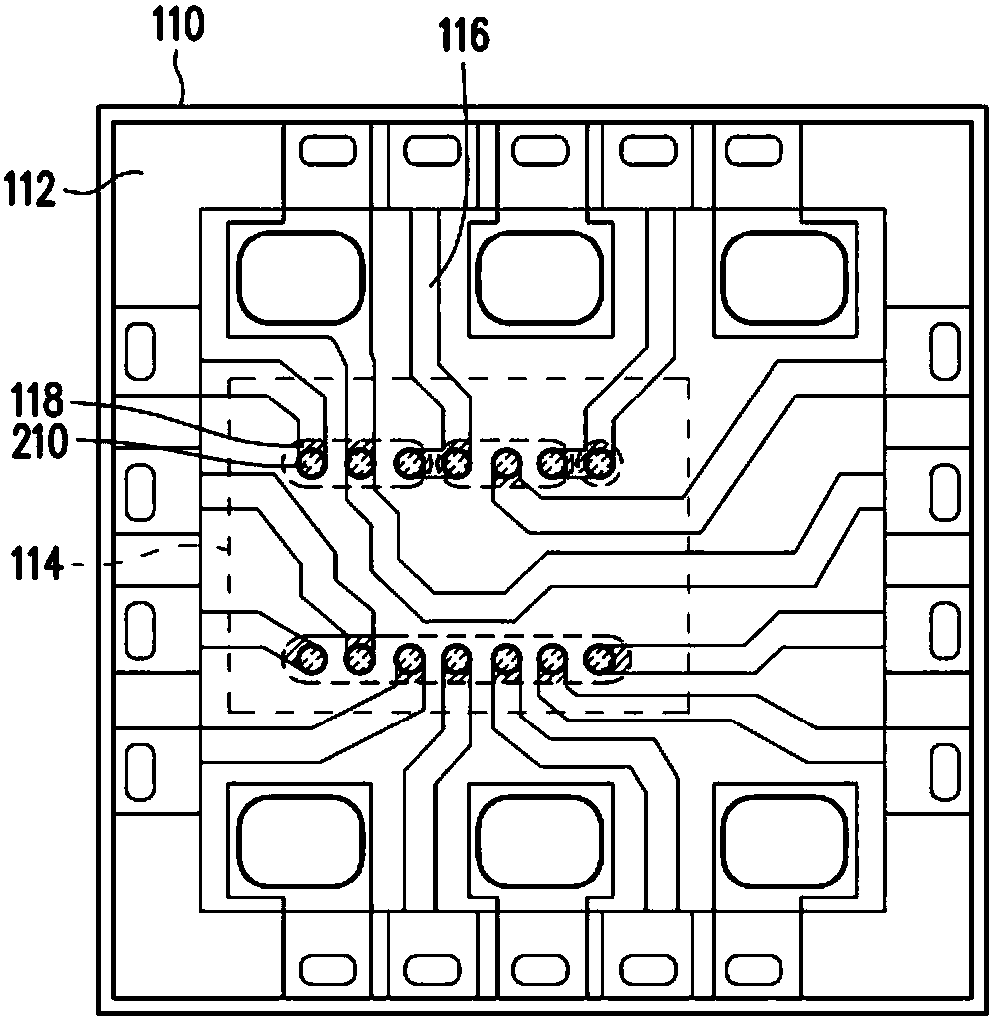

[0037] Figure 1B is along Figure 1A A schematic cross-sectional view of the A-A line segment. figure 2 yes Figure 1A An enlarged schematic top view of one of the semiconductor packages in . It should be noted that in figure 2 The second chip 200 and the encapsulant between the first chip 100 and the second chip 200 are intentionally hidden in order to expose the relative positions between the bumps 210 and the wires 116 . see Figure 1B to Figure 2 , the semiconductor package 10 of this embodiment includes a first chip 11...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com