Shifting register unit and driving method thereof as well as gate drive circuit and display device

A shift register, unit group technology, applied in static memory, digital memory information, instruments, etc., can solve the problems of poor stability, high power consumption, and short working life of GOA circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

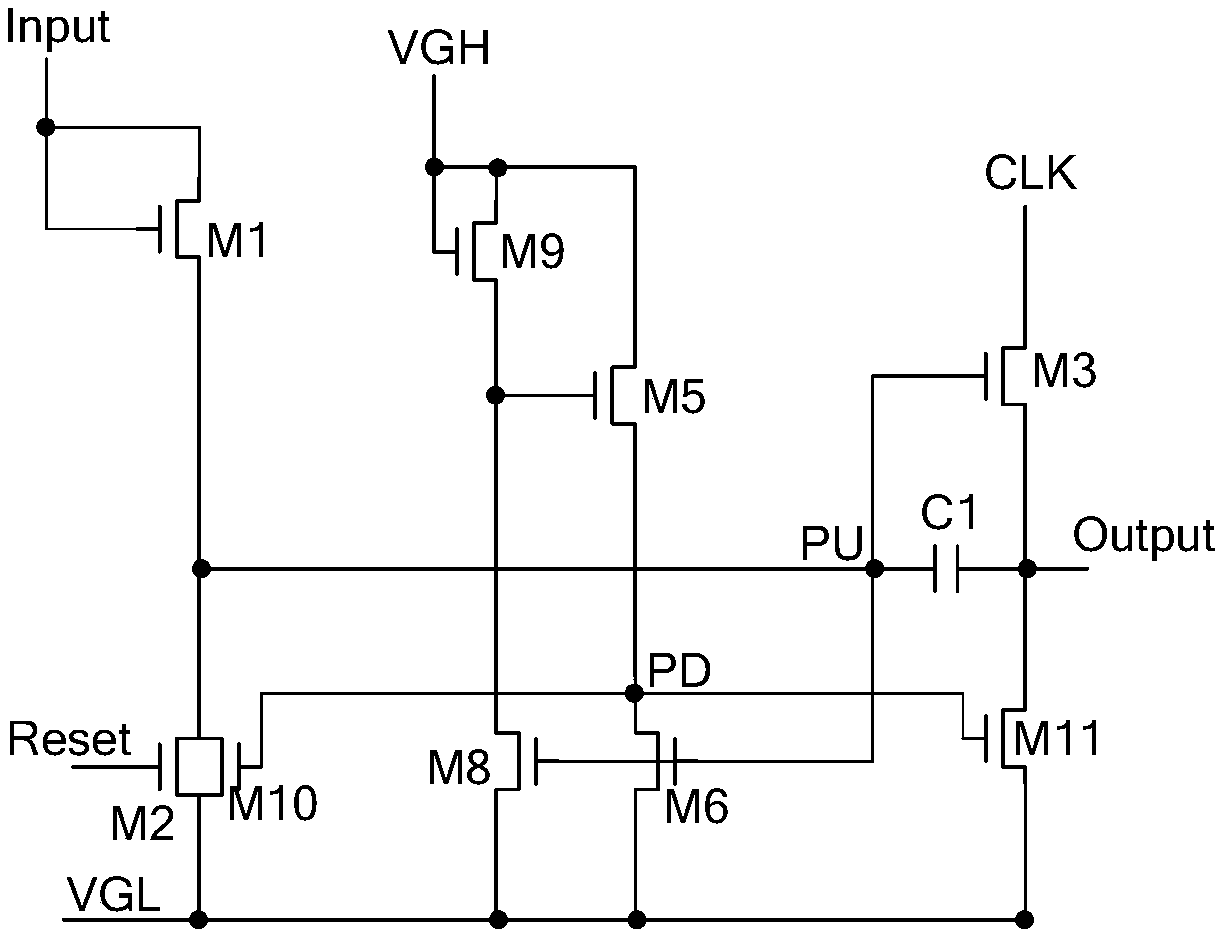

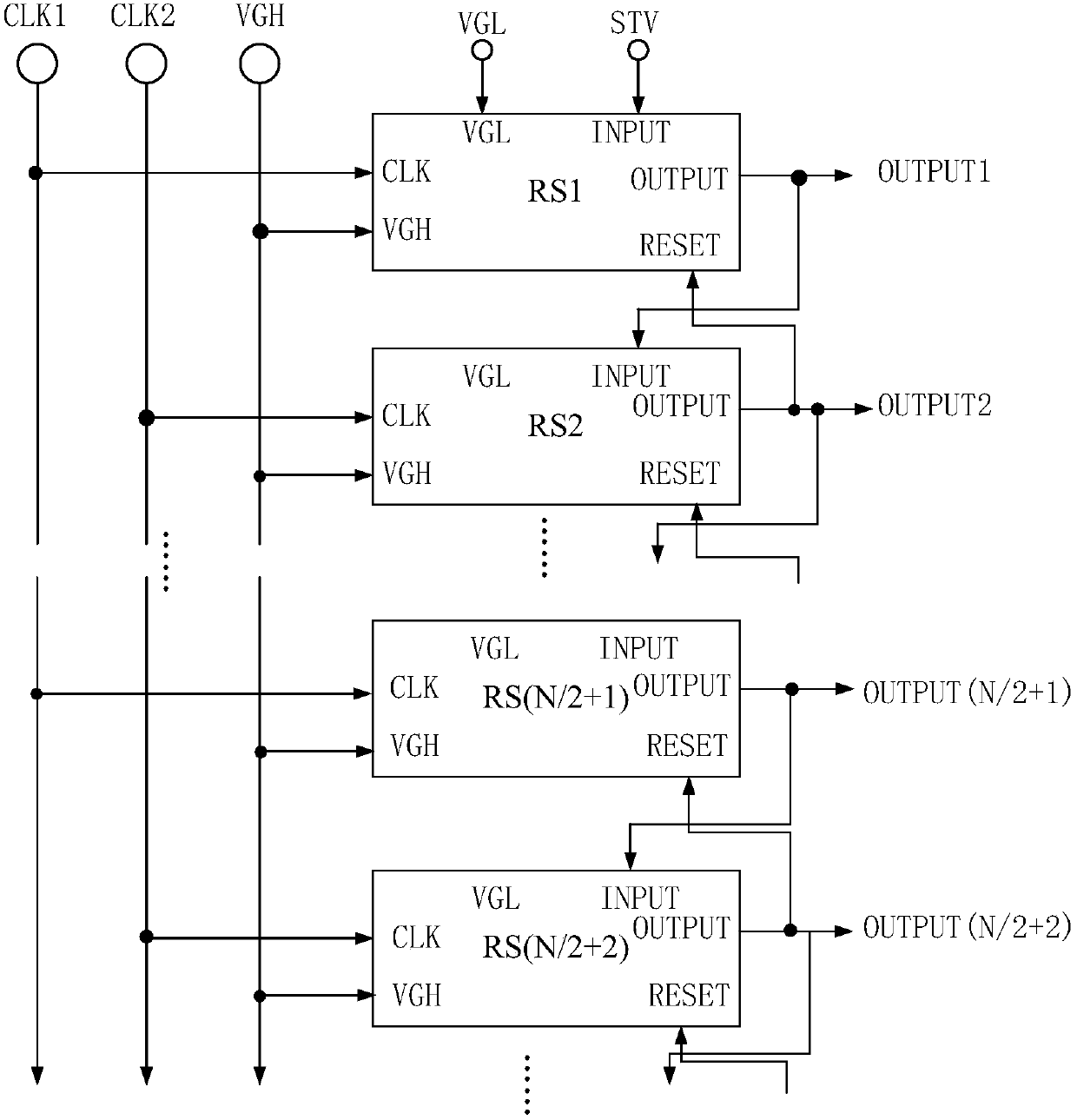

[0058] An embodiment of the present invention provides a shift register unit, such as Figure 6 As shown, it includes: a pull-up control module 10 , a pull-up module 20 , a pull-down control module 30 , a pull-down module 40 , a reset module 60 , and a denoising module 50 , that is, M=1.

[0059] Wherein, the pull-up control module 10 is connected to the signal input terminal Input and the pull-up node PU, and the pull-up control module 10 is used to pull up the potential of the pull-up node PU to the signal input terminal Input under the control of the signal input terminal Input.

[0060] The pull-up module 20 is connected to the pull-up node PU, the clock signal terminal CLK and the signal output terminal Output. The pull-up module 20 is used to output the signal of the clock signal terminal CLK to the signal output terminal Output under the control of the pull-up node PU.

[0061] The pull-down control module 30 is connected to the first control terminal Ctr, the pull-down...

Embodiment 2

[0095] Embodiments of the present invention provide a Figure 10 The shift register unit shown is different from the first embodiment in that the shift register unit includes a denoising module 50 and a denoising module 50', that is, M=2. The denoising module 50' is connected to the second control terminal TRSTb, the pull-up node PU, the signal output terminal Output and the first voltage terminal VGL, and the denoising module 50' is used to control the pull-up node PU under the control of the second control terminal TRSTb The potential of the sum signal output terminal Output is pulled down to the first voltage terminal VGL.

[0096] On this basis, the circuit structure of the denoising module 50' can be as follows Figure 11 It includes the twelfth transistor M12 and the thirteenth transistor M13, the connection relationship of which is the same as the structure of the denoising module 50 in the first embodiment, which will not be repeated in the present invention.

[0097...

Embodiment 3

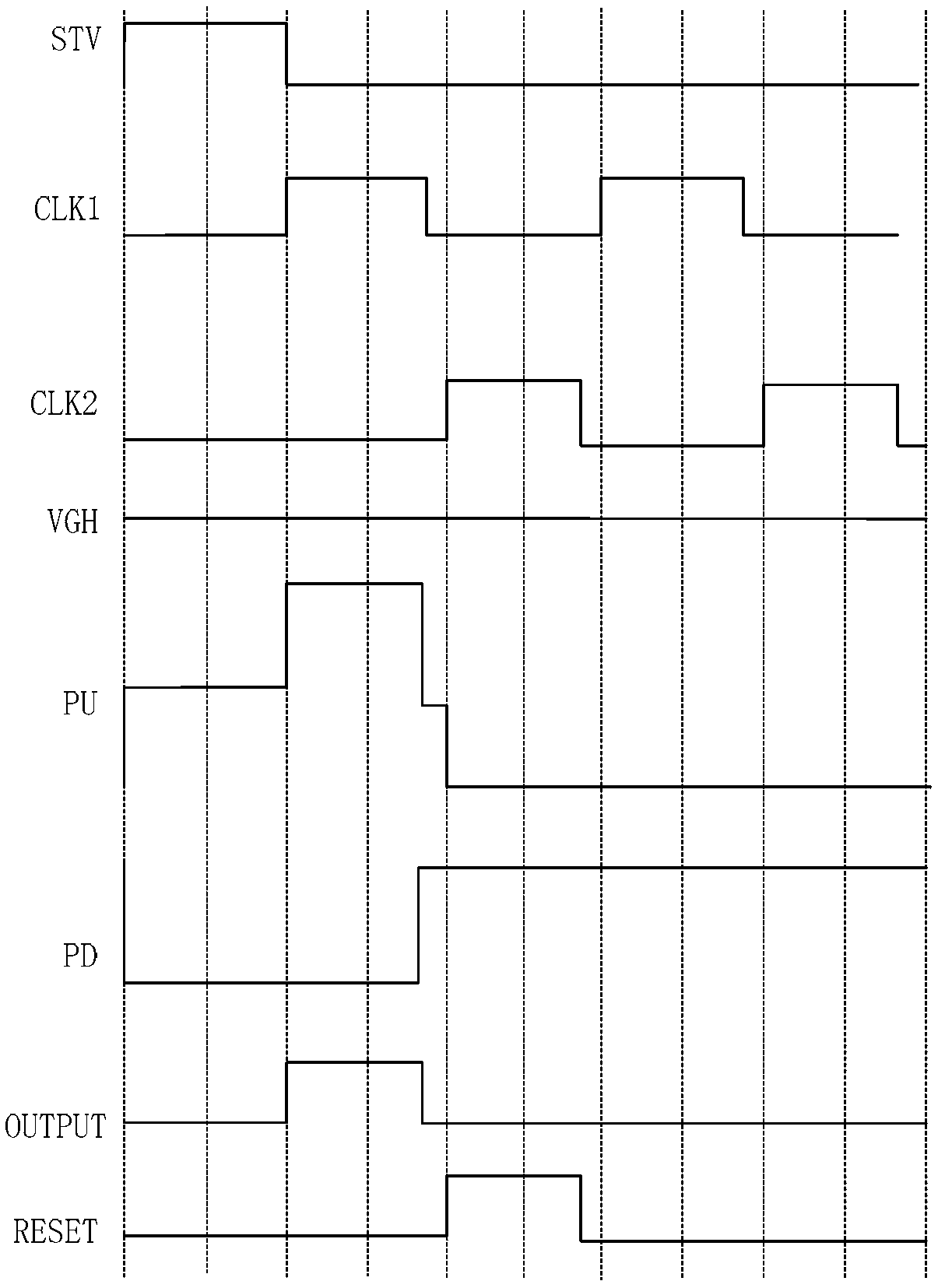

[0106] An embodiment of the present invention provides a driving method for a shift register unit as described in Embodiment 1. Refer to Figure 9a and Figure 9b As shown, in an image frame, the driving method includes:

[0107] Input stage P1: Input=1, CLK=CLK1=0, Ctr=1, TRSTa=0, PU=1, PD=0, Output=0.

[0108] The pull-up control module 10 pulls up the potential of the pull-up node PU to the signal input terminal Input under the control of the signal input terminal Input; the pull-down control module 30 pulls the potential of the pull-up node PU and the first control terminal Ctr under the control of the pull-up node PU The potential of the node PD is pulled down to the first voltage terminal VGL.

[0109] Specifically, since the signal input terminal Input is at a high level, under the control of the signal input terminal Input, the first transistor M1 is turned on, and the high level of the signal input terminal Input is output to the pull-up node PU through the first tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More