System-on-a-chip (SoC) production method with fault diagnosis

A system-level chip and production method technology, applied in measurement devices, instruments, measurement electronics, etc., can solve the problems of high test cost of automatic test equipment, bottlenecks in development cycle and fault location, and difficulty in improving fault coverage, so as to improve the chip The effect of testing efficiency, narrowing the scope of investigation, and saving chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] It should be noted that, in the case of no conflict, the following technical solutions and technical features can be combined with each other.

[0042] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

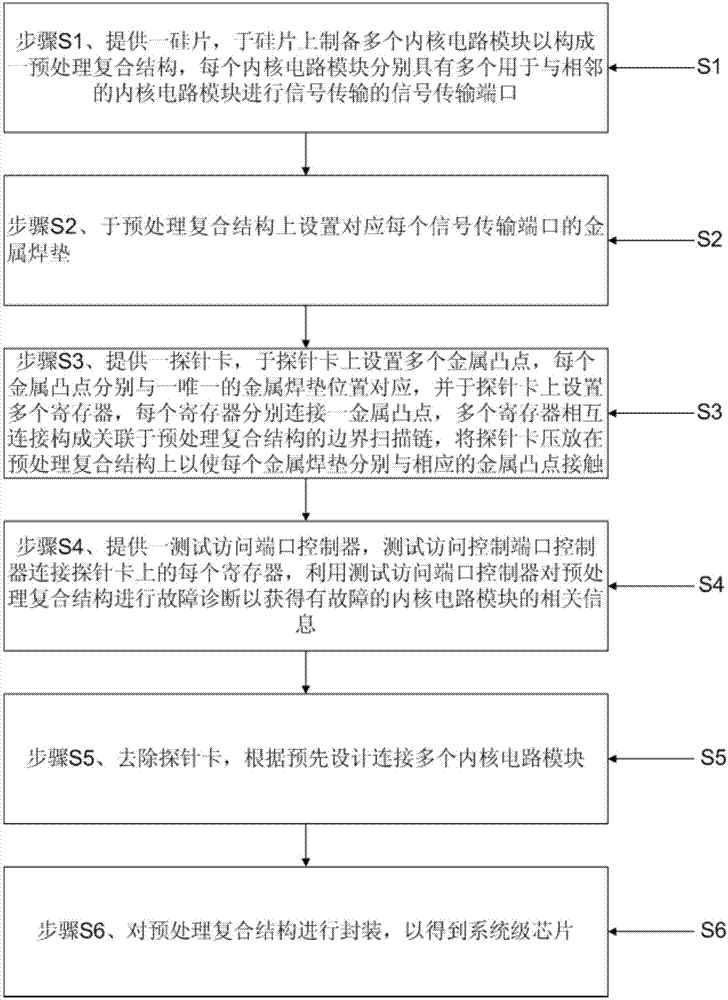

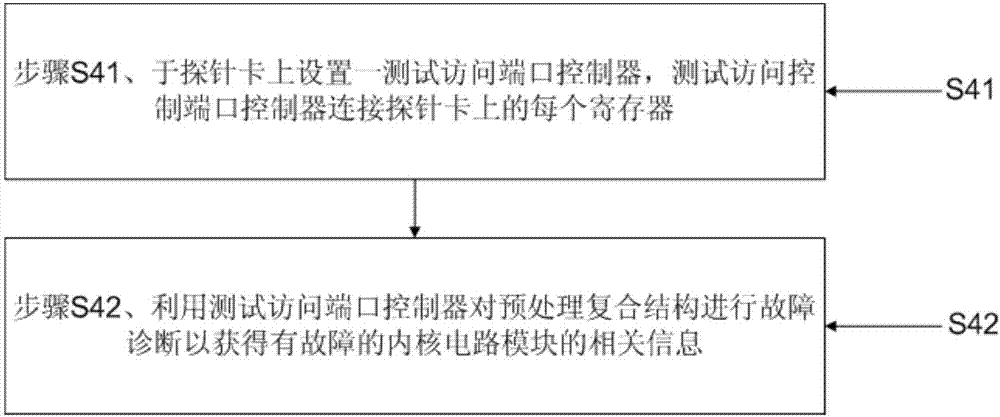

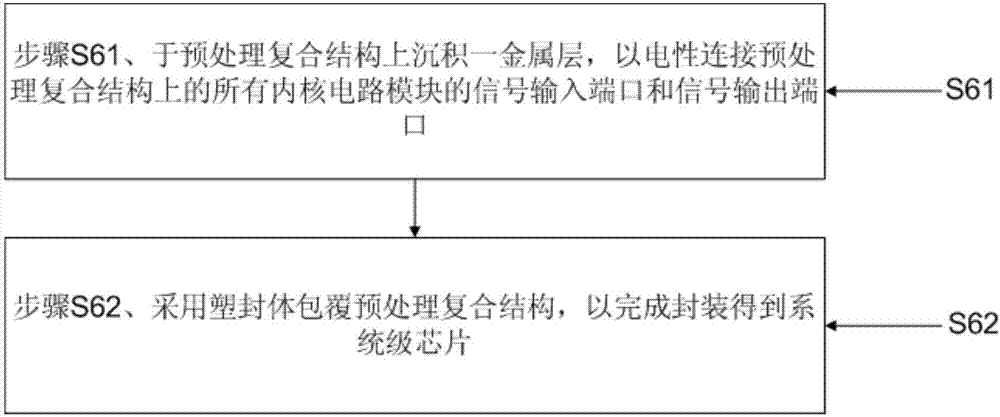

[0043] Such as figure 1 As shown, a system-on-chip production method with fault diagnosis, the above-mentioned method comprises:

[0044] Step S1, providing a silicon chip, preparing a plurality of core circuit modules 1 on the above silicon chip to form a preprocessing composite structure 5, each of the above-mentioned core circuit modules 1 has a plurality of core circuit modules for connecting with adjacent core circuit modules 1. A signal transmission port for signal transmission;

[0045] Step S2, setting metal pads 7 corresponding to each of the above-mentioned signal transmission ports on the above-mentioned pretreatment composite structure 5;

[0046] Step S3, provide a probe card 6, set...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More