Photolithography method for silicon wafer surface with high step structure

A silicon wafer surface and step technology, applied in microlithography exposure equipment, optics, optomechanical equipment, etc., can solve the problems of high cost and long operation time, and achieve the effects of short operation time, cost reduction and simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

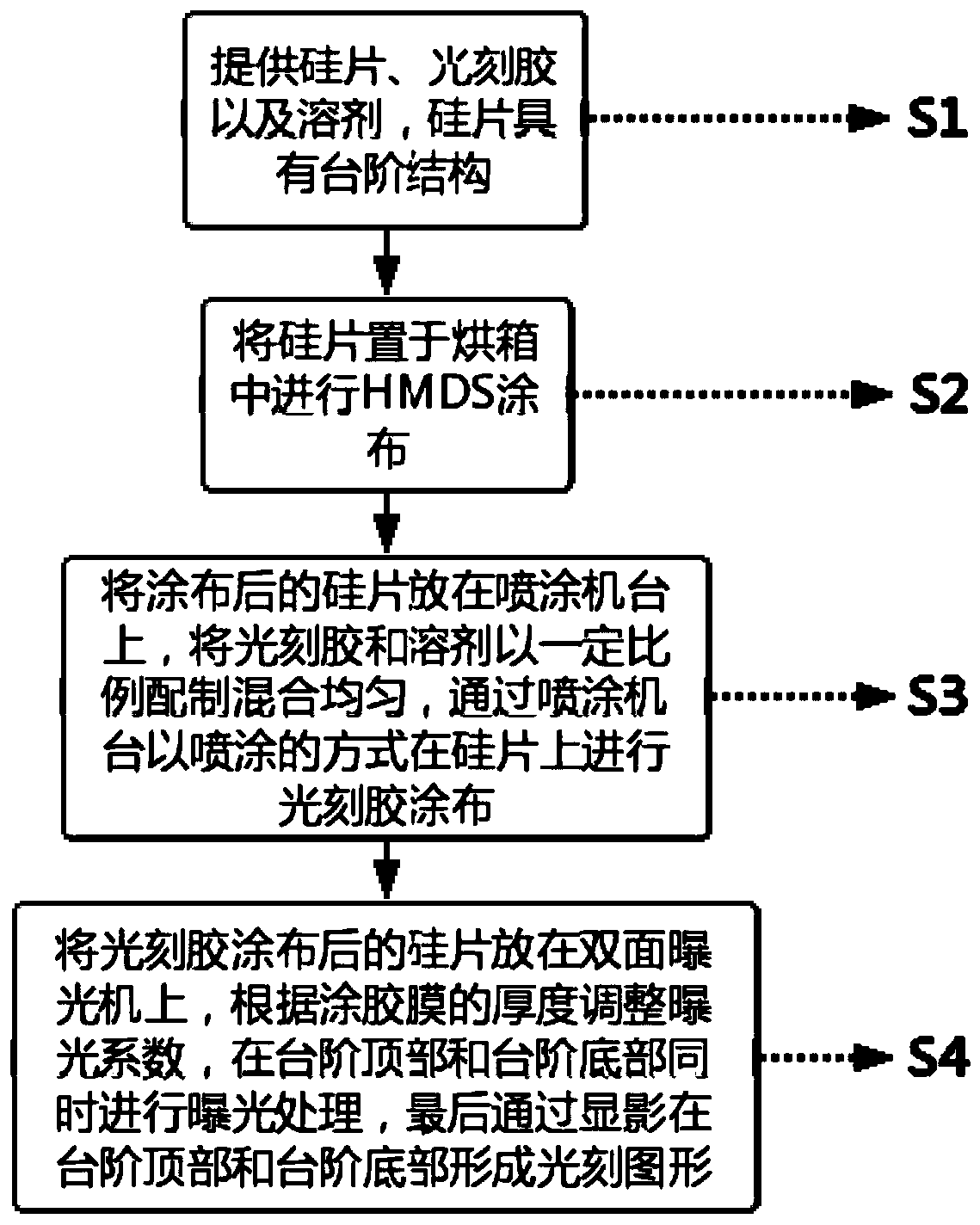

Method used

Image

Examples

Embodiment 1

[0038] According to the normal yellow light process, the silicon wafer with a 300μm high step structure wet-etched by KOH is coated with HMDS in an oven, and then a 1:10 ratio of photoresist and solvent is used on the spraying machine. Coat the photoresist on the silicon wafer by spraying, and confirm that the side walls of the steps and the sharp corners are completely covered by the photoresist (see Figure 3 to Figure 6 ), and the glued film at the bottom of the step is confirmed to be 4um, the glued film at the top of the step is confirmed to be 6um, and the thickness of the glued film on the side wall and sharp corner of the step is confirmed to be 2um. Finally, the silicon wafer is placed in a double-sided exposure machine, and the exposure coefficient is adjusted according to the thickness of the adhesive film. At the same time, the exposure treatment is performed on the bottom of the step and the top of the step, and then developed to obtain a photolithographic pattern ...

Embodiment 2

[0040] According to the normal yellow light process, the silicon wafer with a 150 μm high step structure wet etched by KOH is coated with HMDS in an oven, and then a 1:8 ratio of photoresist and solvent is used on the spraying machine. Coat the photoresist on the silicon wafer by spraying, confirm that the side walls and sharp corners of the steps are completely covered by the photoresist, and the coating film at the bottom of the steps is confirmed to be 2um, and the coating film at the top of the steps is confirmed to be 3um , the film thickness of the side wall of the step and the sharp corner is confirmed to be 1um. Finally, the silicon wafer is placed in a double-sided exposure machine, and the exposure coefficient is adjusted according to the thickness of the adhesive film. At the same time, the exposure treatment is performed on the bottom of the step and the top of the step, and then developed to obtain a photolithographic pattern on the bottom of the step and the top o...

Embodiment 3

[0042] According to the normal yellow light process, the silicon wafer with a 500μm high step structure wet-etched by KOH is coated with HMDS in an oven, and then a 1:20 ratio of photoresist and solvent is used on the spraying machine. Coat the photoresist on the silicon wafer by spraying, confirm that the side walls and sharp corners of the steps are completely covered by the photoresist, and the coating film at the bottom of the steps is confirmed to be 6um, and the coating film at the top of the steps is confirmed to be 6um , The film thickness of the side wall of the step and the sharp corner is confirmed to be 4um. Finally, the silicon wafer is placed in a double-sided exposure machine, and the exposure coefficient is adjusted according to the thickness of the adhesive film. At the same time, the exposure treatment is performed on the bottom of the step and the top of the step, and then developed to obtain a photolithographic pattern on the bottom of the step and the top o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| height | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More