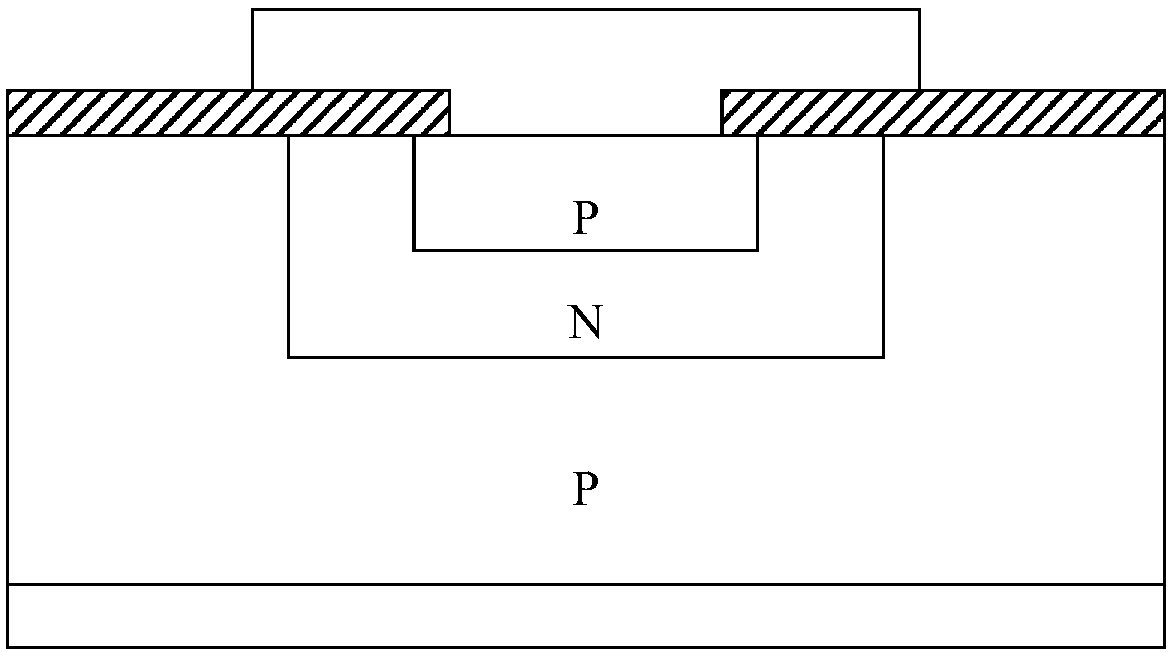

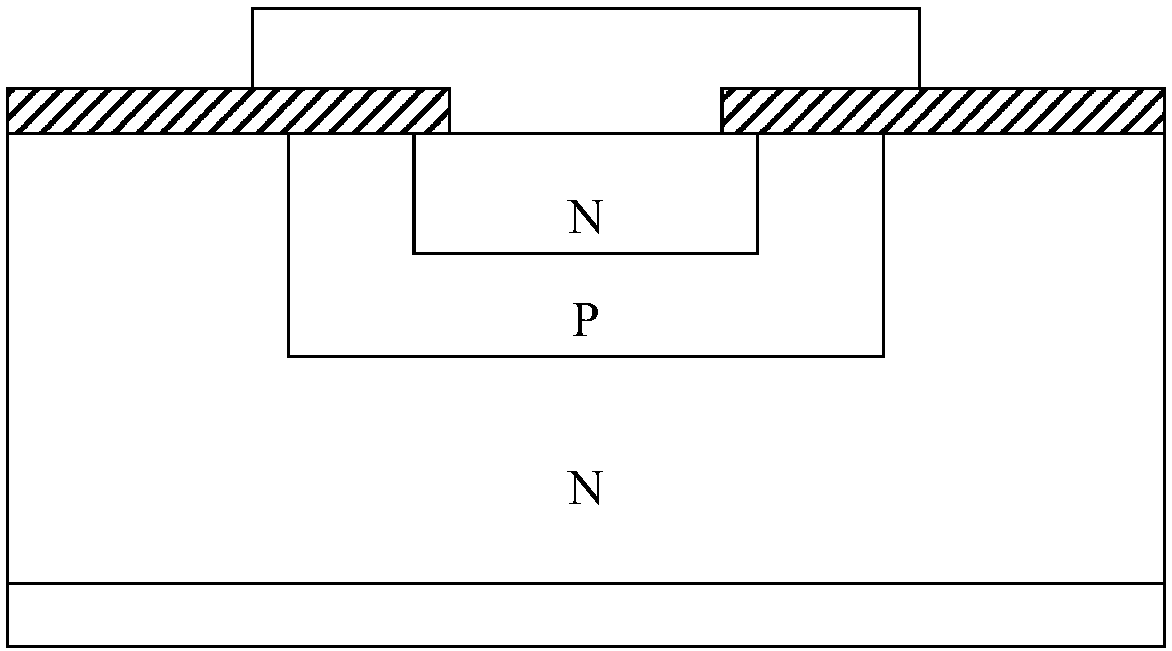

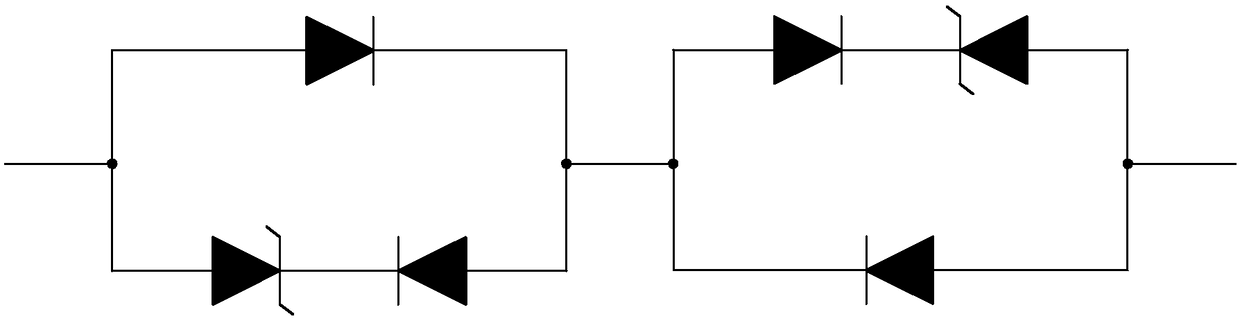

Transient voltage suppressor and manufacturing method thereof

A technology of transient voltage suppression and manufacturing method, which is applied in the direction of electric solid-state devices, circuits, electrical components, etc., can solve the problems of large size of bidirectional transient voltage suppressor, high cost of chip placement, unsuitable package, etc., to achieve The effect of reducing the difficulty of production, high chip area utilization, and chip size compression

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The present invention is described below based on examples, but the present invention is not limited to these examples. In the following detailed description of the embodiments of the present invention, some specific details are described in detail, and those skilled in the art can fully understand the present invention without the description of these details. In order to avoid obscuring the essence of the present invention, well-known methods, procedures, and flow charts are not described in detail.

[0043] In the various figures, identical elements are indicated with similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale. Also, some well-known parts may not be shown in the drawings. The flowcharts and block diagrams in the accompanying drawings illustrate the possible system framework, functions and operations of the systems, methods, and devices of the embodiments of the present invention, and the blocks an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com