Comparator and successive approximation analog-to-digital converter

A comparator and inverter technology, applied in the direction of analog/digital conversion, code conversion, instruments, etc., can solve the problem of low speed of the comparator, and achieve the effect of increasing the speed and reducing the number of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The asynchronous successive approximation analog-to-digital converter (Successive Approximation Register Analog-to-Digital Converter, SAR DC) is a research hotspot in recent years. Compared with the traditional pipelined ADC, the asynchronous SAR ADC has the advantages of low power consumption and low cost , These advantages enable asynchronous SAR ADC to obtain a wide range of applications, such as portable battery-powered instruments, pen input quantizers, industrial control and data signal collectors, etc.

[0024] However, the asynchronous SAR ADC also has the problem of low maximum operating speed, and the reason for the low maximum operating speed of the SAR ADC is its internal comparator.

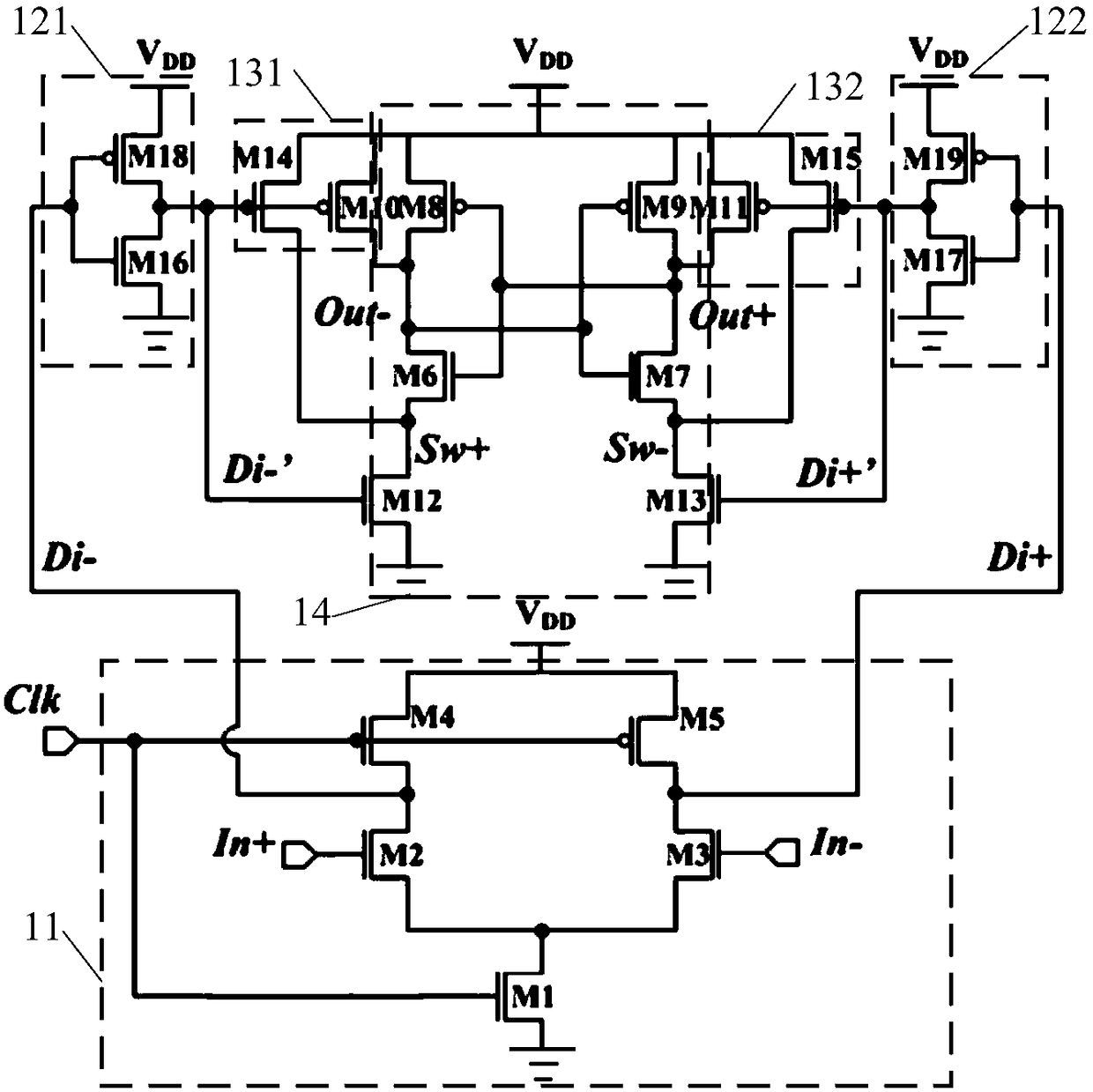

[0025] Currently, a typical comparator structure is as figure 1As shown, the comparator includes: a first pre-op-amp unit 11 suitable for sequentially amplifying the signal to be compared at various stages, including an op-amp subunit 121 and an op-amp subunit 121 symmetricall...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More