14T radiation-resistant static storage cell

A static storage and anti-irradiation technology, applied in static memory, information storage, digital memory information, etc., can solve problems such as poor write margin, high power consumption, and slow circuit write speed, so as to reduce power consumption and improve resistance The ability of SEU and the effect of improving the writing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

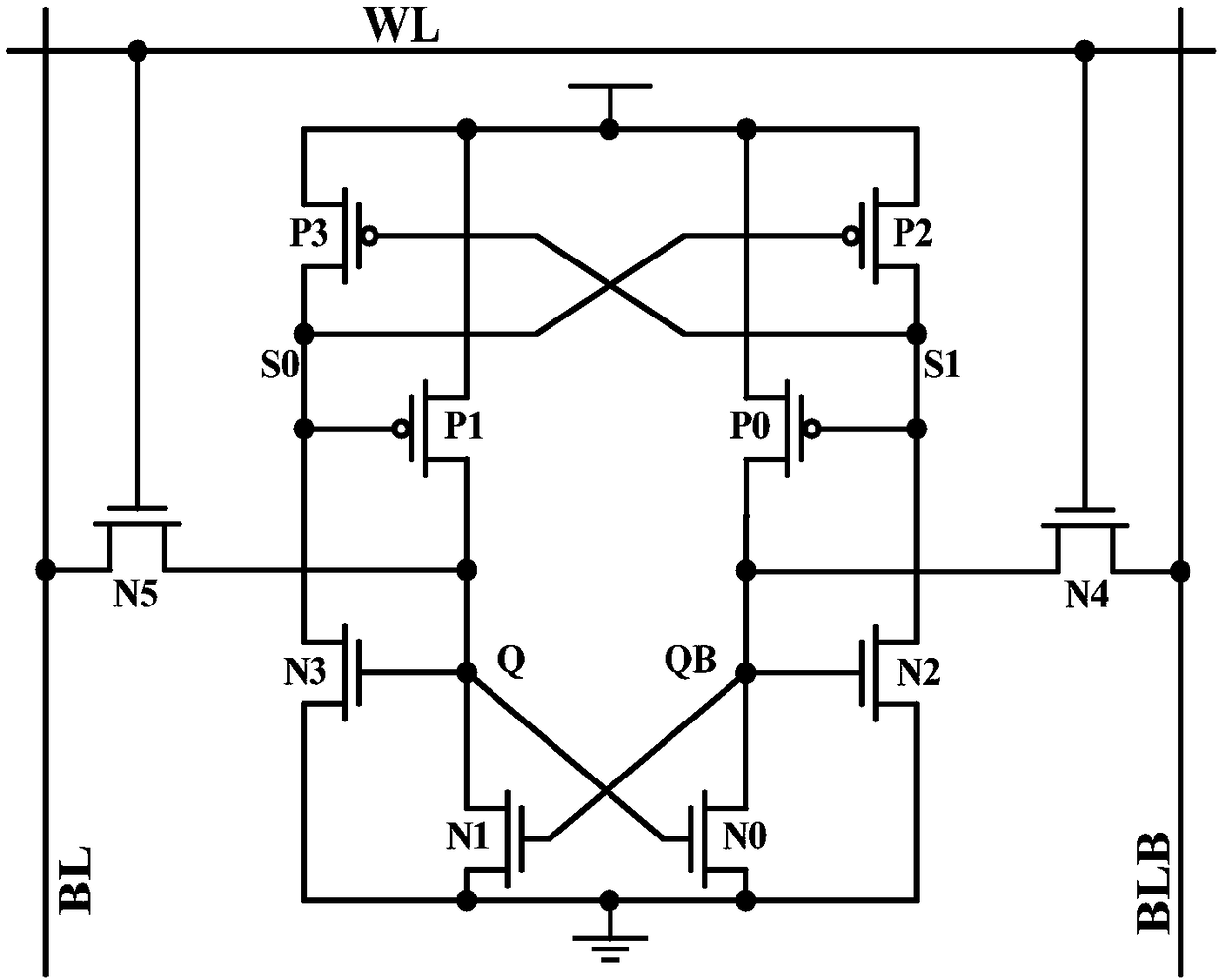

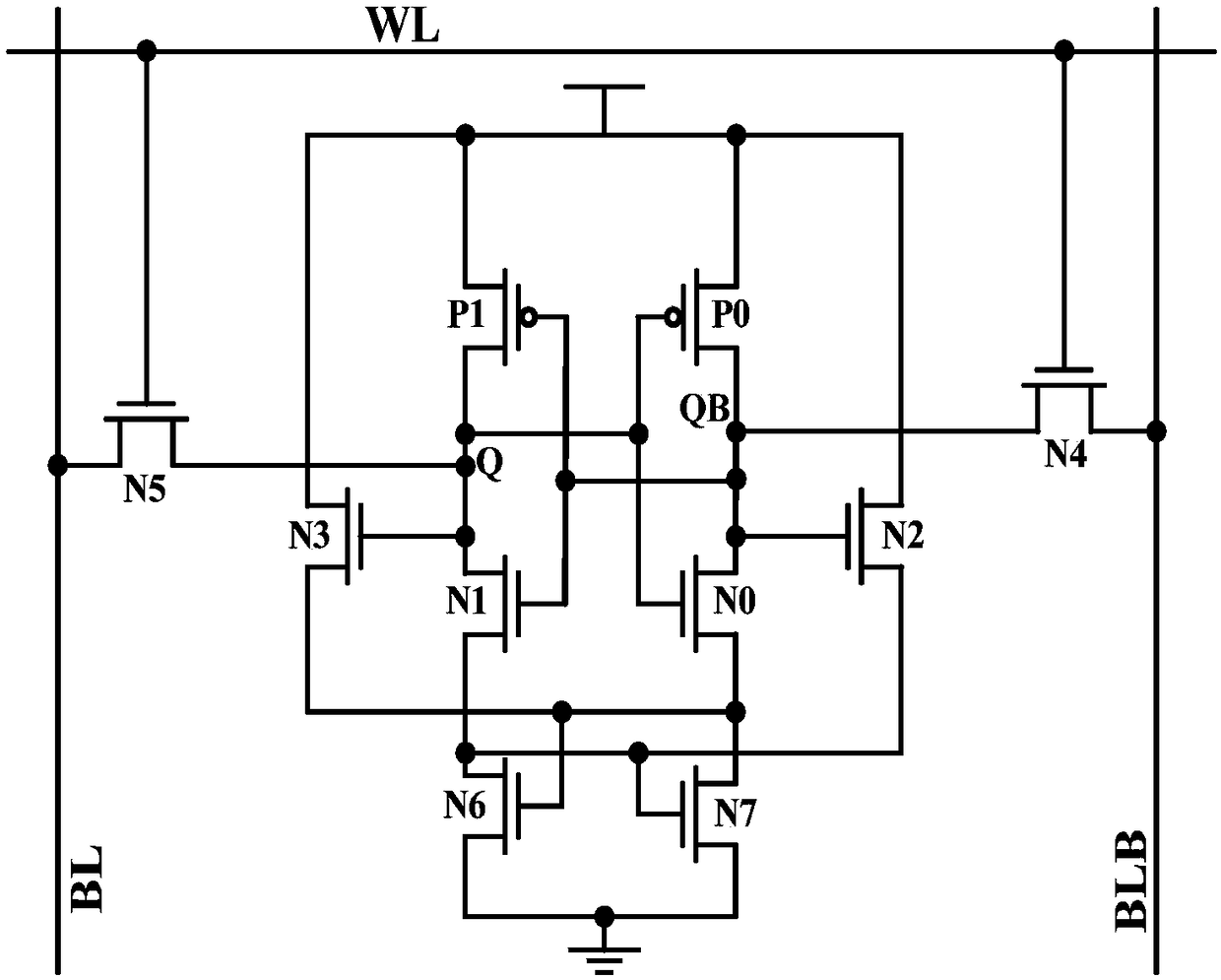

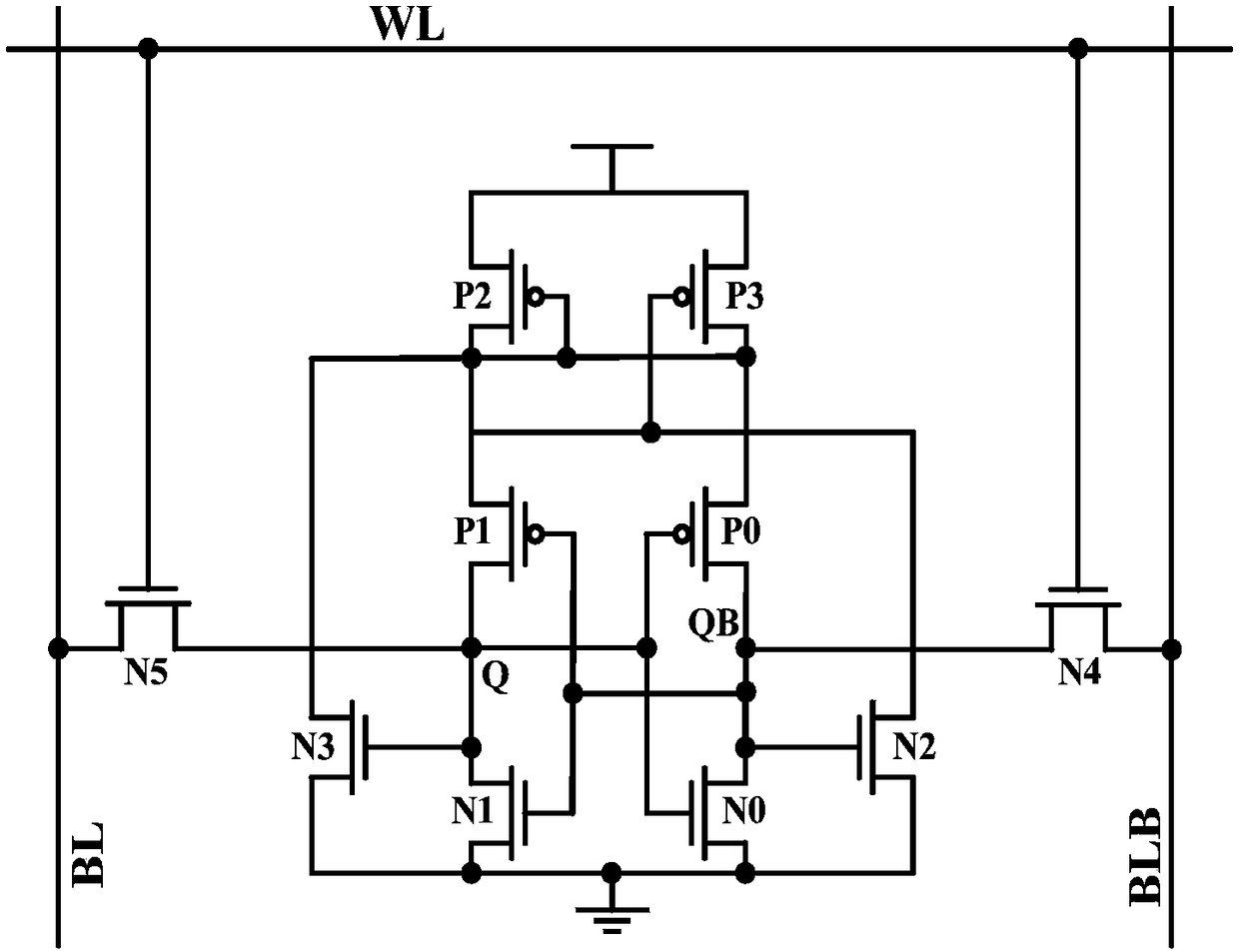

[0034] An embodiment of the present invention provides a 14T radiation-resistant static memory unit, such as Figure 6As shown, it mainly includes: six NMOS transistors and eight PMOS transistors; the six NMOS transistors are sequentially marked as N0~N5, and the eight PMOS transistors are sequentially marked as P0~P7; the PMOS transistor P1 and the NMOS transistor N1 form an inverting PMOS transistor P0 and NMOS transistor N0 form another inverter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More