14T radiation-proof SRAM (Static Random Access Memory) storage unit circuit

A storage unit circuit and anti-irradiation technology, which is applied in the field of SRAM, can solve the problems of incomplete immunity to SEU, inability to recover SEU, time difference between read operation and write operation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

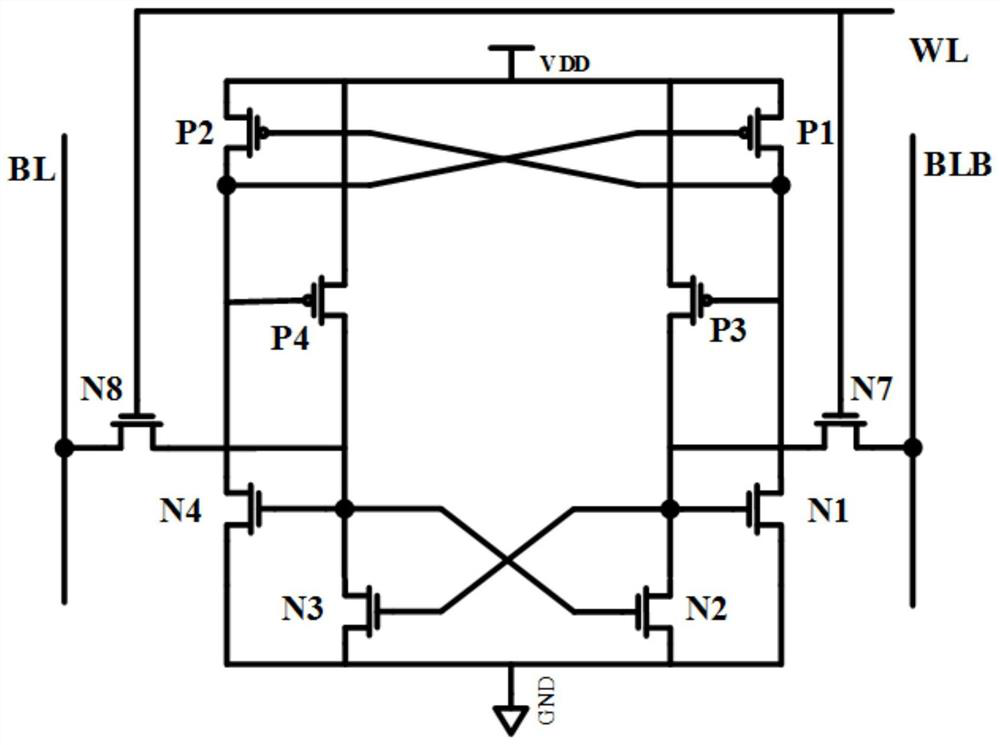

[0030] Such as Figure 5 As shown, Embodiment 1 of the present invention provides a 14T radiation-resistant SRAM storage unit circuit (referred to as HRH-14T), which is a 14T radiation-resistant SRAM storage unit circuit based on polarity hardening technology, and its structure mainly includes 8 NMOS transistors and 6 PMOS transistors; these 8 NMOS transistors are respectively defined as N1, N2, N3, N4, N5, N6, N7, N8; these 6 PMOS transistors are respectively defined as P1, P2, P3, P4, P5, P6.

[0031] PMOS transistor P5, NMOS transistor N3, PMOS transistor P6 and NMOS transistor N4 constitute a pair of cross-coupled inverters (the PMOS transistor P5, NMOS transistor N3, PMOS transistor P6 and NMOS transistor N4 constitute a pair of cross-coupled inverters The inverter means that the PMOS transistor P5 and the NMOS transistor N3 form the first inverter, and the PMOS transistor P6 and the NMOS transistor N4 form the second inverter. These two inverters are cross-coupled, that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More