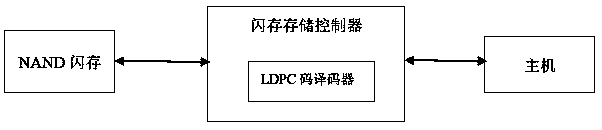

LDPC decoding method suitable for NAND flash memory

An LDPC code and decoding technology, applied in the field of LDPC decoding, can solve problems such as short delay required and unavailability of NAND flash memory systems, and achieve the effects of dynamic balance, fast data transmission, and low computing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

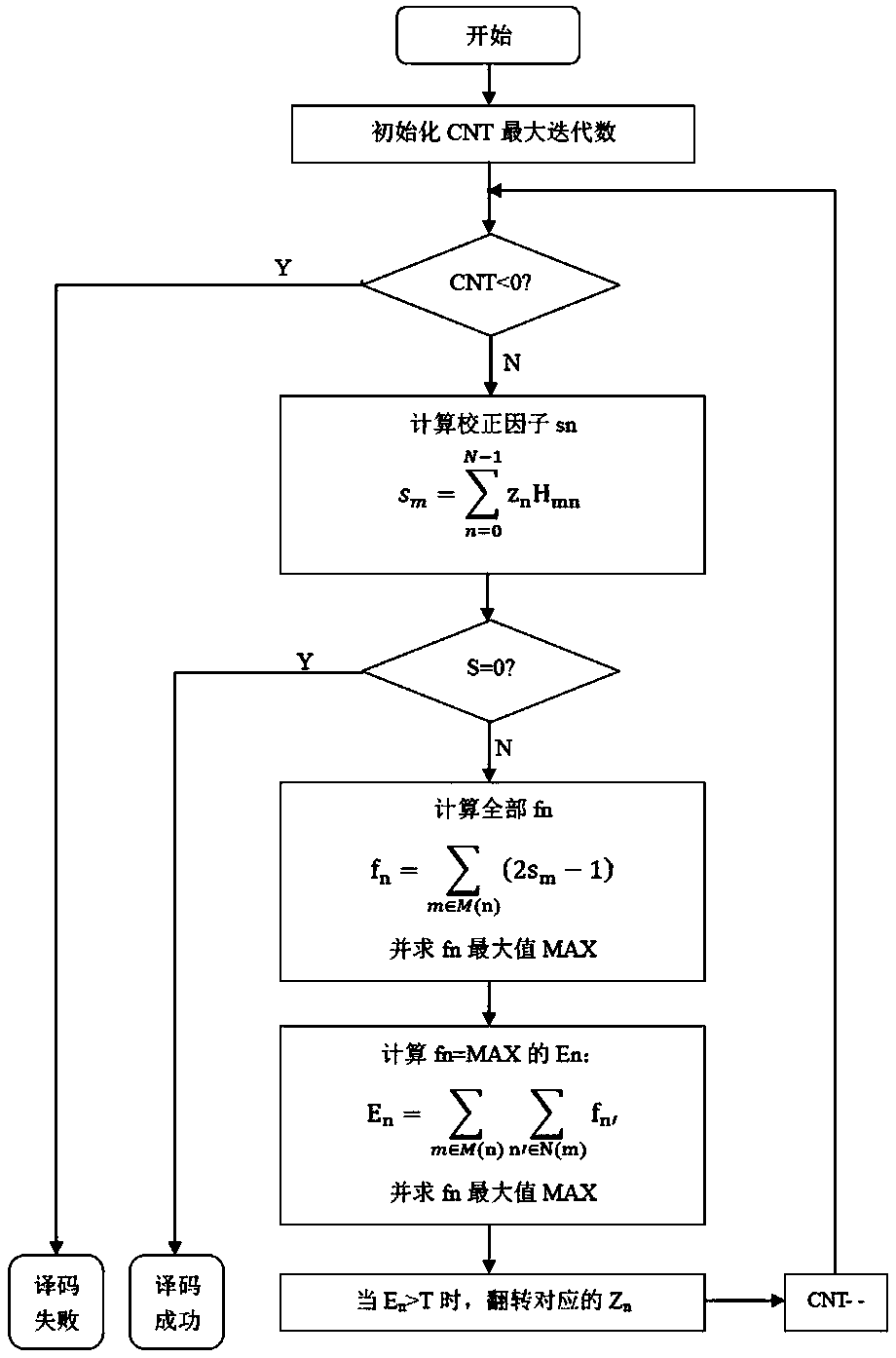

[0030] The present invention will be further defined below in conjunction with the accompanying drawings and specific embodiments.

[0031] like figure 2 As shown, it is a flow chart of the LDPC decoding method suitable for NAND flash memory described in this embodiment, and the method includes the following steps:

[0032] S01), assuming that the code length of the LDPC code is N, the information bit length is K, and its check matrix H mn is an M ×N sparse matrix [h mn ], M, N, K are positive integers greater than 0, 0≤m≤M-1, 0≤n≤N-1, H mn There are γ 1s in each column, ρ 1s in each row, γ and ρ are integers greater than or equal to 0, the size of the check matrix is M*N, and each row uses h 0 , h 1 , ……, h M-1 means that h j =( h j,0 , h j,1 , ……, h j(N-1)), 0≤j mn The set of columns where the 1 in the mth row is recorded as N(m)={n:h mn = 1}; the set of check equations that the nth bit participates in is the check matrix H mn The set of rows where the 1 in t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More