Packaging structure and packaging method for chip

A packaging method and chip technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of poor packaging structure performance and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] As mentioned in the background, the performance of the packaging structure formed by the existing 3D packaging process is poor.

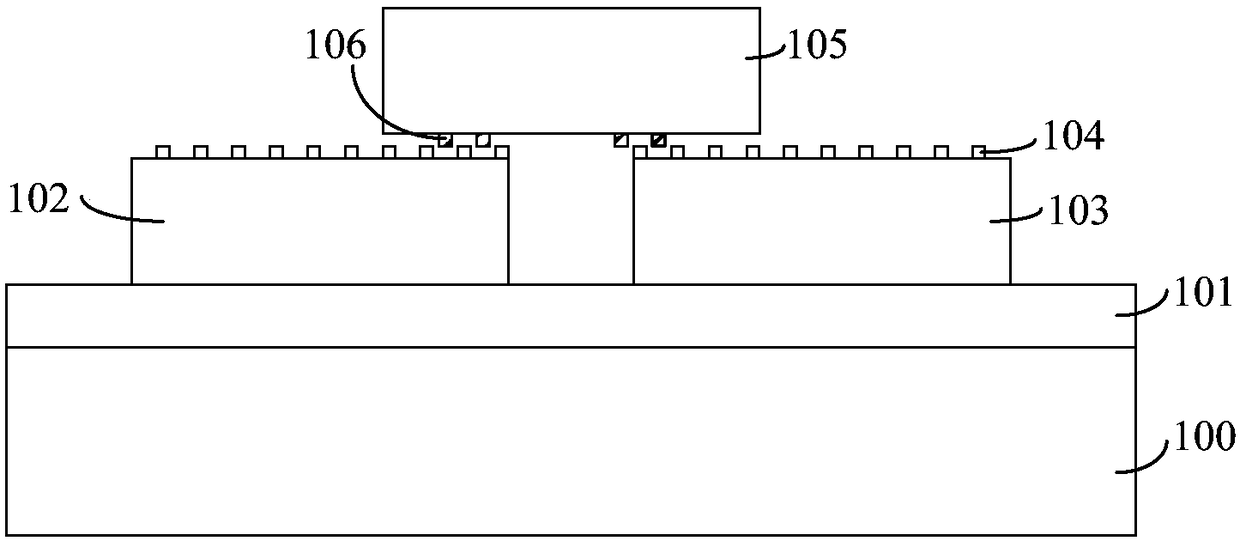

[0032] figure 1 It is a structural schematic diagram of a chip packaging structure.

[0033] Please refer to figure 1 , providing a carrier board 100, the surface of the carrier board 100 has a mounting film 101; on the surface of the mounting film 101, a first chip 102 and a second chip 103 separated from each other are mounted, and the first chip 102 and the second chip 103 are mounted on the surface of the mounting film 101. The top of the second chip 103 has a first connection column 104; a third chip 105 is provided, and the top of the third chip 105 has a second connection column 106; the third chip 105 is mounted so that the second connection column 106 is connected to the first connection column Post 104 contacts.

[0034] In the above chip packaging method, the surface of the carrier 100 has a first identification point for identi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More