A memory test system, method and storage medium

A memory test and memory technology, which is applied in the test of memory circuits in low-temperature environments, and in the field of test systems for memory circuits, can solve problems such as insufficient holding time and insufficient low-temperature test time, so as to improve test accuracy and solve direct test problems , testing a wide range of effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

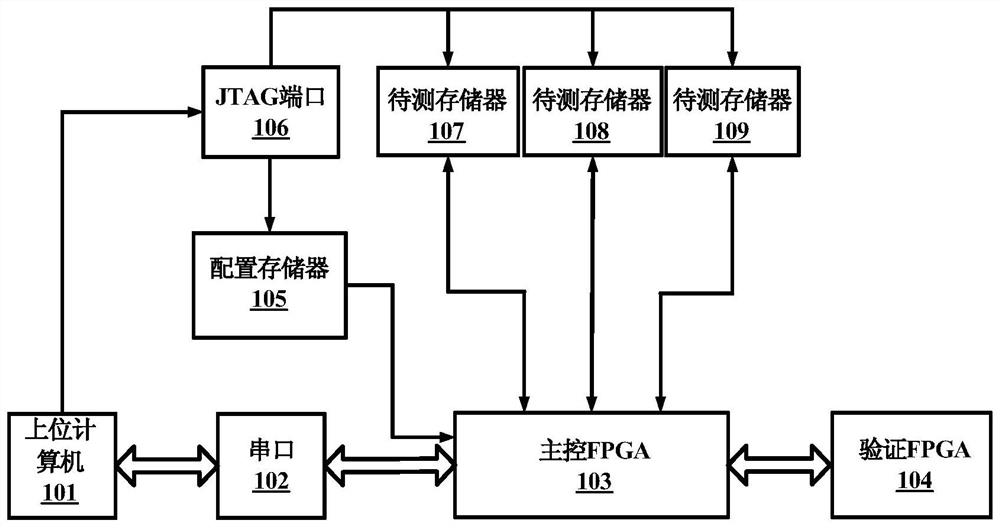

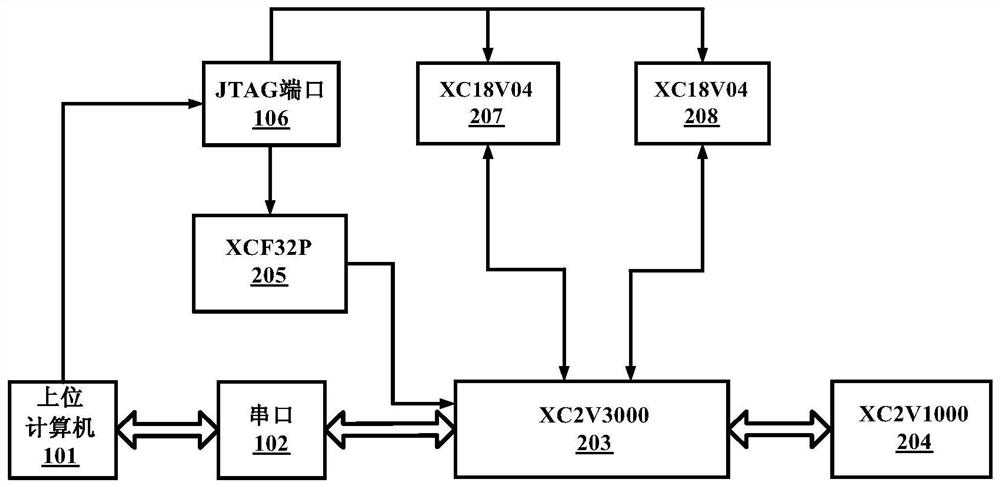

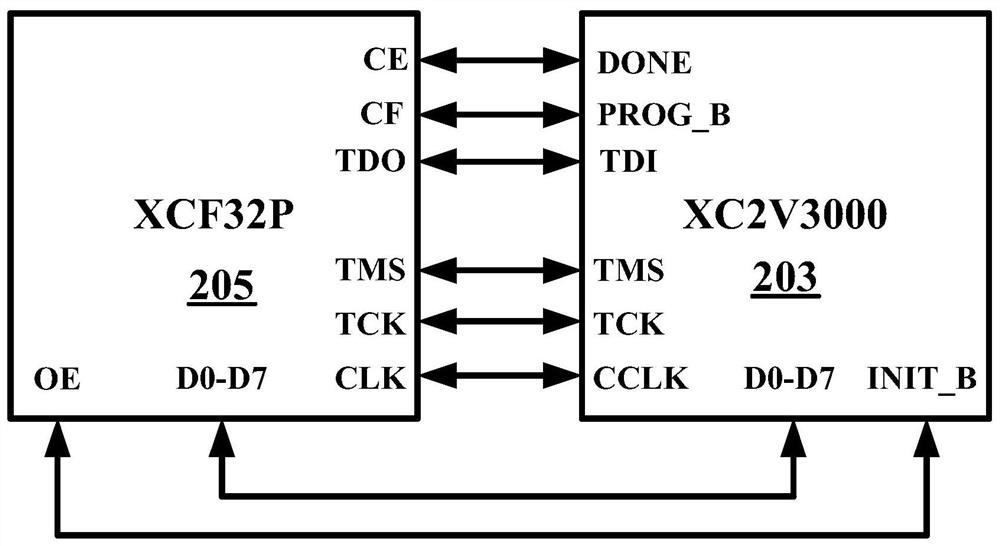

[0043] The entire test system framework is as follows figure 1 As shown, it consists of a host computer 101, a communication serial port 102, a system main control FPGA 103, a verification FPGA 104, a configuration memory 105, a JTAG port 106 and a memory to be tested 107108109. Wherein, the upper computer sends control commands to the main control FPGA 103 through the serial port 102 to operate the main control FPGA 103 . The main control FPGA controls the configuration, erasing and testing operations between the memory to be tested and the upper computer 101 and verification FPGA 104 according to the command requirements, and feeds back the memory test results to the upper computer 101 . Verify that the FPGA 104 configures it through the memory to be tested 107108109, and verify whether the function of the memory is normal through the configuration result. The configuration memory 105 is used to automatically configure the main control FPGA 103 in JTAG mode through the JTAG...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More