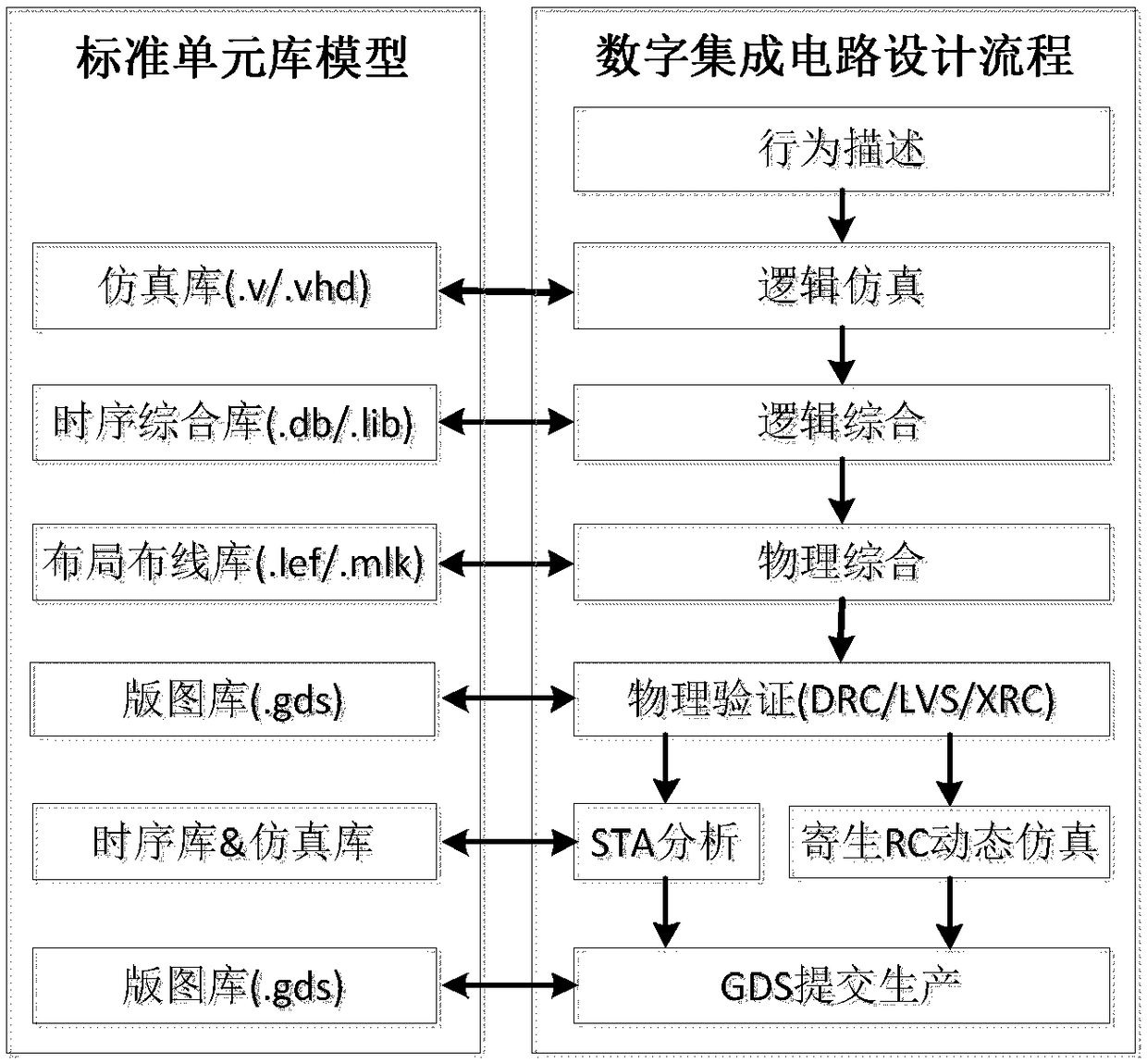

Testing method and system of standard cell library full model

A standard cell library, standard cell technology, applied in the fields of instrumentation, computing, electrical digital data processing, etc., can solve the problems of chip tape-out failure, can not guarantee the electrical characteristics of standard cell library, affect the application of chip designers, etc., to achieve high coverage The effect of rate sum

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

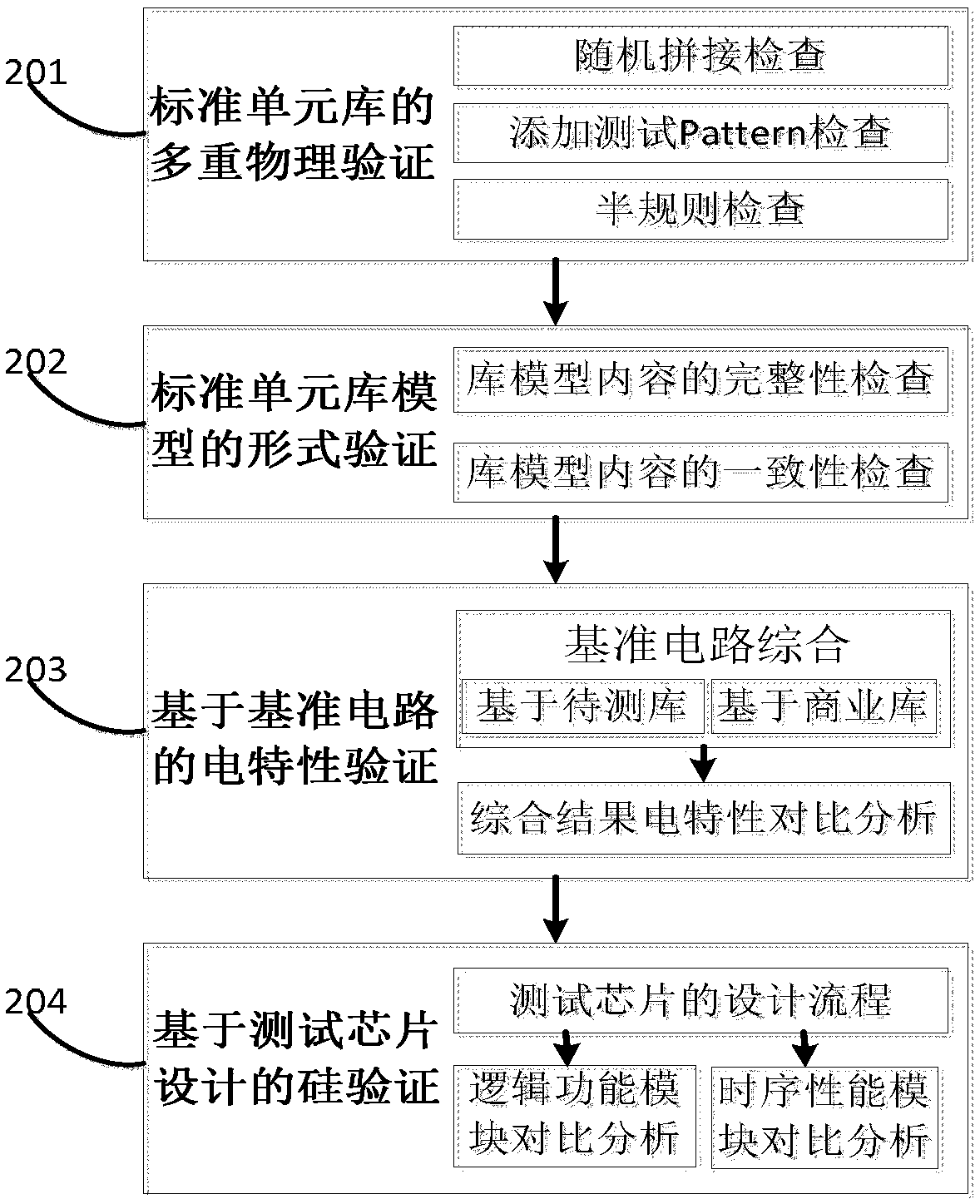

[0068] In an exemplary embodiment of the present invention, a method for testing a full model of a standard cell library is provided. figure 2 It is a schematic flowchart of a testing method for a full model of a standard cell library in an embodiment of the present invention. like figure 2 As shown, the testing method of the standard cell library full model of the present invention comprises the following steps:

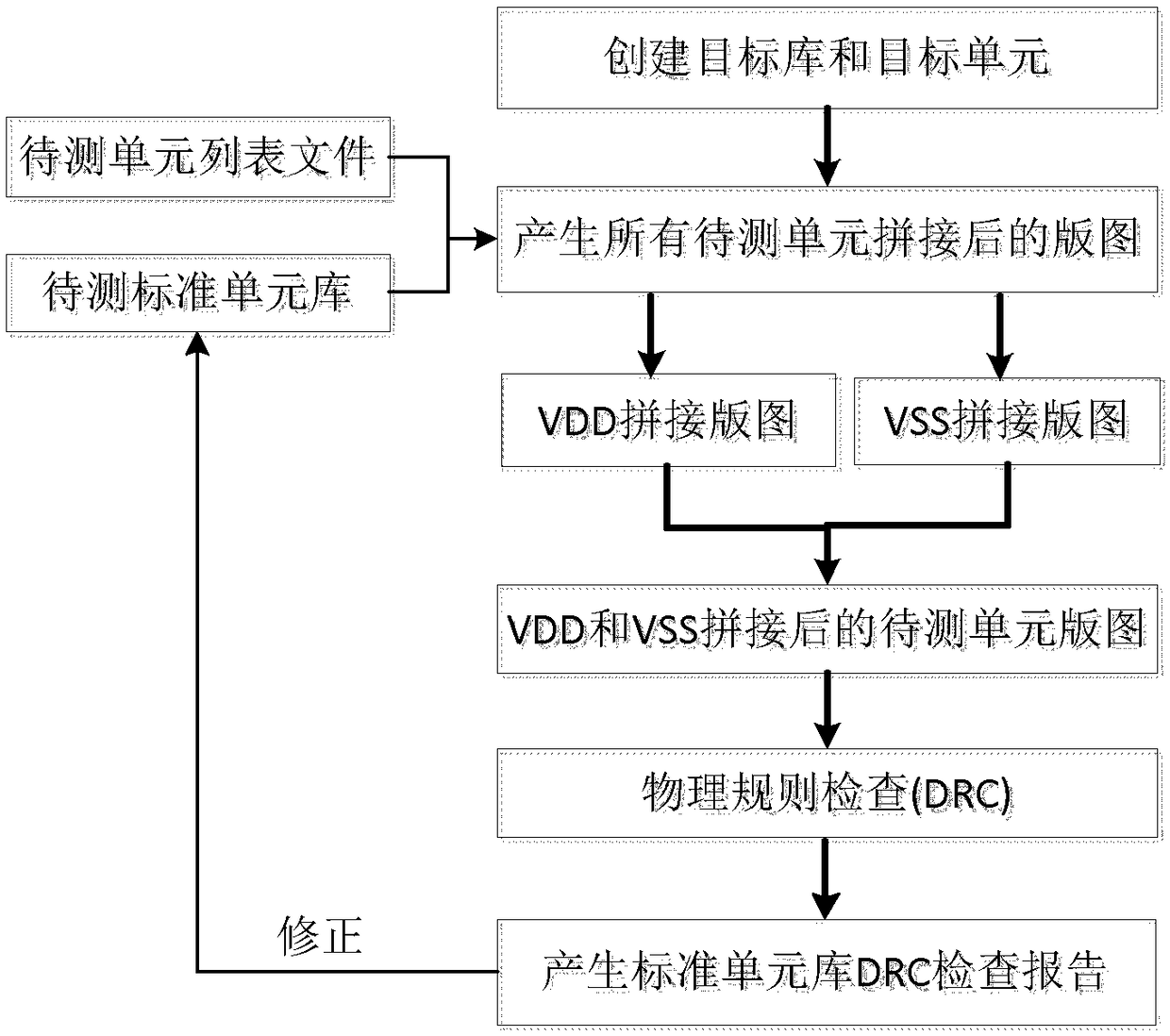

[0069] Step 201 , check the multiple physical rules of the standard cell layout to verify the correctness of the standard cell physical design rules.

[0070] This step includes the following substeps:

[0071] A1. Perform random splicing inspection of standard cells: splice all standard cells together ran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More