Transistor structure adopting embedded bit line and manufacturing method of transistor structure

A technology of embedded bit lines and manufacturing methods, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, and electric solid-state devices. It can solve the problems of reduced node contact area and device performance degradation, and achieves reduced channel leakage and increased area. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0112]The invention provides a method for manufacturing a transistor structure using a buried bit line, comprising the following steps:

[0113] See first Figure 8 , performing step S1: providing a substrate 201 in which an isolation structure 202 is disposed, and the isolation structure defines a plurality of active regions 203 in the substrate.

[0114] Specifically, the substrate 201 includes but not limited to Si, Ge, SiGe, SOI and other semiconductor substrates. The isolation structure 202 may be a shallow trench isolation (Shallow Trench Isolation, STI for short).

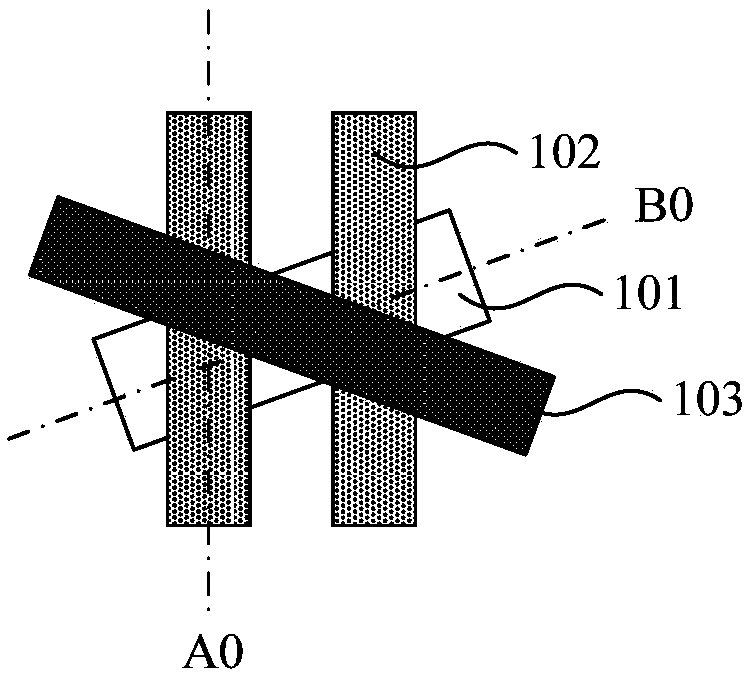

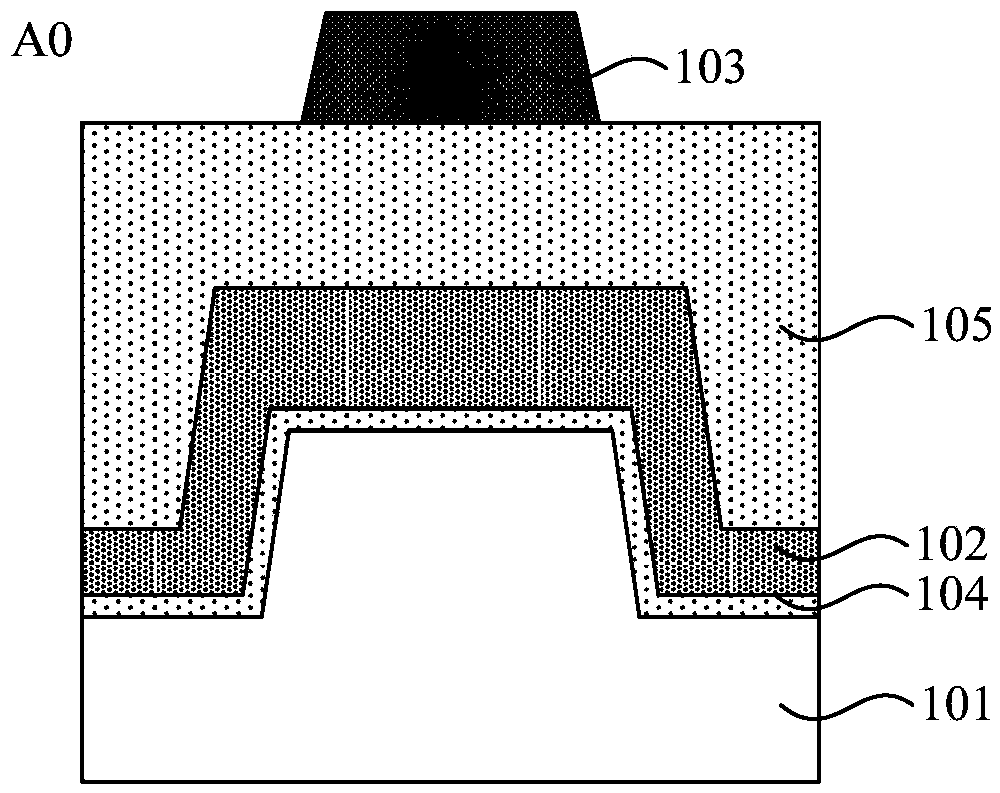

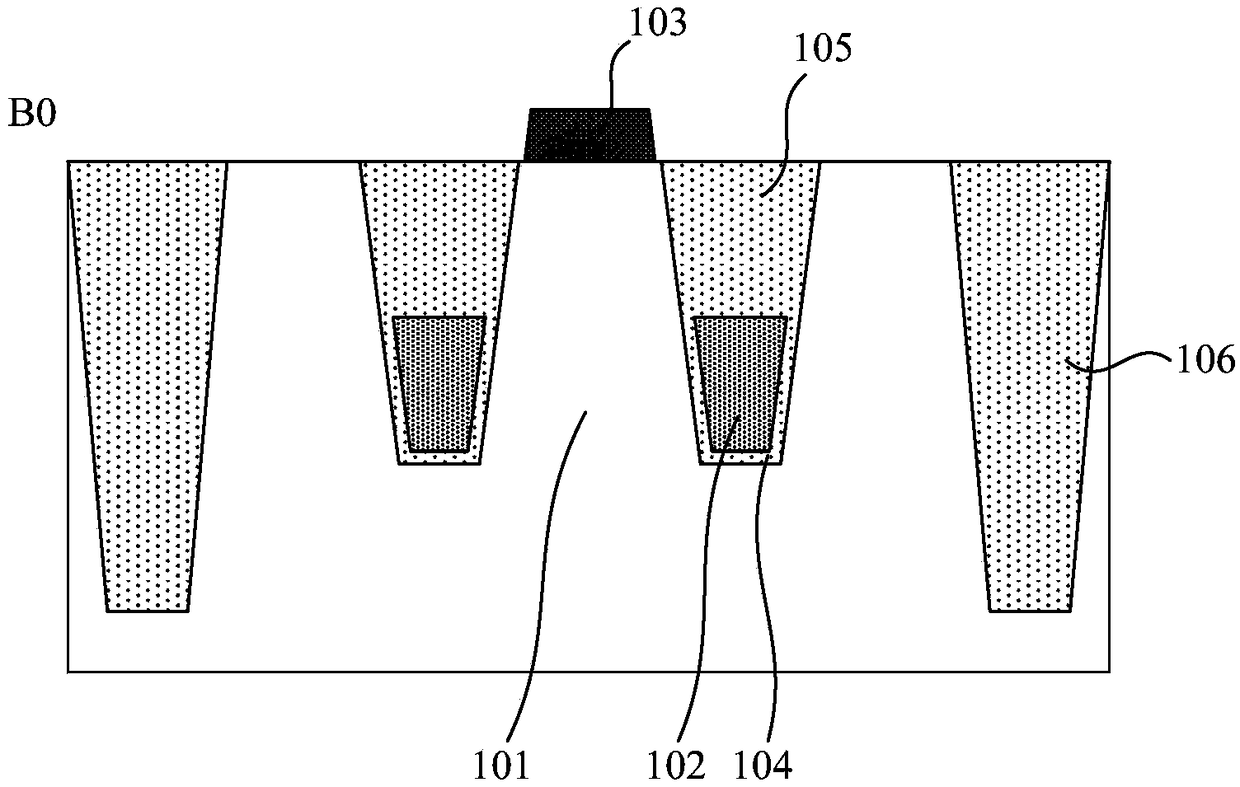

[0115] As an example, see Figure 4 , shown as a top view of a single active region 203 in the substrate, where the substrate is at Figure 4 The cross-sectional view of plane A1 is shown as Figure 5 As shown, the substrate is in Figure 4 The cross-sectional view of plane A2 is shown as Figure 6 As shown, the substrate is in Figure 4 The cross-sectional view of the A3 plane is shown as Figure 7 ...

Embodiment 2

[0145] The present invention also provides a transistor structure using a buried bit line, including a substrate, an isolation structure, a drain sinking groove, a first word line trench, a second word line trench, a buried word line and A buried bit line, wherein the isolation structure defines a plurality of active regions in the substrate, and the drain sinking groove is formed in the active regions.

[0146] see Figure 19 , shown as a single active region 203, drain sinking groove 204, first word line trench 206, second word line trench 207, buried word line 208a, buried word line 208b, From the planar layout of the bit line trench 209 and the buried bit line 210 , it can be seen that the drain sinking groove 204 overlaps the middle section of the active region 203 .

[0147] Please refer to Figure 23, which shows the transistor structure for the Figure 19 As shown in the cross-sectional view of the B1 plane, it can be seen that the first word line trench 206 and the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com