A light-emitting diode epitaxial wafer and its manufacturing method

A technology of light-emitting diodes and manufacturing methods, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of reducing the combined luminous efficiency of electrons and holes, reducing the luminous efficiency of light-emitting diodes, and dislocation of corresponding positions, so as to improve the luminous Efficiency, impact reduction, and the effect of reducing the degree of distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

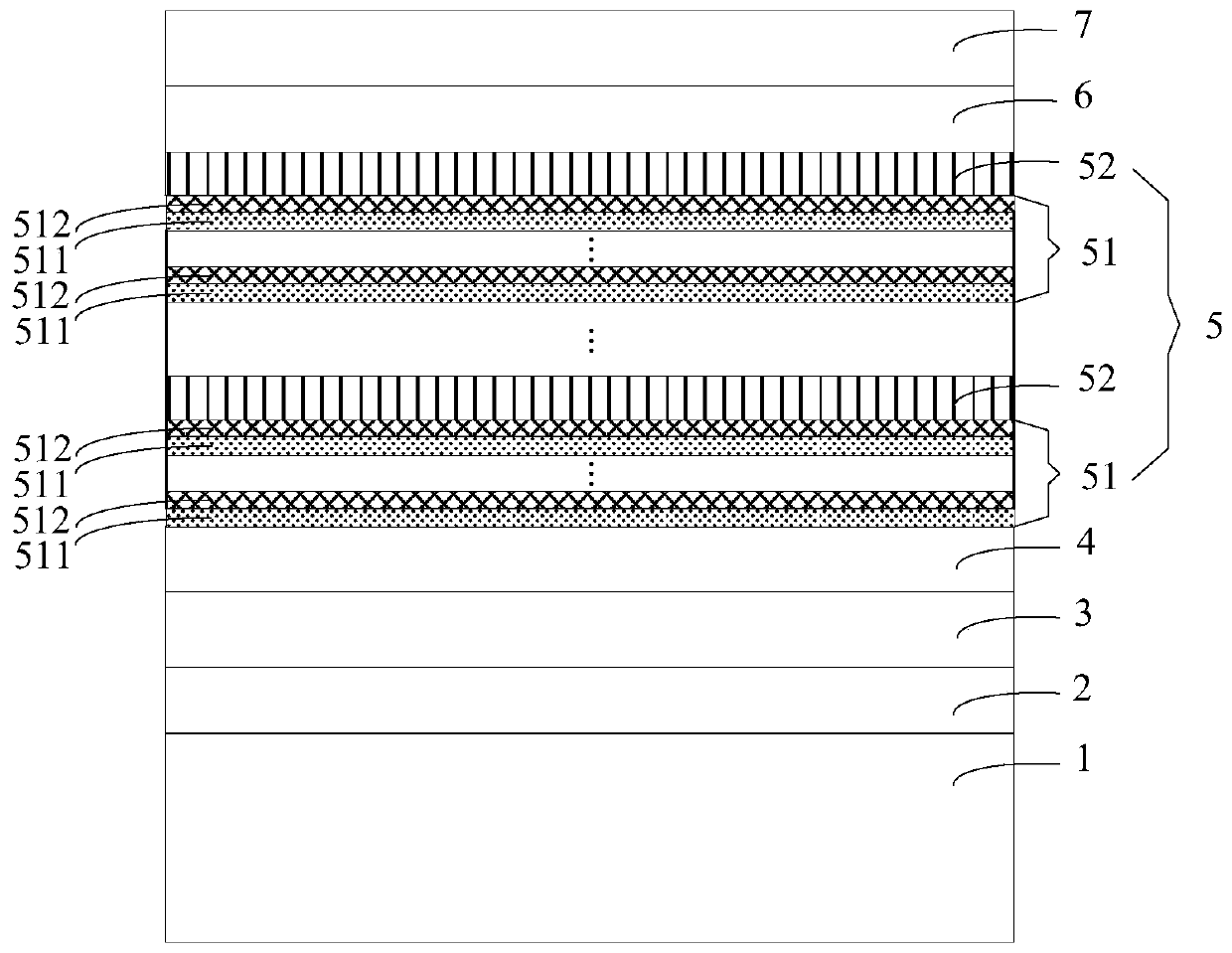

[0029] An embodiment of the present invention provides a light emitting diode epitaxial wafer, figure 1 It is a schematic structural diagram of a light-emitting diode epitaxial wafer provided by an embodiment of the present invention, as shown in figure 1 As shown, the light-emitting diode epitaxial wafer includes a substrate 1, a buffer layer 2, an undoped GaN layer 3, an N-type layer 4, an active layer 5, an electron blocking layer 6, and a P-type layer stacked on the substrate 1 in sequence. Layer 7, the active layer 5 includes a plurality of well layers 51 and barrier layers 52 alternately grown in a plurality of periods.

[0030] Each well layer 51 is a superlattice structure composed of the first sublayer 511 and the second sublayer 512, the first sublayer 511 and the second sublayer 512 are both InGaN layers, and the In in the first sublayer 511 The concentration is greater than that of In in the second sublayer 512 .

[0031] Each well layer in the active layer of th...

Embodiment 2

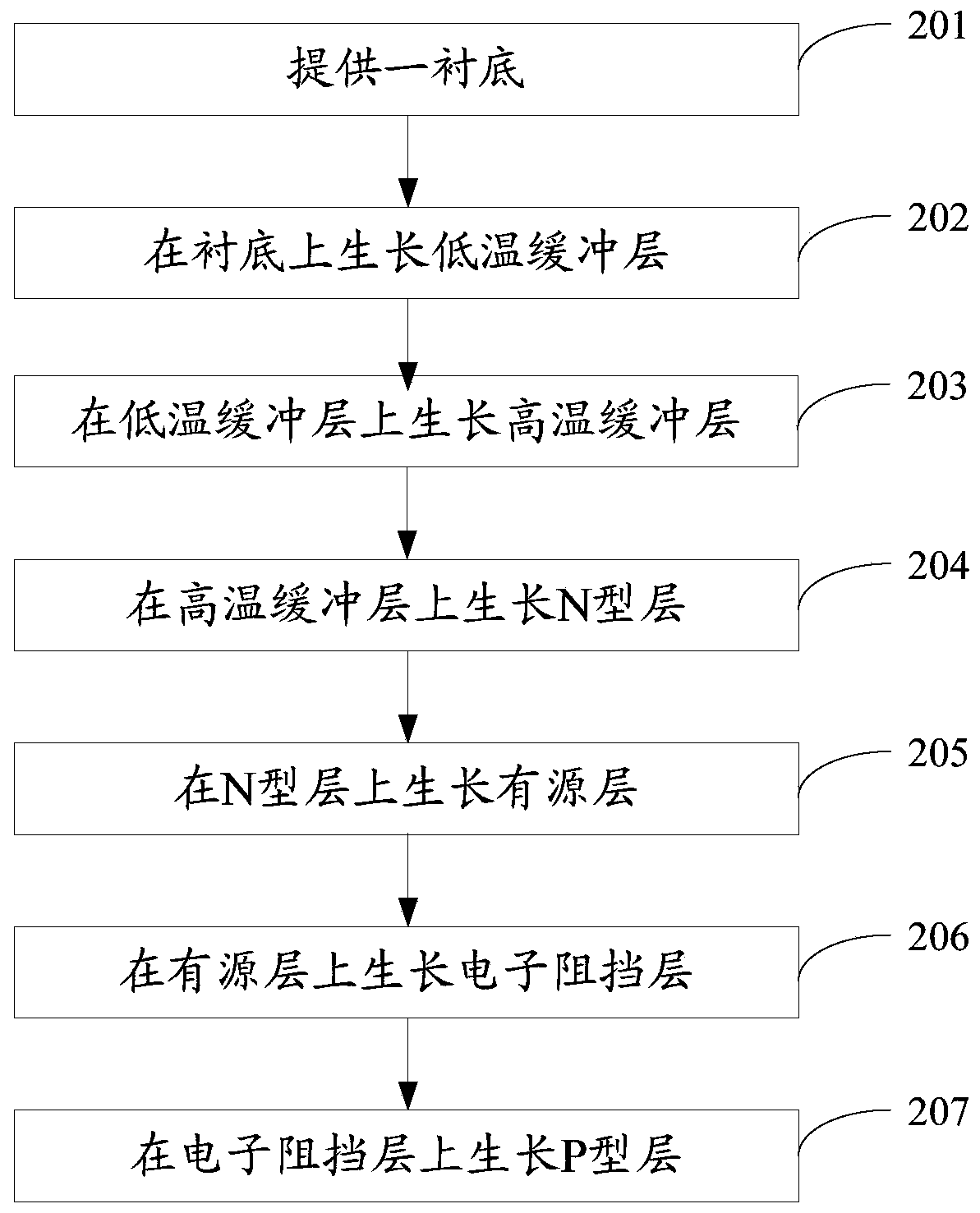

[0048] An embodiment of the present invention provides a method for manufacturing a light-emitting diode epitaxial wafer, which is used to manufacture the light-emitting diode epitaxial wafer provided in Embodiment 1, figure 2 It is a method flowchart of a method for manufacturing a light-emitting diode epitaxial wafer provided by an embodiment of the present invention, as shown in figure 2 As shown, the manufacturing method includes:

[0049] Step 201, providing a substrate.

[0050] Optionally, the substrate is sapphire.

[0051] Specifically, this step 201 includes:

[0052] Under a hydrogen atmosphere, treat the substrate at high temperature for 5-6 minutes. Wherein, the temperature of the reaction chamber is 1000-1100° C., and the pressure of the reaction chamber is controlled at 200-500 torr.

[0053] Step 202, growing a low-temperature buffer layer on the substrate.

[0054] In this embodiment, Veeco K465i or C4MOCVD (Metal Organic Chemical Vapor Deposition, Meta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More