Multi-chip package interconnection structure and multi-chip package interconnection method

A technology of multi-chip packaging and interconnection structure, applied in the field of electronics, can solve the problems of difficult to verify the reliability effectively, complicated manufacturing process, short interconnection length, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In view of the deficiencies in the prior art, the inventor of this case was able to propose the technical solution of the present invention after long-term research and extensive practice. The technical solution, its implementation process and principle will be further explained as follows.

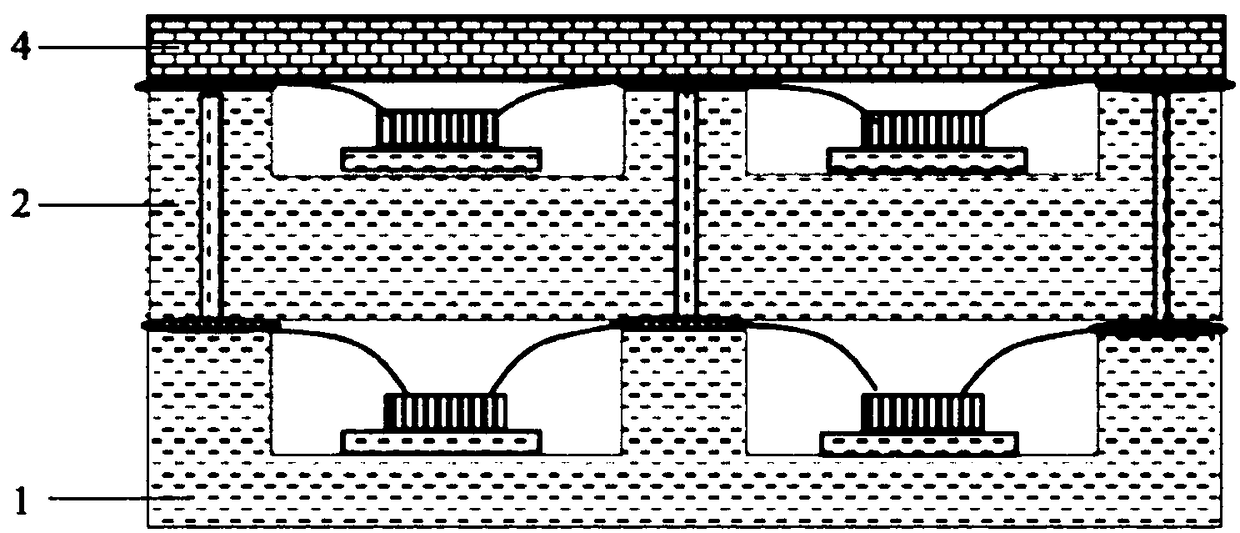

[0021] An embodiment of the present invention provides a multi-chip packaging and interconnection structure, including:

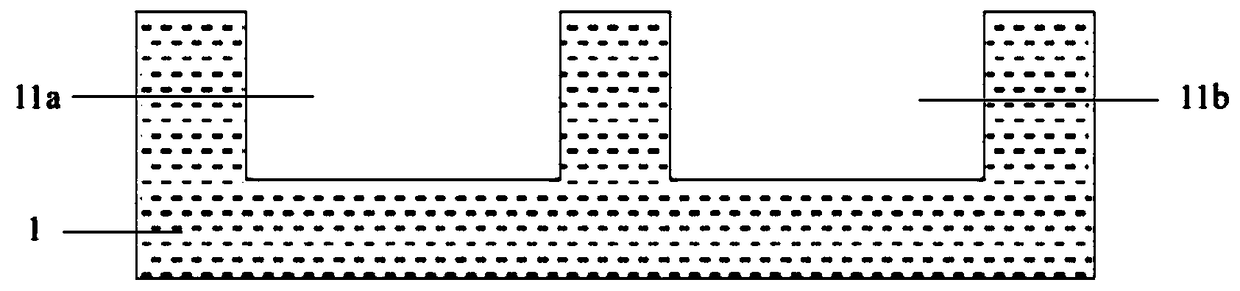

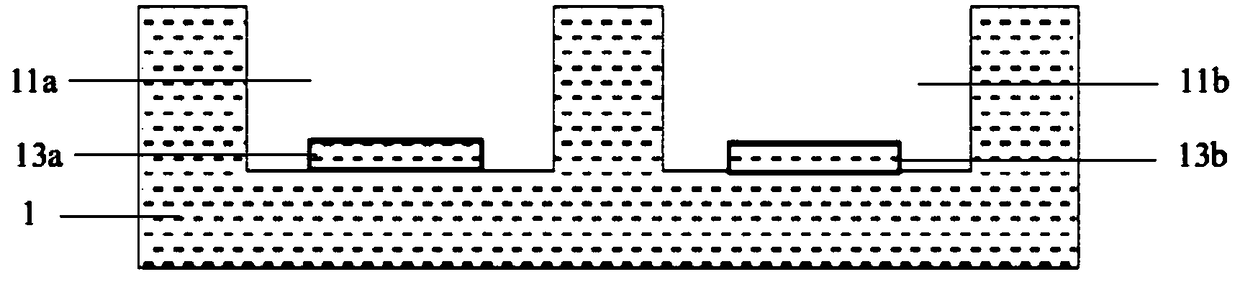

[0022] a first substrate and a second substrate arranged in layers;

[0023] A plurality of first cavities are provided on the first substrate, a plurality of first chips are provided in the first cavities, a first pad is provided on the upper surface of the first substrate, and the first pad is electrically connected to the first chip;

[0024] A plurality of second cavities are provided on the second substrate, a plurality of second chips are provided in the second cavities, a second pad is provided on the upper surface of the second substrate, and the second...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More