A SoC prototype verification method based on FPGA

A prototype verification, interface control module technology, applied in the direction of instruments, electrical digital data processing, computing, etc., can solve problems such as low visibility of test signals, and achieve the effect of shortening implementation time, high practical value, and reducing FPGA storage resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] A kind of concrete steps of SoC prototype verification method based on FPGA are:

[0026] The first step is to build a SoC prototype verification system

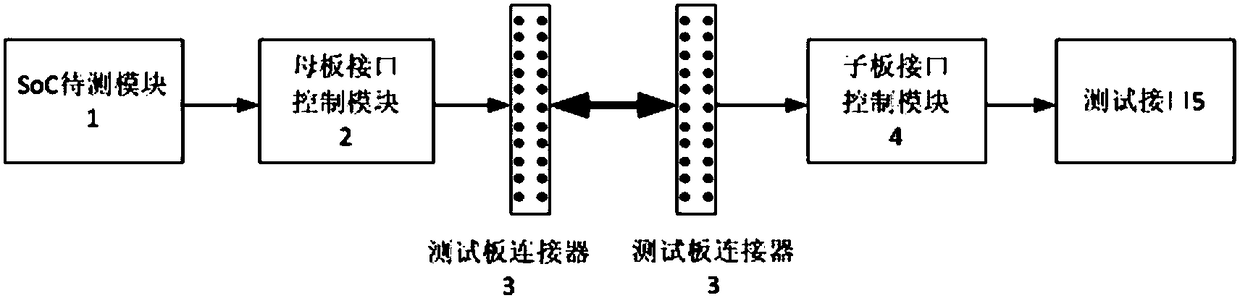

[0027] The SoC prototype verification system includes: a SoC module to be tested 1 , a motherboard interface control module 2 , a test board connector 3 , a daughter board interface control module 4 and a test interface 5 .

[0028] The Soc module 1 to be tested is connected to the motherboard interface control module 2, the motherboard interface control module 2 is connected to the test board connector 3, the test board connector 3 is connected to the daughter board interface control module 4, and the daughter board interface control module 4 is connected to the test board Interface 5 is connected. There are multiple test interfaces 5 .

[0029] The function of the Soc module 1 to be tested is to simulate the function of the SoC chip, and connect the signal to be tested with the motherboard interface control module...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More