6t storage unit structure of sram

A technology of memory cells and active areas, applied in electrical components, semiconductor devices, transistors, etc., can solve the problems of device mismatch, affecting device matching, and inconsistency in dimensional changes, so as to eliminate the mismatch in width and length, improve Good matching and consistency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

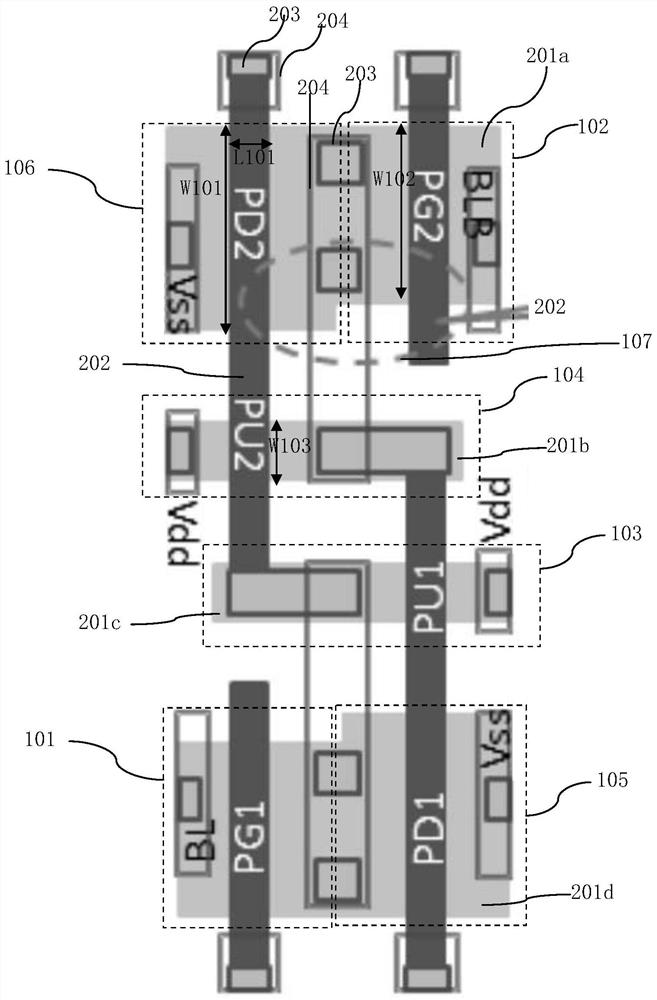

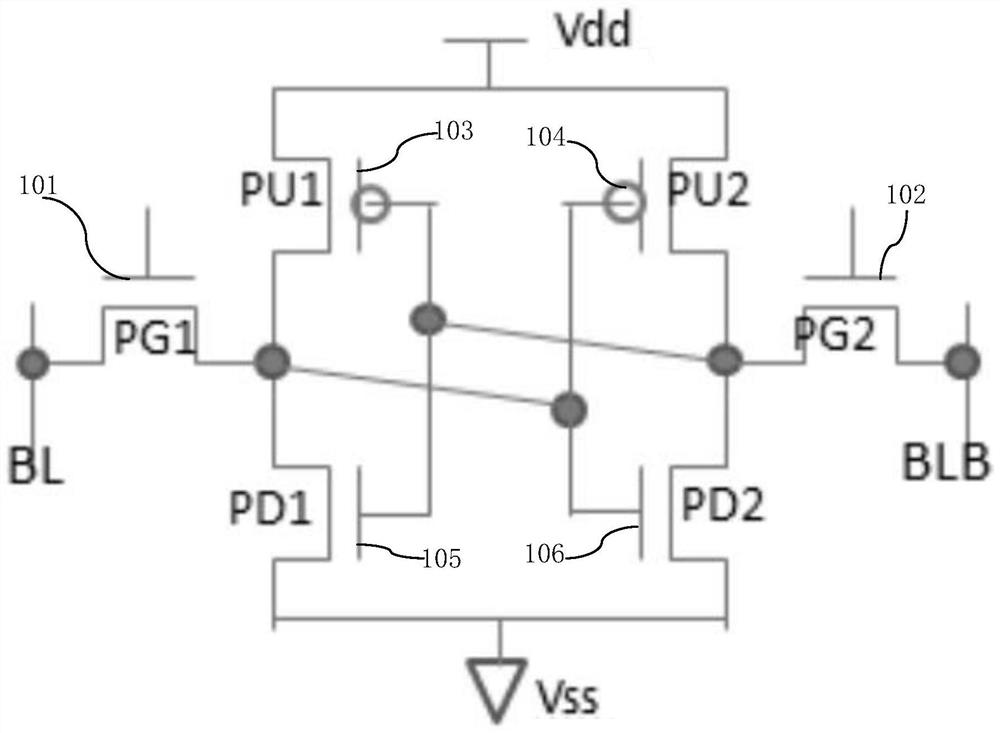

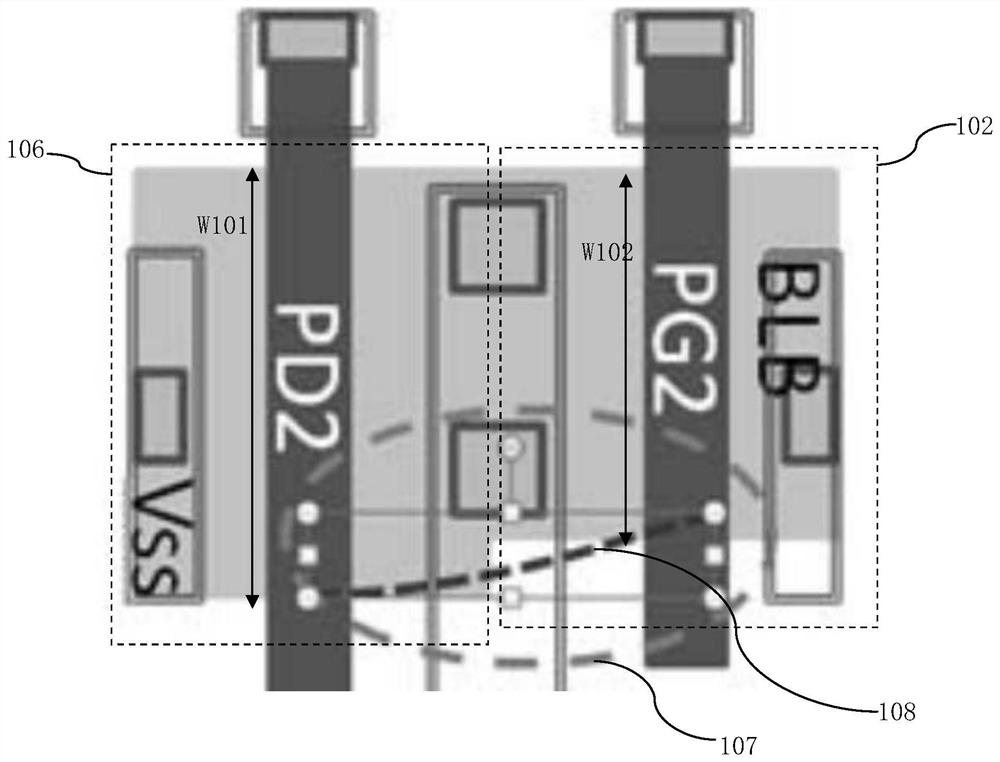

[0061] Such as Figure 4 Shown is the layout of the 6T memory cell structure of the SRAM of the embodiment of the present invention; Figure 5 yes Figure 4 The circuit diagram of the 6T memory cell structure of the SRAM in the embodiment of the present invention is shown, the 6T memory cell structure of the SRAM in the embodiment of the present invention consists of a first selection transistor 1, a second selection transistor 2, a first PMOS transistor 3, and a second PMOS transistor 4 The first NMOS transistor 5 and the second NMOS transistor 6 are connected to form six transistors, the first PMOS transistor 3 and the second PMOS transistor 4 are used as two pull-up transistors (Pull Up, PU), and the The first NMOS transistor 5 and the second NMOS transistor 6 serve as two pull down transistors (Pull Down, PD). Figure 4 Among them, the first selection transistor 1 is also represented by PG1, the second selection transistor 2 is also represented by PG2, the first PMOS tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com