Back surface structure of IGBT chip, IGBT chip structure and preparation method thereof

A backside structure and chip technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, transistors, etc., can solve the problems of current concentration process manufacturing cost in the transition zone, avoid local over-temperature or over-current failure, and save photolithography Process, the effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

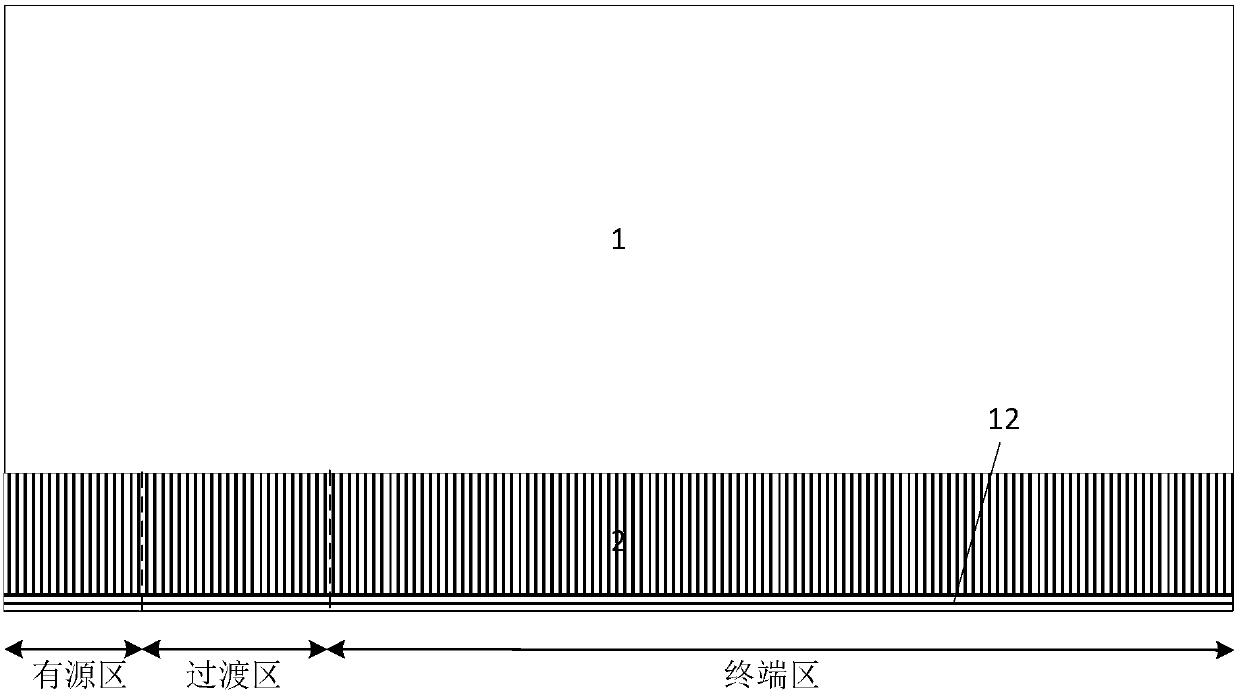

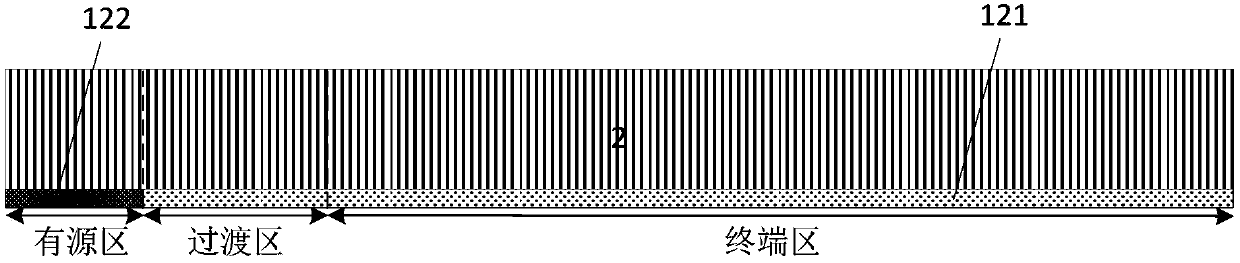

[0047] An embodiment of the present invention provides a backside structure of an IGBT chip, including: a buffer layer 2 and a doped layer 12, wherein the doped layer 12 is formed by ion implantation at a first preset depth of the buffer layer 2; The doped layer in the terminal region and the transition region of 2 is subjected to the first preset high temperature annealing treatment; the doped layer located in the active region of the buffer layer 2 is subjected to the first preset high temperature annealing treatment and the second preset high temperature annealing treatment. The first preset high-temperature annealing treatment is furnace tube annealing treatment, the annealing temperature is 350-500°C, and the annealing time is 30-120min; the second preset high-temperature annealing treatment is laser annealing treatment, the laser wavelength is 500nm-700nm, and the laser energy is 0.8J-4.0 J, the above is just an example, not a limitation.

[0048] In the embodiment of th...

Embodiment 2

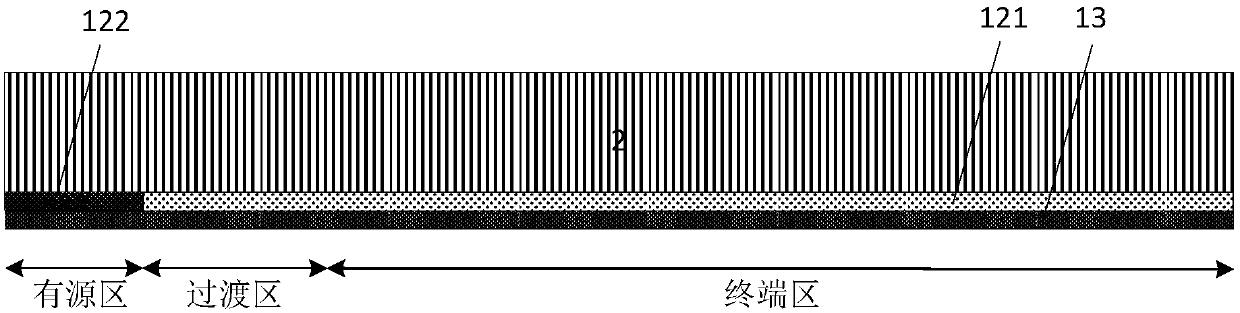

[0054] The back structure of the IGBT chip provided by the embodiment of the present invention, such as Figure 4 As shown, the back structure of the IGBT chip includes: a buffer layer 2, a doped layer 3 and a defect layer 11, wherein the structure and manufacturing process of the buffer layer 2 and the doped layer 3 are the same as those of the back side of the IGBT chip in Example 1. The structure of the buffer layer 2 and the doped layer 3 is the same, and will not be repeated here. The defect layer 11 is formed by performing ion implantation at a second predetermined depth of the buffer layer, the second predetermined depth is greater than the above-mentioned first predetermined depth, and the defect layer 11 penetrates the active region, the transition region and the terminal of the buffer layer 2 Area. In one embodiment, the defect layer 11 is formed by implanting inert ions into the buffer layer, specifically, the inert ions can be argon ions, and the implantation dose...

Embodiment 3

[0058] An embodiment of the present invention provides an IGBT chip structure, including: the front structure of the IGBT chip and the back structure of the IGBT chip described in Embodiment 1 or Embodiment 2. The IGBT front-side process is carried out on the substrate 1 made of silicon material. The front-side structure includes: a voltage-resistant field ring 31 in the terminal area, a polysilicon field plate 7, a metal field plate 81, a stop ring 41 and a passivation layer 10. The active area is light Doping P-type 3 and heavily doping P-type 4, N-type emitter 5, gate oxide layer 6, polysilicon field plate 7, oxide layer 9 and active region metal layer 8, forming a structure such as Image 6 Shown is just an example, not a limitation.

[0059] The IGBT chip structure provided by the embodiment of the present invention can not only realize different hole injection efficiencies between the collector active region and the terminal region on the back of the IGBT, improve the cu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More