Chip packaging structure and chip packaging method

A chip packaging structure, chip technology, applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problems affecting the heat dissipation performance of the chip packaging structure, and achieve the effect of improving heat dissipation efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

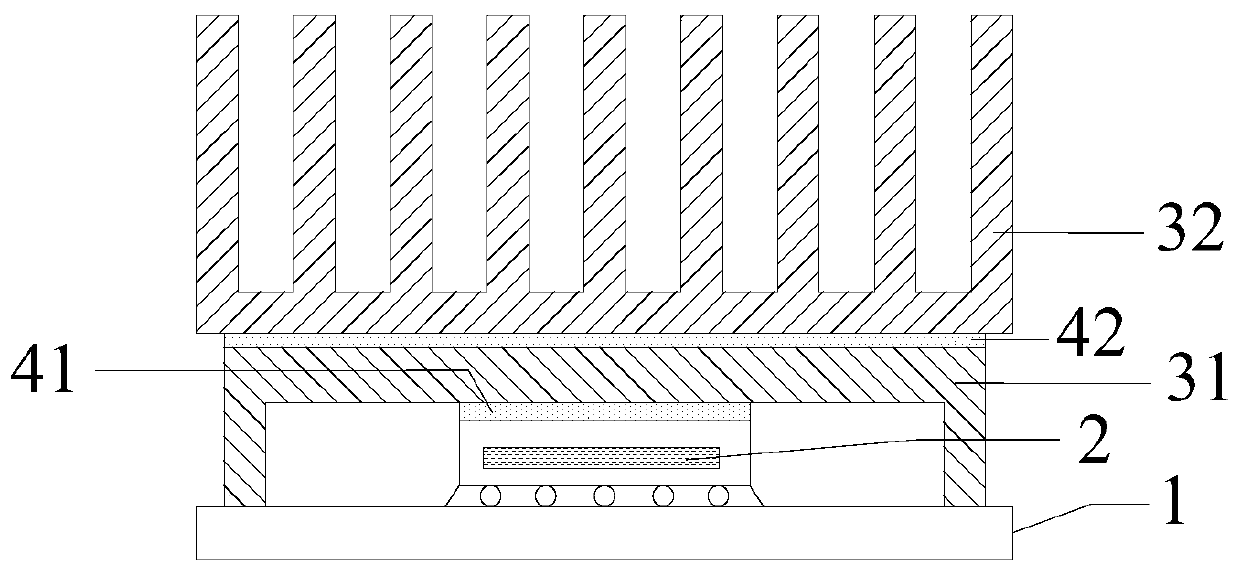

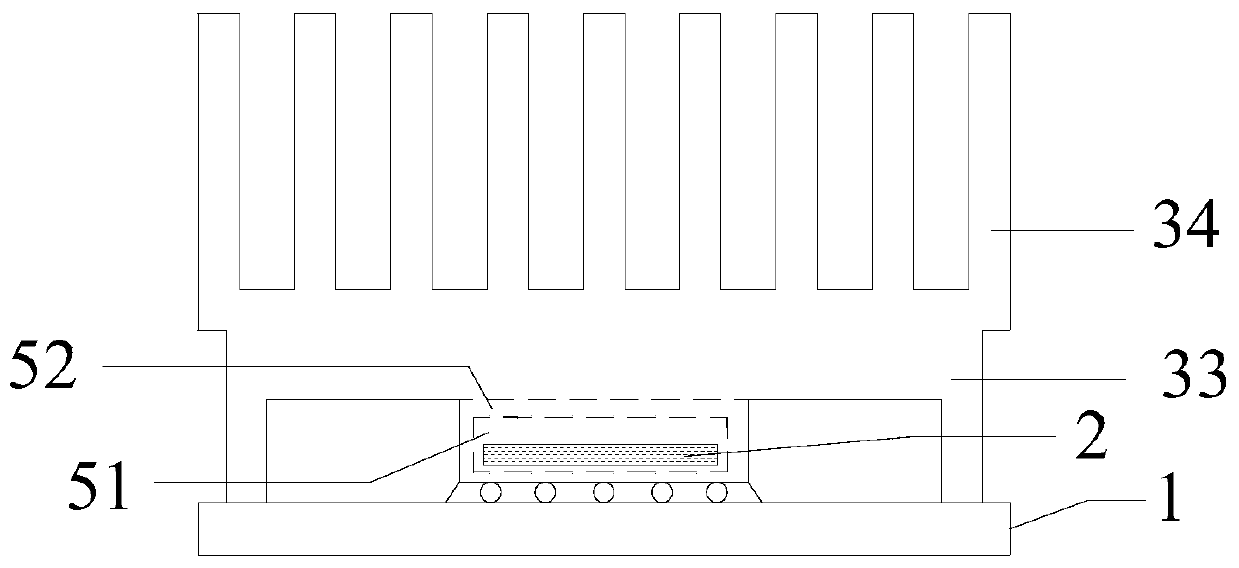

[0032] figure 2 is a schematic diagram of a chip package structure according to an embodiment of the present invention, such as figure 2 As shown, the chip package structure includes: a carrier board 1, a chip 2, a thermally conductive insulating layer and a heat sink. The heat sink includes a horizontal portion above the outer side of the thermally conductive insulating layer and a vertical portion extending from these positions close to the carrier board 1. The package cover structure 33 of the vertical part of the package cover 33 and the heat sink structure 34 formed by several groups of vertical bracket-like structures above the package cover 33, the heat conduction insulation layer includes a flexible heat conduction layer 51 wrapped on the outside of the chip 2 and a flexible heat conduction layer located on the flexible heat conduction layer. Semi-solid thermally conductive layer 52 on the outside of layer 51 . The package cover structure 33 mainly plays a certain r...

Embodiment 2

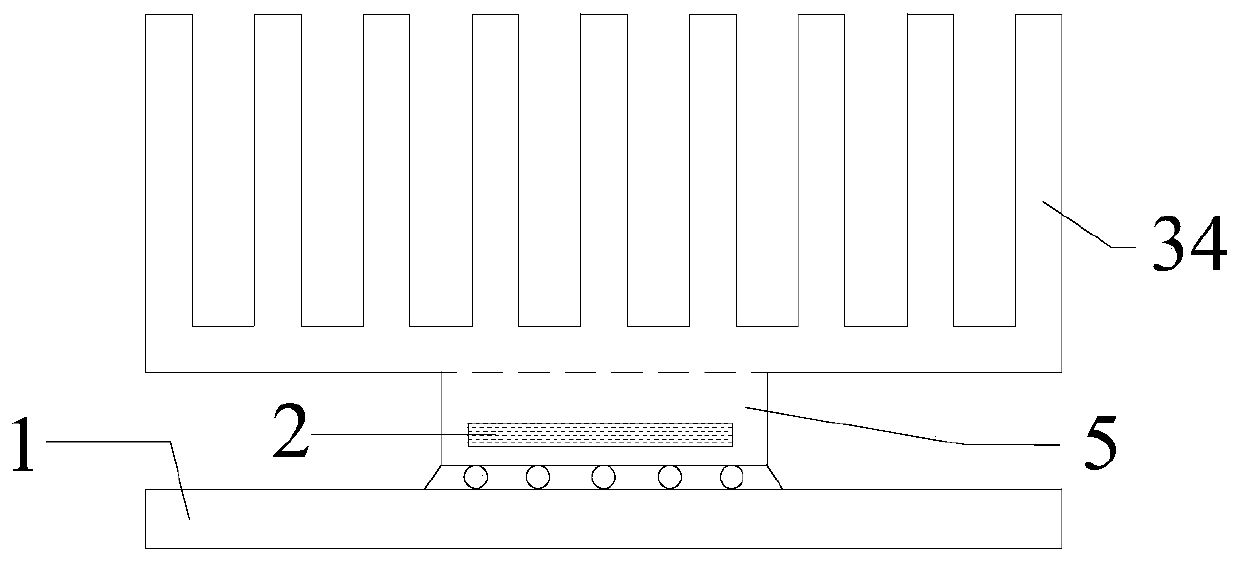

[0041] image 3 is a schematic diagram of a chip package structure according to another embodiment of the present invention. Such as figure 2As shown, the difference between the chip package structure and the embodiment 1 is that the structural setting of the package cover is omitted, and the two parts of the thermally conductive insulating layer 5 and the heat sink structure 34 are in direct contact; at the same time, in this embodiment, the flexible thermally conductive The raw materials of the layer are all silicone grease, and the raw materials of the semi-solid heat conduction layer are 60wt% of silicone grease, 20wt% of diamond, and 20wt% of silicon dioxide. Wherein, the arrangement, shape, and structure of the flexible heat-conducting layer and the semi-solid heat-conducting layer are the same as those in Embodiment 1.

Embodiment 3

[0043] Figure 4 It is a schematic diagram of a chip package structure according to another embodiment of the present invention. Such as image 3 As shown, a chip 2 is mounted on a carrier 1 , and the outer side of the chip 2 is covered with a thermally conductive insulating layer 5 . Above the thermally conductive insulating layer 5 is the package cover structure 33 , and the package cover structure 33 in this embodiment is packaged with carbon fiber-reinforced resin composite wires and boron nitride fiber-reinforced resin composite wires with high thermal conductivity. Also on the package lid structure 33 is a vapor chamber structure 35 . The amount of thermally conductive filler in the vapor chamber structure 35 is slightly more than that in the package cover structure, so as to achieve better heat dissipation.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More