A fpga-based national secret algorithm acceleration processing system

A national secret algorithm and processing system technology, applied in the field of national secret algorithm acceleration processing system, can solve the problems of poor scalability and low throughput, and achieve high throughput, good scalability and good reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

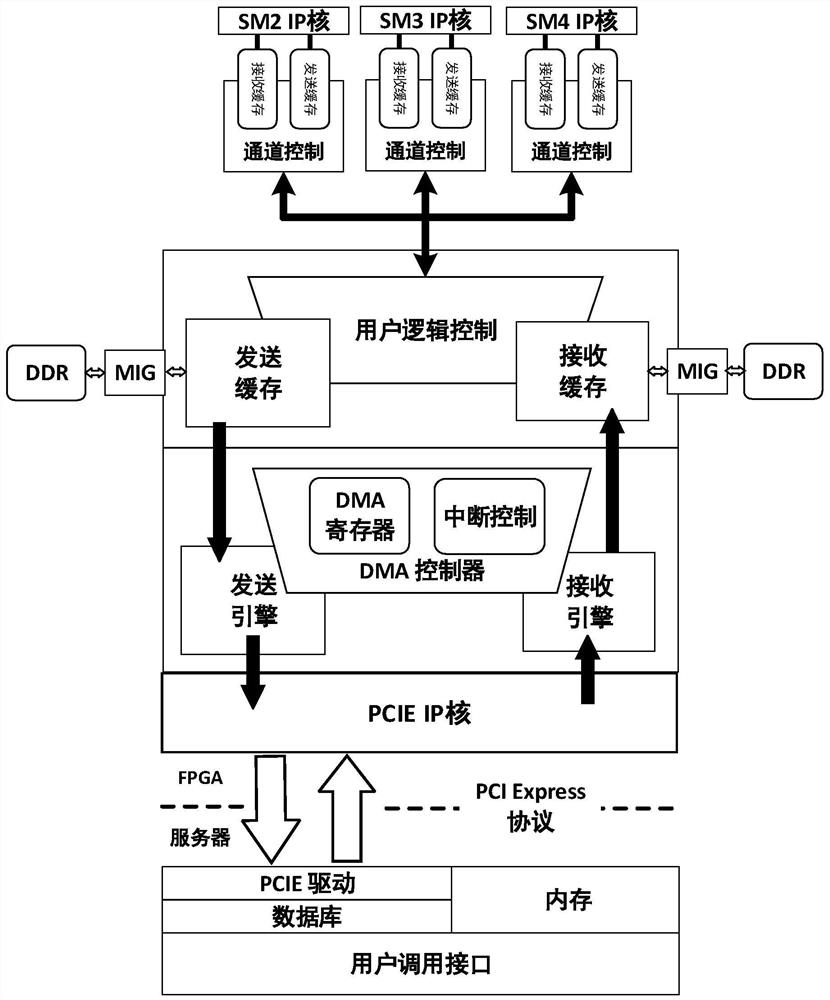

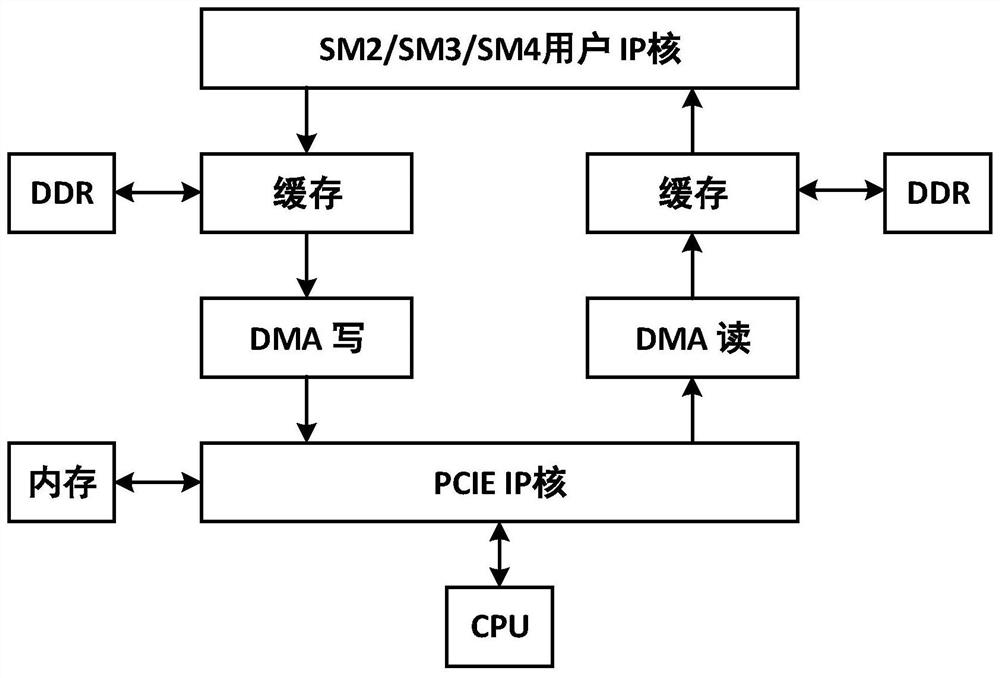

[0034] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings. These embodiments are used to illustrate the present invention without limiting the scope of the present invention.

[0035]National secret algorithms (SM2 / SM3 / SM4) are mainly used for encryption protection and security authentication of commercial information. With the development of high-speed networks, the demand for high-speed encryption and decryption of network data packets based on national secrets has become very urgent. However, the domestic encryption chips (Z8IDA chip, LKT4305 chip) in the current market adopt I 2 C bus transmission mode, the throughput rate is very low. Other publicly reported national secret hardware implementation schemes failed to achieve the throughput rate required by high-speed networks, and due to the limitations of their own system architecture, the scalability was poor, and it was inconvenient to expand int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More