Large-size chip system package structure with flexible adapter plate and manufacturing method thereof

A chip system and packaging structure technology, applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve problems such as unfavorable signal transmission and data processing, large system size, and inability to meet packaging requirements. , to avoid the height difference of solder balls

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

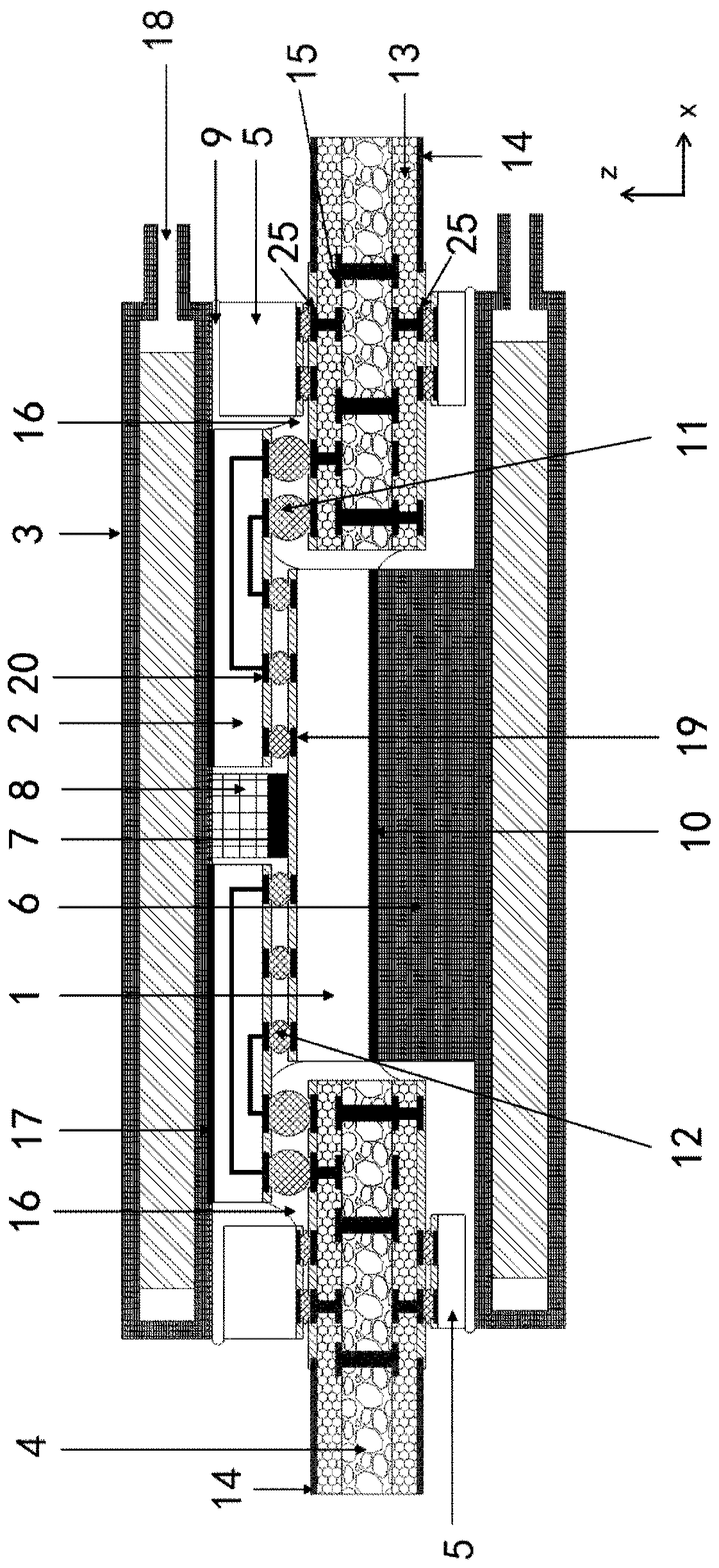

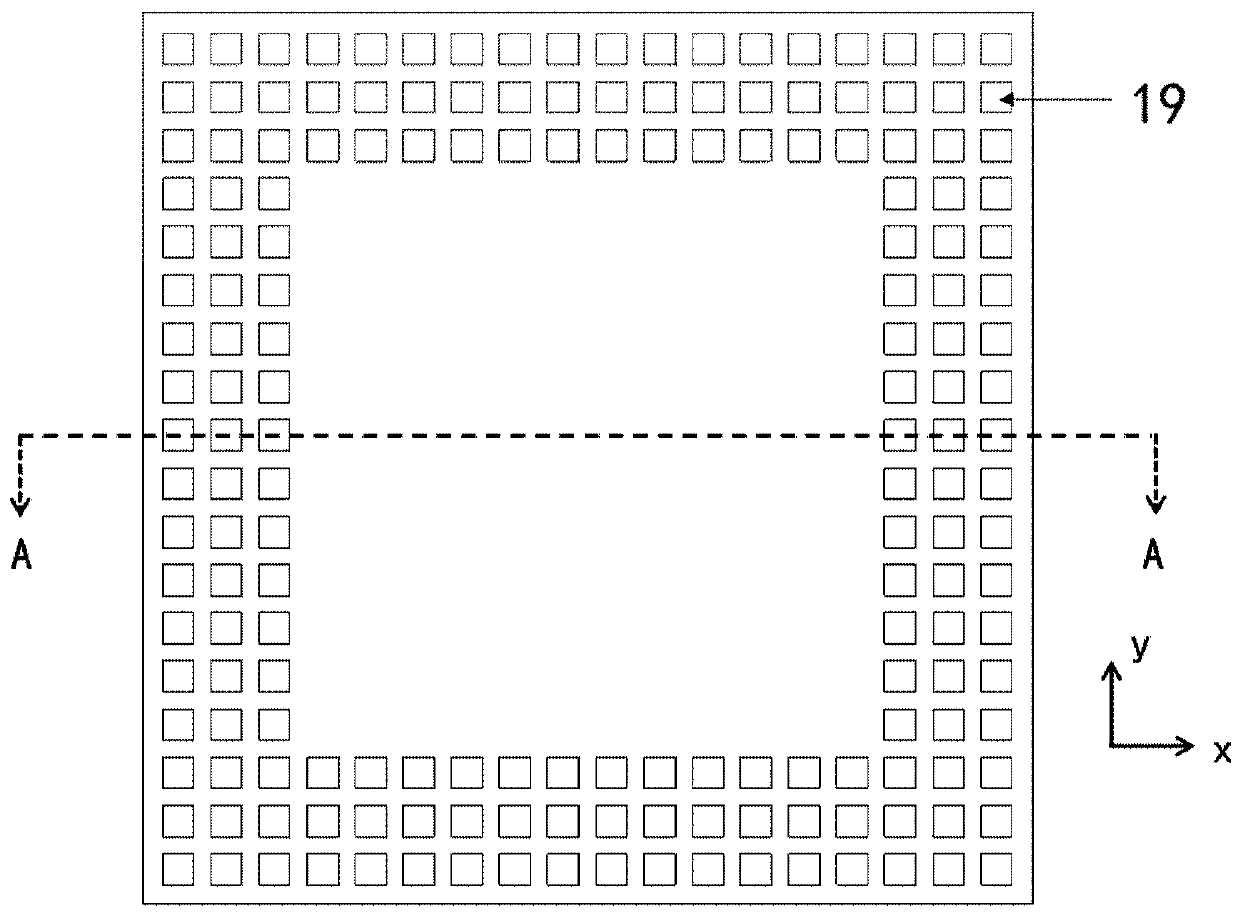

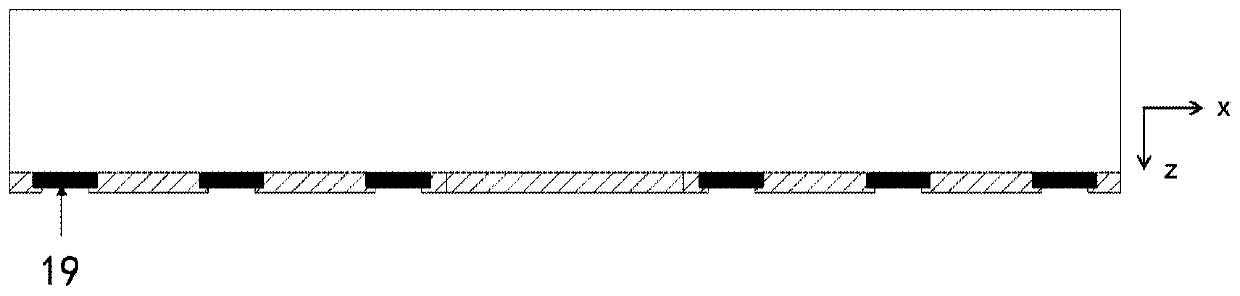

[0060] The present disclosure provides a large-size system-on-chip packaging structure with a flexible interposer. The large-scale system-on-a-chip package structure with a flexible interposer avoids virtual soldering of large-sized chips or other poor soldering problems while ensuring The heat dissipation effect is good. Of course, the large-size chip system packaging structure with a flexible interposer of the present disclosure can be used to simultaneously package one or more large-size chips and / or small-size chips, as well as multiple components. The components can be It is a flip-chip or other type of components, which realizes the packaging and heat dissipation of system functions, and avoids the problem of virtual soldering of large-size chips.

[0061] to combine figure 1 , Figure 7 and Figure 13 As shown, the large-scale chip system packaging structure with a flexible interposer of the present disclosure includes: a flexible interposer 2, which is provided with ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap