TSV (Through-Silicon-Via) packaging structure and preparation method thereof

A packaging structure and enhanced structure technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as incomplete guarantee of structural strength and warpage, and achieve reduced TSV cost, low CTE, high intensity effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment

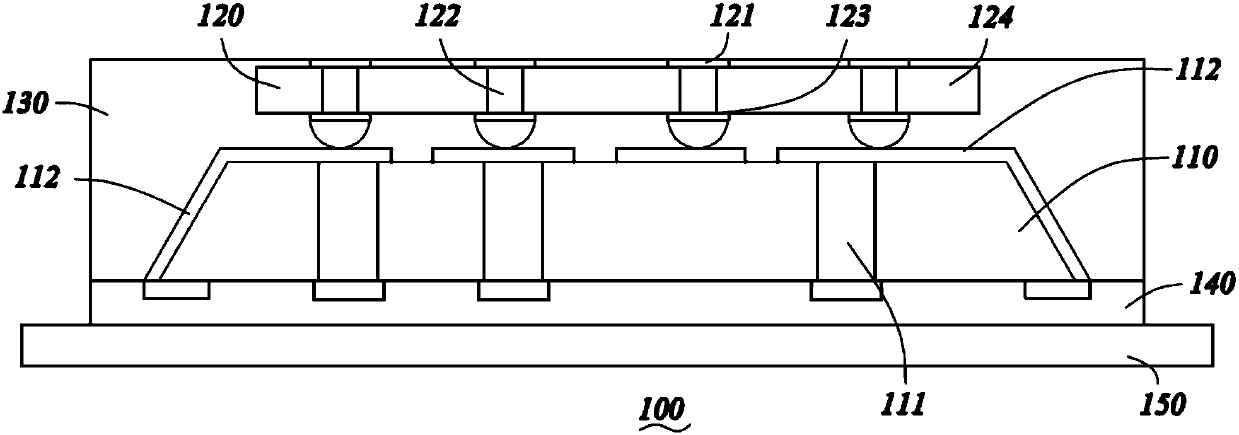

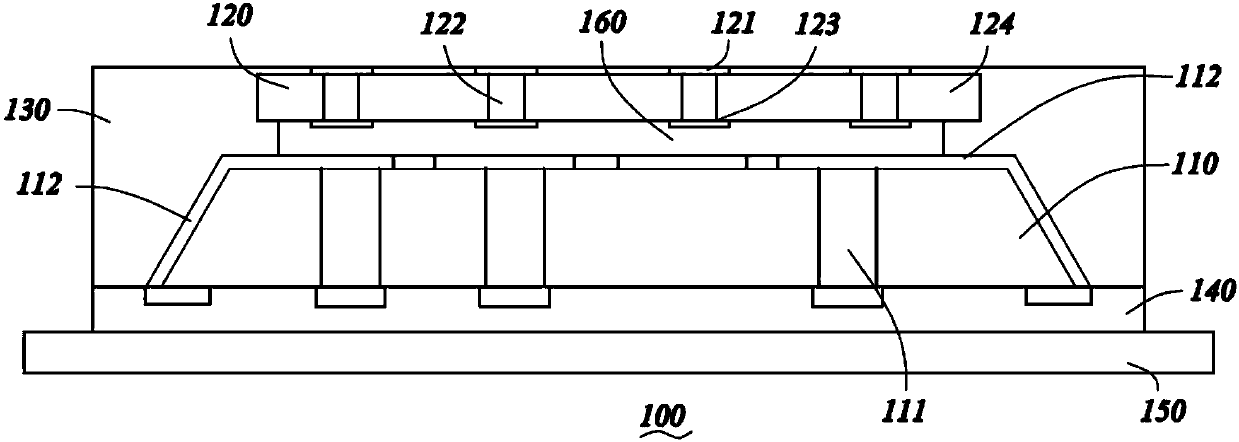

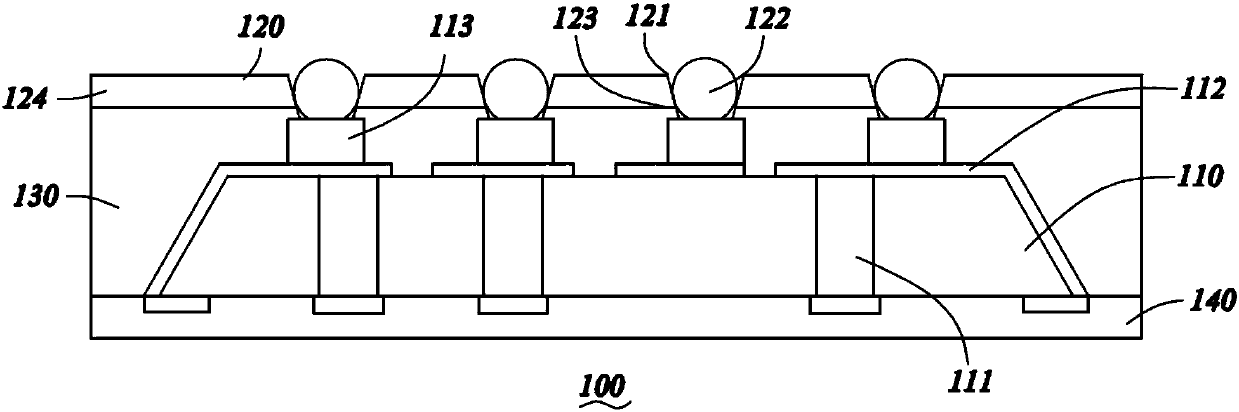

[0038] ginseng figure 1 As shown, the present invention proposes a TSV packaging structure 100. The TSV packaging structure 100 includes a TSV wafer 110. At the same time, the TSV wafer 110 includes a number of first through holes 111 etched through. The inner walls of the first through holes 111 are coated with There is conductive material to make the front and back of the TSV wafer 110 electrically connected. In this embodiment, the first through holes 111 are arranged vertically.

[0039] Further, connecting lines 112 are selectively laid on the back and side of the TSV wafer 110 to realize the connection between circuits disposed on the back and side of the TSV wafer 110 .

[0040] Further, the TSV package structure 100 also includes a reinforcement structure 120 assembled to the back of the TSV wafer and electrically connected to the connection line 112. Specifically, the assembly method proposed in the present invention includes flip-chip or front-mount, and the common p...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap