Low-power consumption boundary scanning test method

A technology of boundary scan testing and boundary scan, which is applied in the direction of electronic circuit testing, measuring electronics, measuring devices, etc., and can solve problems affecting test results, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

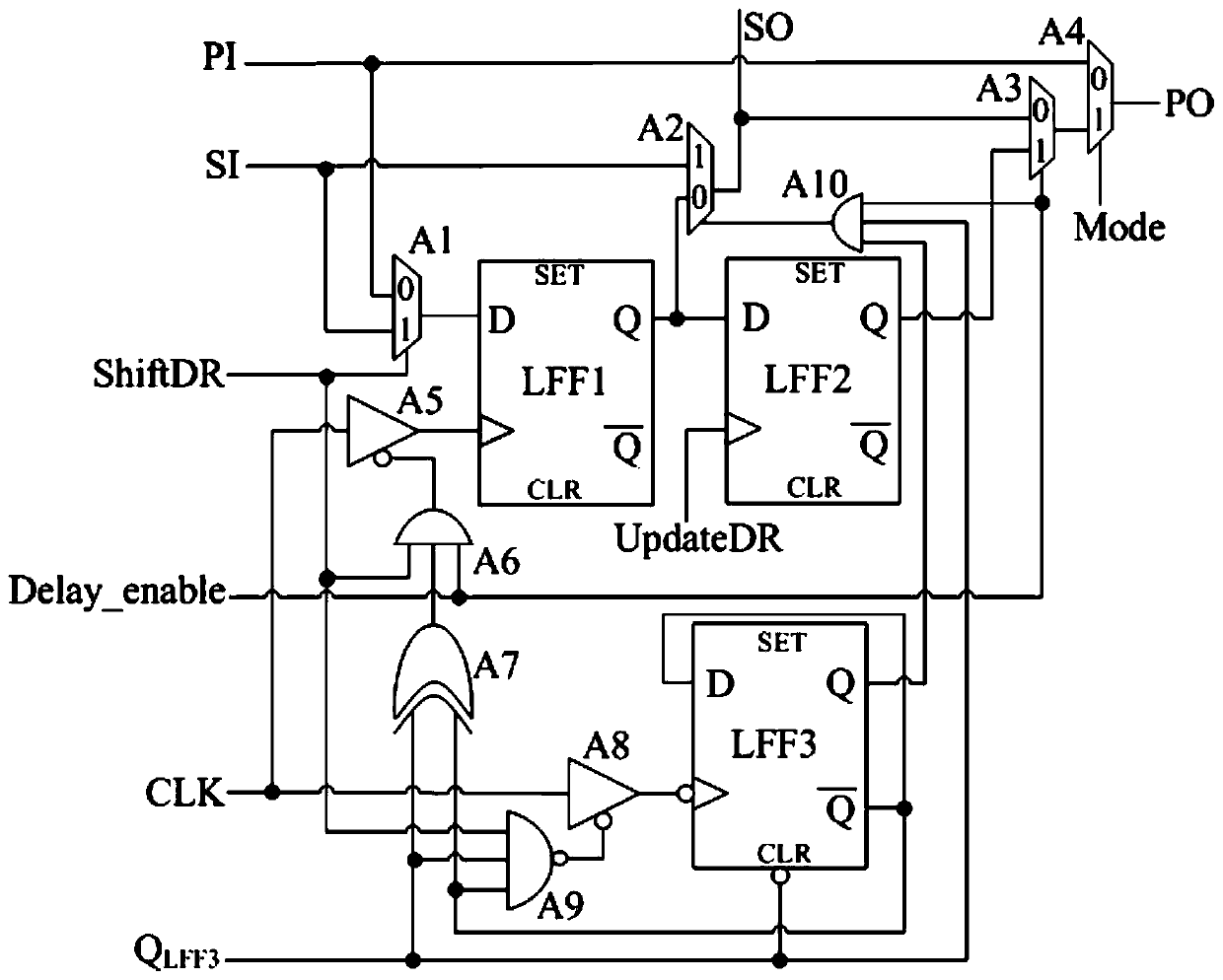

[0078] Specific implementation mode 1. In the non-delay test mode, the specific working process of the input boundary scan chain:

[0079] Capture phase: see Figure 5(a), Delay_enable is 1, CLK is the test clock; ShiftDR is 0, and the initial value 0 is set to the D flip-flop LFF3; at the same time, control the tri-state gate A5 of the LFF1 clock terminal (active low) is turned on, BSCC1 can capture the response of the previous test process into LFF1 through the system input terminal PI under the trigger of the clock.

[0080] Shift phase: See Figure 5(b). When the control signal ShiftDR changes from 0 to 1, the test enters the shift phase, and at the same time, the tri-state gate A8 that controls the LFF3 clock terminal in BSLC1 is opened. The test vector is sequentially input from the test serial input terminal SI bit by bit. When the rising edge of the first test clock arrives, the first bit of the test vector is shifted into LFF1 of BSLC1. When the falling edge of the fir...

specific Embodiment approach 2

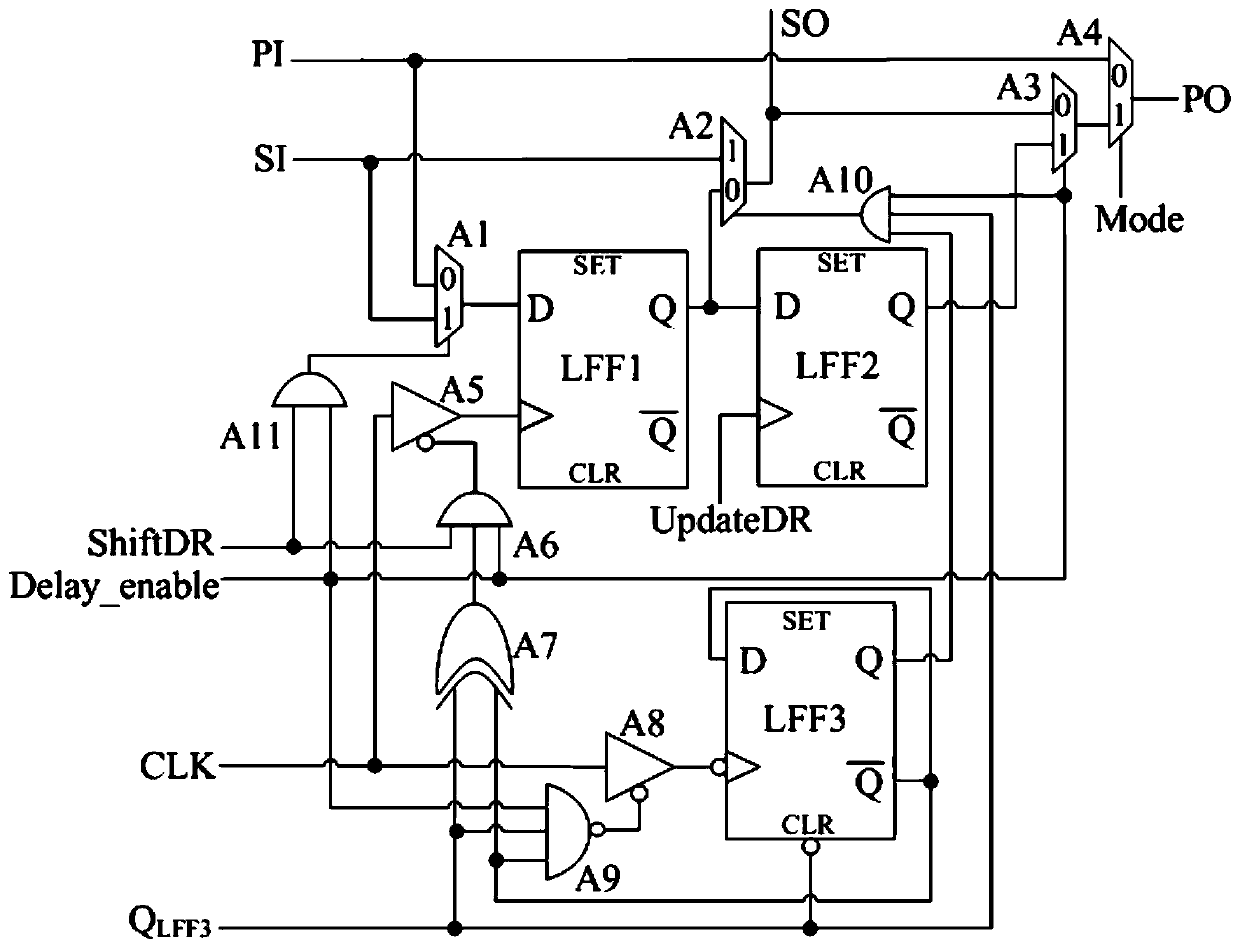

[0088] Specific implementation mode 2. In the full-speed test mode, the specific working process of the input boundary scan chain:

[0089] In full-speed testing, the boundary-scan cell skips the capture phase and goes directly to the shift phase, which moves the test vectors into the scan chain. After the shift is completed, the Delay_enable signal changes from 1 to 0, and the scanning unit enters the full-speed test mode.

[0090] Specifically: the initial Delay_enable is 1, CLK is the test clock; perform a shift to move the test vector into the scan chain;

[0091] After the shift is completed, the Delay_enable signal changes from 1 to 0, and the input clock is switched to the functional clock. At the same time, the test vector is applied to the functional path through the PO terminal of the BSLC scanning unit as its initial logic value;

[0092] When the first rising edge of the function clock arrives, the scan chain performs another shift, and the logic value conversion ...

specific Embodiment approach 3

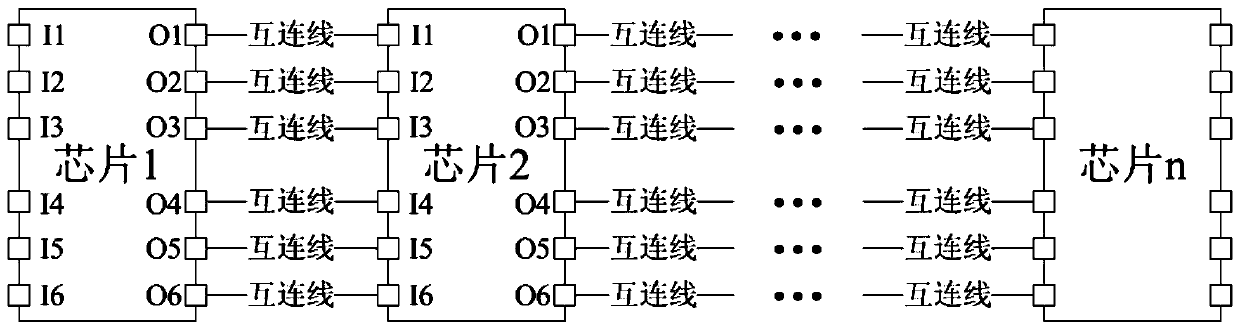

[0097] Specific embodiment three, combine Figure 7-10 This embodiment will be described, and simulation experiment data will be given in this embodiment.

[0098] In order to verify whether the present invention can correctly complete operations in different test phases such as shift, capture, and update and reduce test power consumption, we perform functional simulation on a boundary-scan unit with low test power consumption. In the experiment, 16 boundary scan units are used to form a scan chain to simulate the test vector shift process, including 8 emission units and 8 capture units. The test clock frequency is set to 100MHz. It is worth noting that the PI-side input signal and PO-side output signal mentioned in the experiment are two 16-bit signals, which are the test vector SI_LC and the test response SO_CC, which represent the system input and output ports PI and PO in the boundary scan unit. the value of figure 1 The data values at PI and PO marked in ; SOi repres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More