Gallium oxide field effect transistor using stannous oxide to adjust threshold voltage and preparation method

A stannous oxide and gallium oxide field technology, applied in circuits, transistors, electrical components, etc., can solve the problem of large threshold voltage of field effect transistors, and achieve the effect of improving the utilization value

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

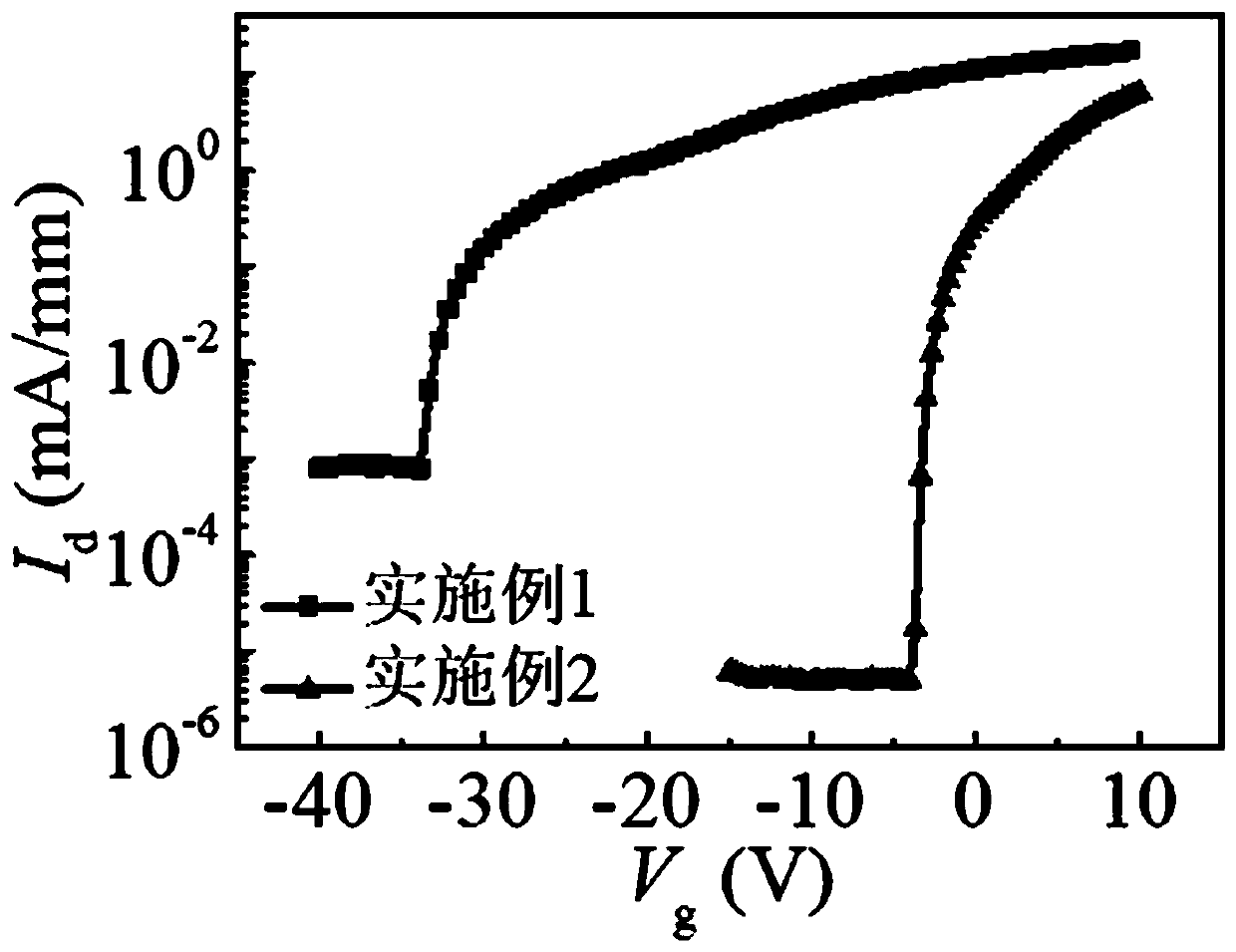

Embodiment 1

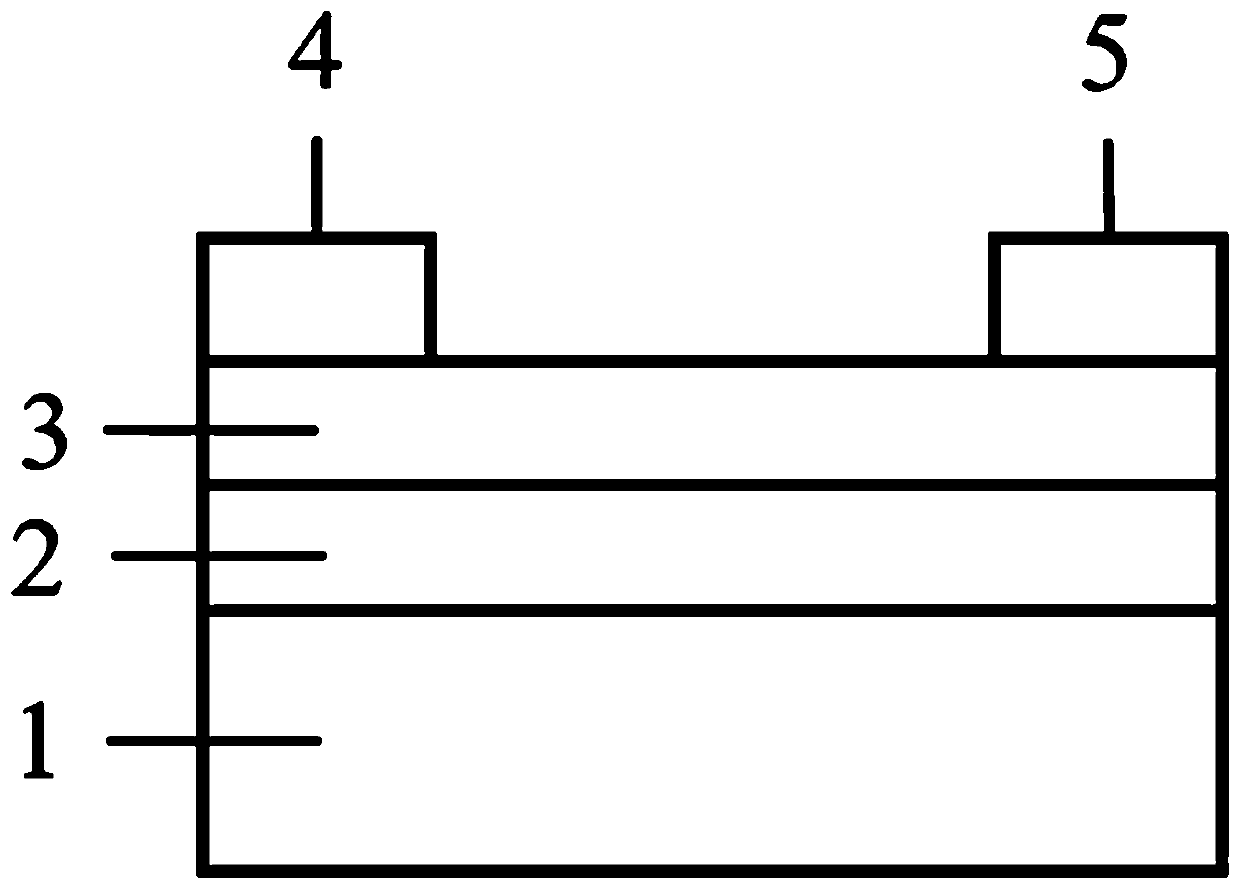

[0030] Embodiment 1, embodiment 1 is not provided with the gallium oxide field effect transistor of tin oxide layer, and it is used as contrast, as figure 1 As shown, a schematic diagram of its structure is given, and the structure is as follows figure 1 As shown, a bottom gate dielectric layer 2 and a gallium oxide channel layer 3 are sequentially arranged on a substrate 1 from bottom to top, and a source electrode 4 and a drain electrode 5 are arranged on the gallium oxide channel layer 3 .

[0031] The substrate is a silicon substrate, and the bottom gate is silicon. The thickness of the bottom gate dielectric layer is 100 nm, and the bottom gate dielectric layer is silicon oxide. The gallium oxide channel layer uses gallium oxide film as the channel layer, the thickness of the gallium oxide film is 185 nm, and it is n-type doped gallium oxide with a doping concentration of 5 × 10 16 cm -3 - 5 x 10 18 cm -3 . The source electrode is Ti / Au laminated metal, the thick...

Embodiment 2

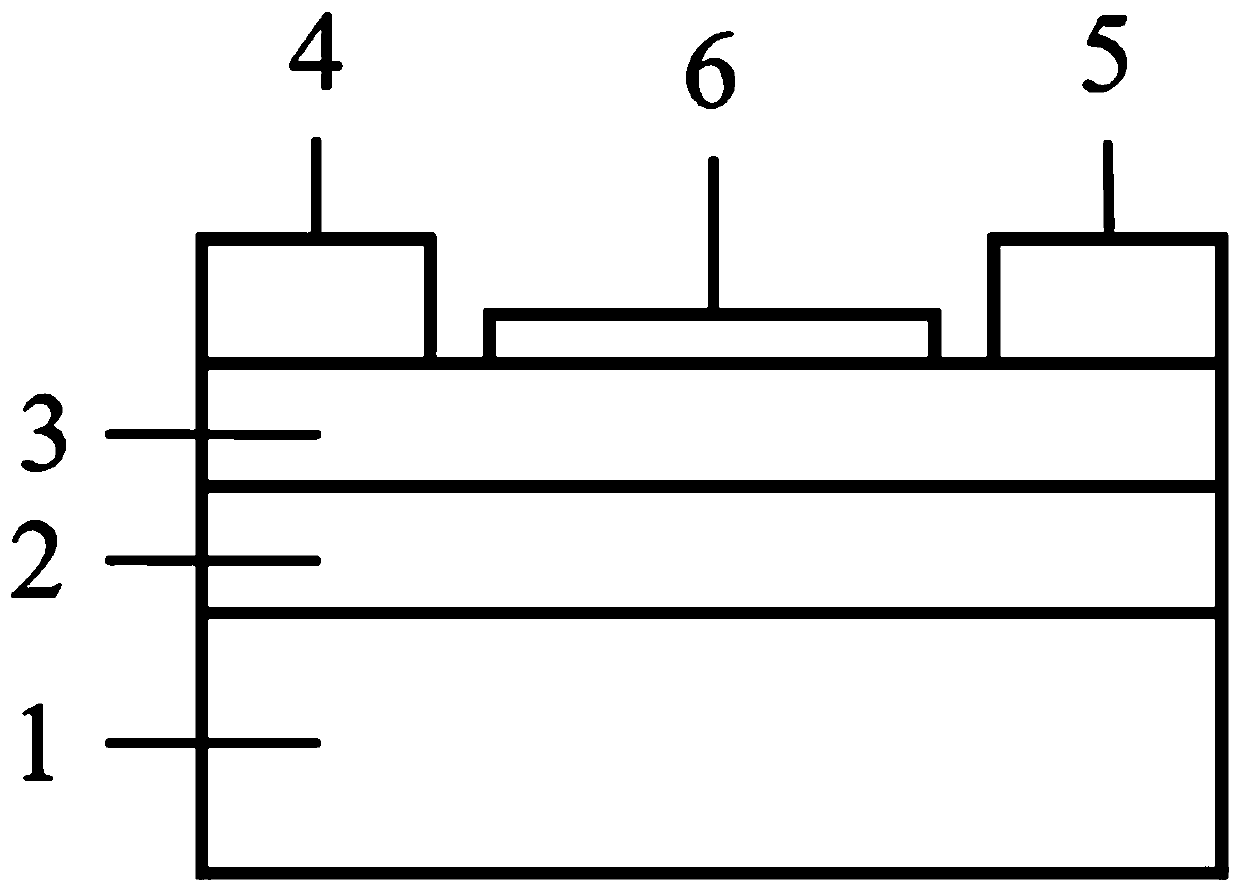

[0039] Example 2, such as figure 2 As shown, the structure schematic diagram of the gallium oxide field effect transistor of the present invention is provided with the tin oxide layer, which is composed of the substrate and the bottom gate electrode 1, the bottom gate dielectric layer 2, the gallium oxide channel layer 3, the source electrode 4 , a drain electrode 5 and a SnO layer 6, the substrate and the bottom gate electrode 1 can be used as the substrate and the gate electrode at the same time, the bottom gate dielectric layer 2 is arranged on the upper surface of the substrate, and the gallium oxide channel layer 3 is arranged on the On the bottom gate dielectric layer 2, the source electrode 4 and the drain electrode 5 are arranged on the upper surface of the gallium oxide channel layer 3, and the tin oxide layer 6 is arranged on the gallium oxide channel layer 3 between the source electrode 4 and the drain electrode 5 , and the SnO layer 6 is not in contact with the so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More