A wafer level chip scale package and a manufacturing method thereof

A technology of grain size and packaging structure, applied in the direction of microstructure technology, microstructure devices, manufacturing microstructure devices, etc., can solve problems such as chip winding, increase in component thermal resistance, and decrease in thermal characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

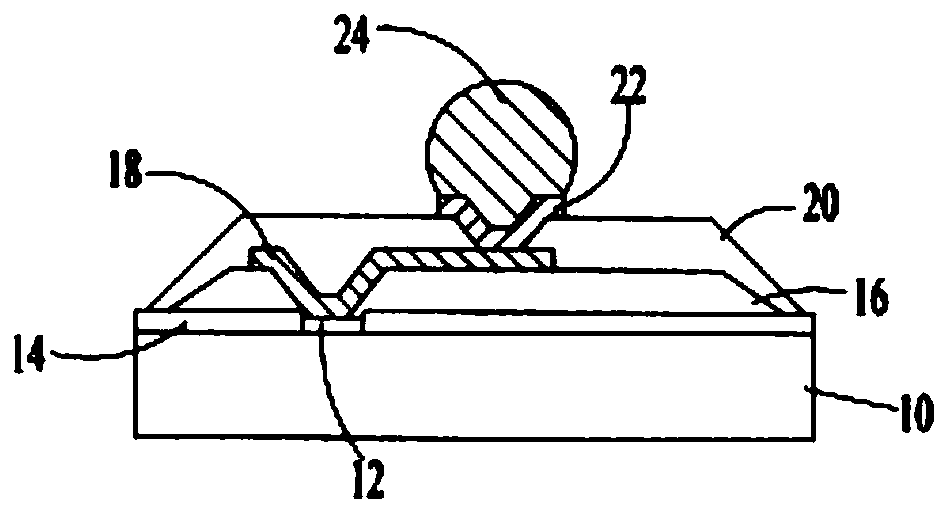

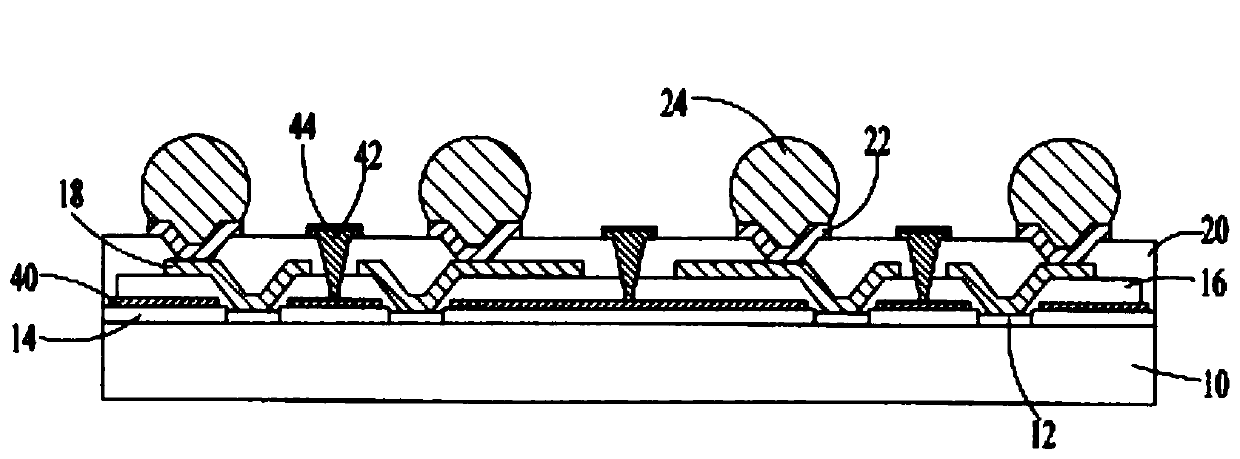

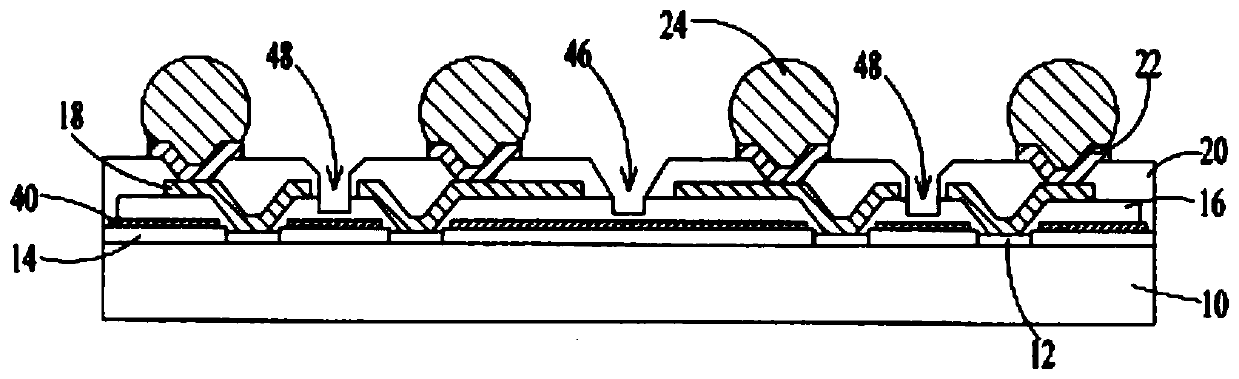

[0039] The present invention provides a method for making a wafer-level die-scale package and its package structure, which uses metal / copper plating isolation barriers and / or trench / notch air gaps to prevent crosstalk interference between adjacent signals , leakage current, and copper migration are reduced. Compared with the existing grain size packaging, the packaging structure and manufacturing process provided by the present invention can also greatly improve the thermal conductivity of the packaging structure.

[0040] The wafer-level grain size packaging technology provided by the present invention further includes the following advantages:

[0041] Compared with the traditional wafer-level die-scale package structure, it has similar appearance variables.

[0042] Compared with the traditional wafer-level grain size packaging structure, it has a similar manufacturing process.

[0043] In the future, without considering the cross-coupling, the process specifications with...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More