Radar echo signal acquisition circuit chip based on SIP technology.

A radar echo and signal acquisition technology, applied in the field of electronics, can solve the problems of space-constrained platforms, low integration, and large system size, achieving the same functions, reduced power consumption, and high seismic resistance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0018] With the development of electronic technology, the complexity and integration of electronic systems are getting higher and higher, and the requirements for the volume, integration and performance of printed circuit boards are also getting higher and higher. In order to improve the performance and integration of electronic systems, it is necessary to It is required to continuously improve the performance of components and develop new packaging technologies. In the existing radar echo signal acquisition circuits, PCB boards are mostly used for design, which are large in size and high in power consumption, and are not easy to be applied to platforms with limited space. Aiming at this current situation, the present invention conducts research and innovation, and proposes a radar echo signal acquisition circuit chip based on SIP technology.

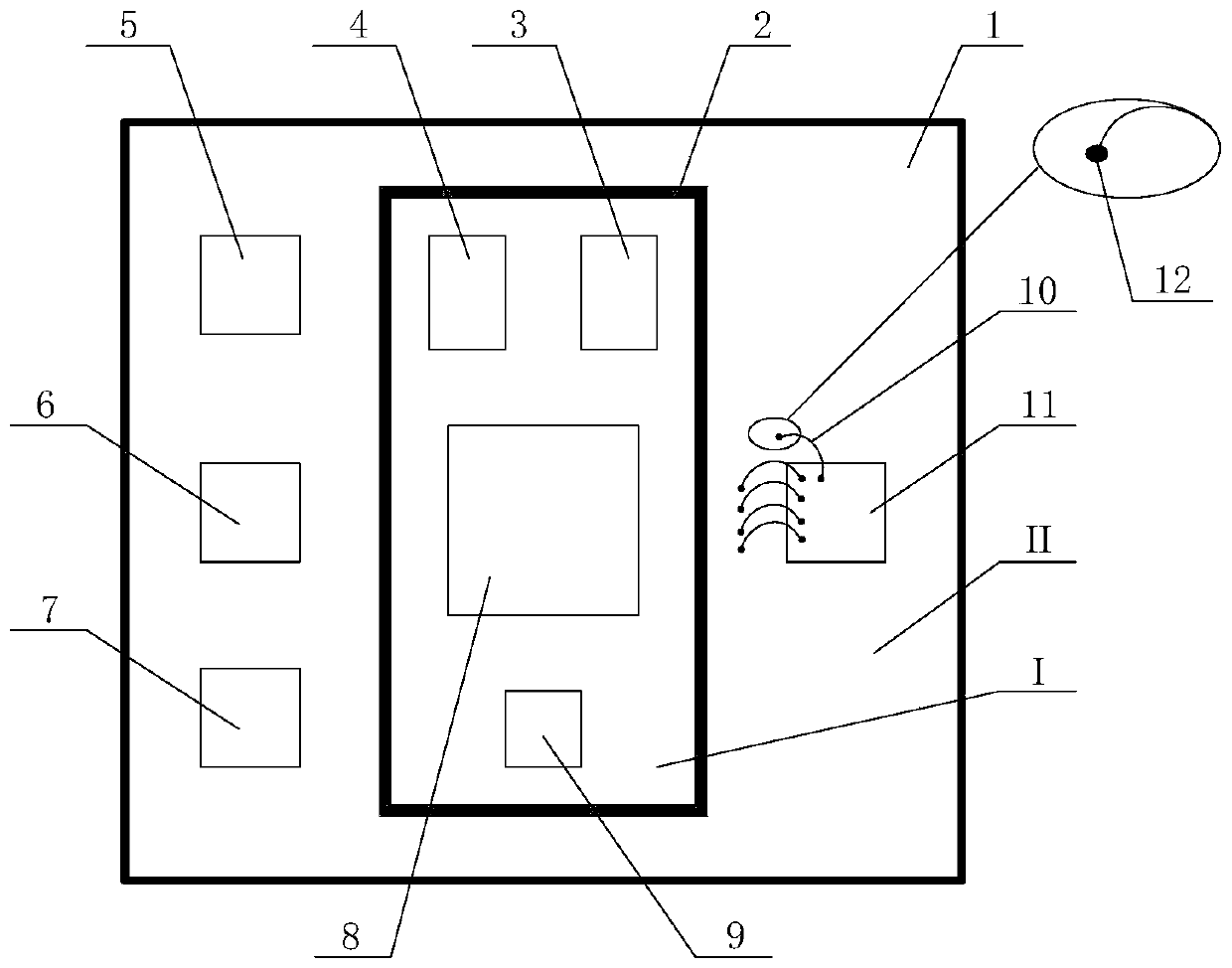

[0019] The radar echo signal acquisition circuit chip based on SIP technology of the present invention adopts system-level packaging, ...

Embodiment 2

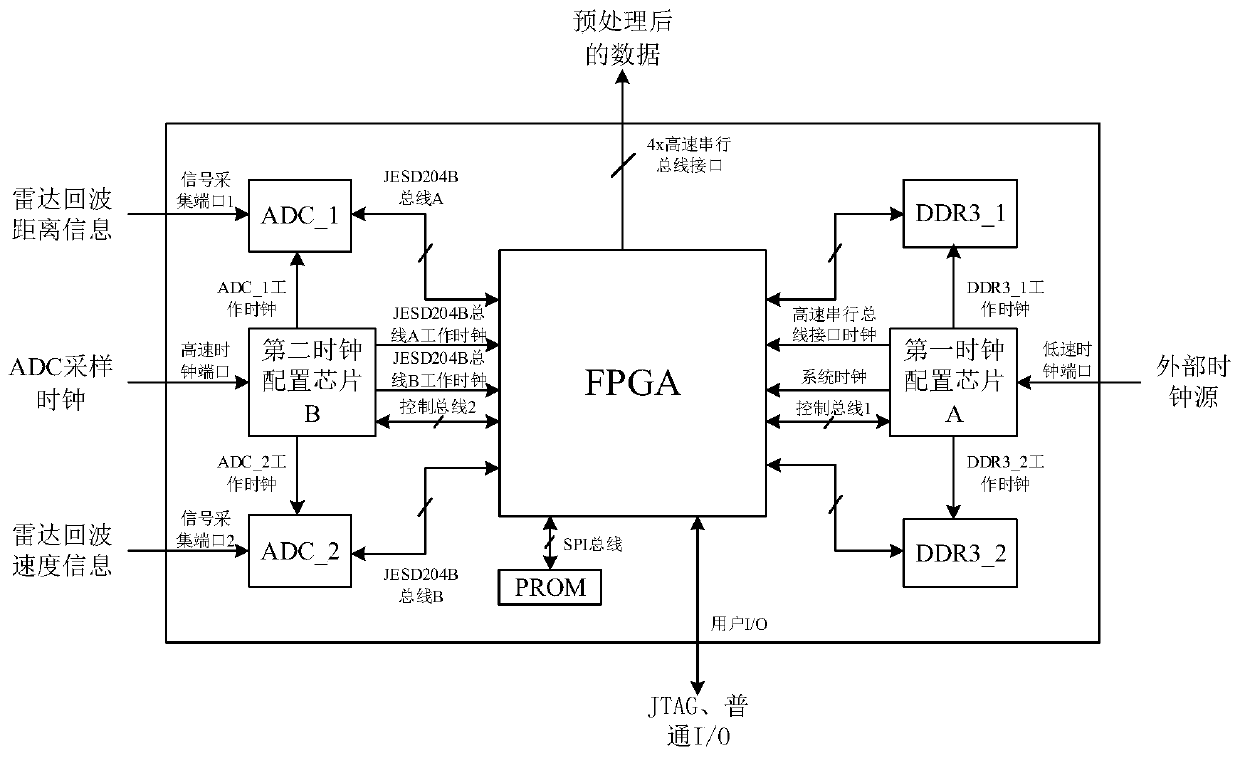

[0026] The overall composition of the radar echo signal acquisition circuit chip based on SIP technology is the same as embodiment 1, see figure 2 , the FPGA in the signal preprocessing module of the present invention is the control core of the whole radar echo signal acquisition circuit chip, it first reads the solidified program in the configuration PROM, and performs ADC, DDR3, clock configuration chip and user I / O After initialization, digital mixing, low-pass filtering, signal extraction, and matching filtering are performed on the data collected by the ADC chip, and then the data after matching filtering is buffered and packaged, and then the packaged data is connected to the 4x high-speed serial bus interface Perform speed matching, and finally transmit the packaged radar echo preprocessed data through the high-speed serial bus interface of FPGA. The preprocessing of the radar echo signal is the first step of the whole radar signal processing. The present invention uti...

Embodiment 3

[0028] The overall composition of the radar echo signal acquisition circuit chip based on SIP technology is the same as embodiment 1-2, see figure 2 , the high-speed ADC acquisition chip ADC_1 of the present invention collects the distance information of the radar echo signal and converts it into a digital signal, and then transmits the digital signal of the radar echo distance information to the FPGA through the JESD204B bus 1 . ADC_2 collects the speed information of the radar echo signal and converts it into a digital signal, and then transmits the digital signal of the radar echo speed information to the FPGA through the JESD204B bus 2. The FPGA performs pulse compression on the digital signals of the radar echo distance information and speed information to obtain the pulse pressure results in the distance direction and azimuth direction, thereby obtaining the position information and speed information of the target. The invention adopts a high-speed ADC acquisition chip,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More