Floating point operation circuit implementation method for real number matrix inversion

A technology of matrix inversion and floating-point operation, applied in complex mathematical operations, calculations, electrical digital data processing, etc. High resource utilization, reasonable computing delay, and the effect of reducing computing delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

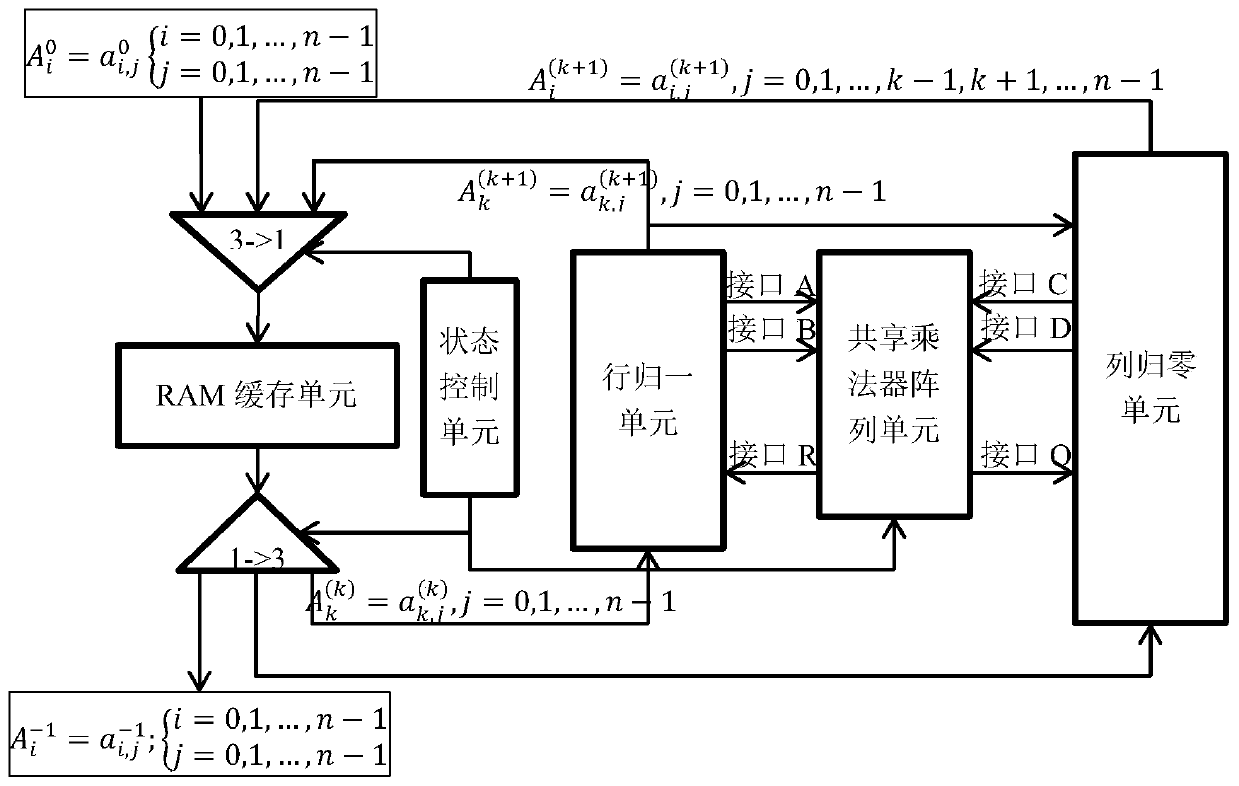

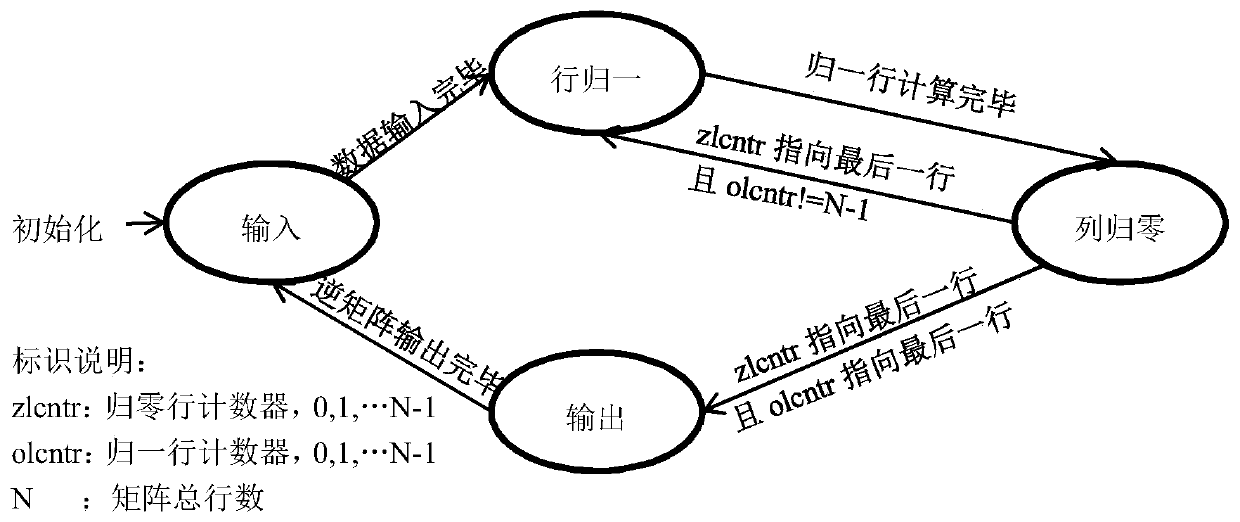

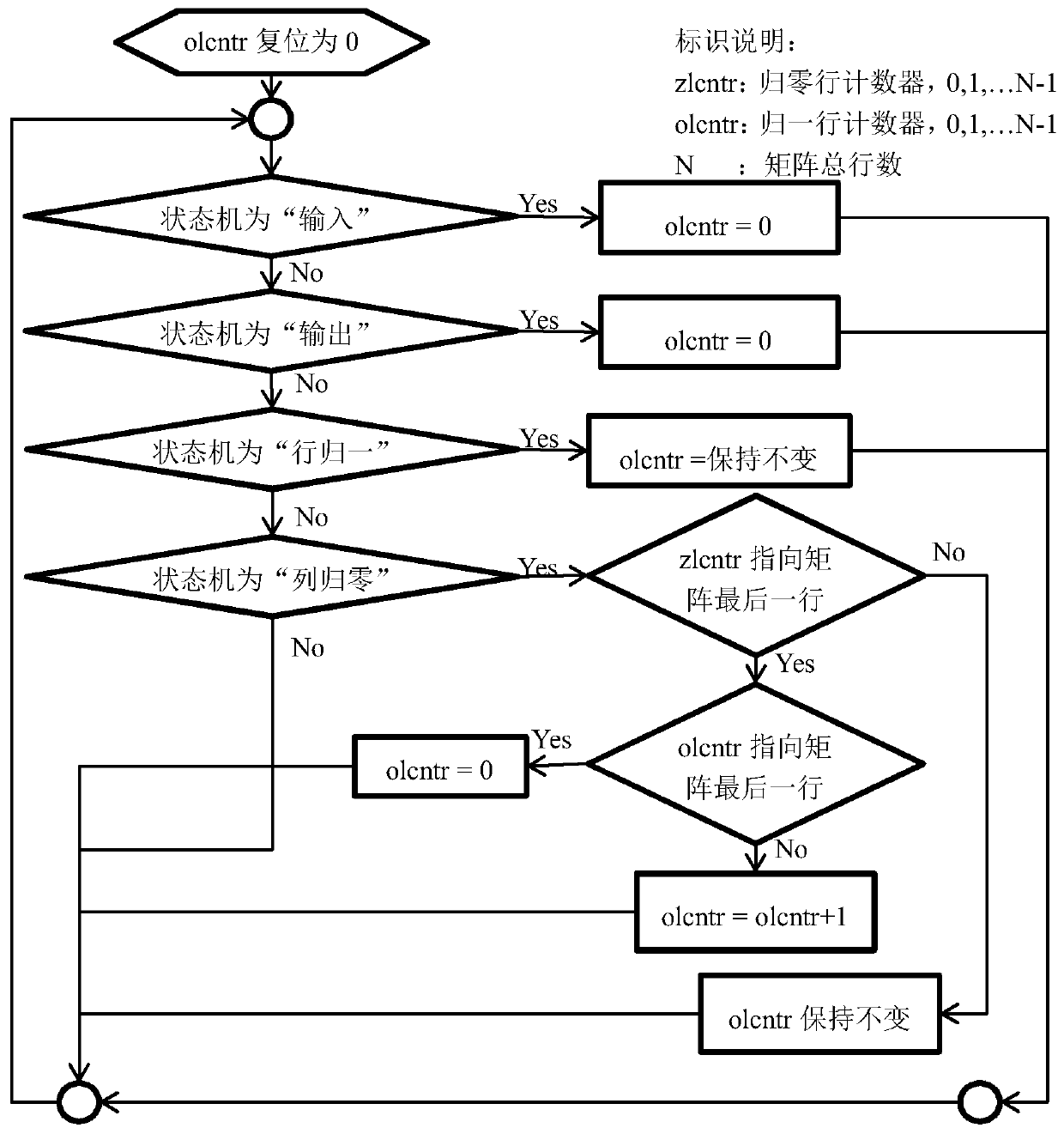

[0041] refer to figure 1. According to the present invention, according to the matrix comprising the inversion operation state control unit, three selector 3MUX1, one select three selector 1MUX3, row normalization unit, column zero unit, RAM cache unit, shared multiplier array unit Inversion circuit, from the input port of the matrix inversion circuit, the N-order square matrix waiting for inversion will be input into the three-choice multiplexer 3MUX1 in row or column order, and the three-choice one multiplexer 3MUX1 is in the "input matrix After the strobe signal between the output results of "row", "row normalization" and "column zero", it is sent to the buffer memory of the RAM cache unit through the state control unit; To read the matrix row data of the kth row, traversing all the row or column data of the matrix once is regarded as an elimination cycle, and the read matrix row data is divided into two paths, and n cycles are executed; one path is sent to the row normali...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com