Method of forming 3D NAND memory

A 3DNAND, memory technology, applied in the direction of electric solid devices, semiconductor devices, electrical components, etc., can solve the problem of easy inclination of gate spacers, short circuit between gate spacers and channel through holes, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example 3D

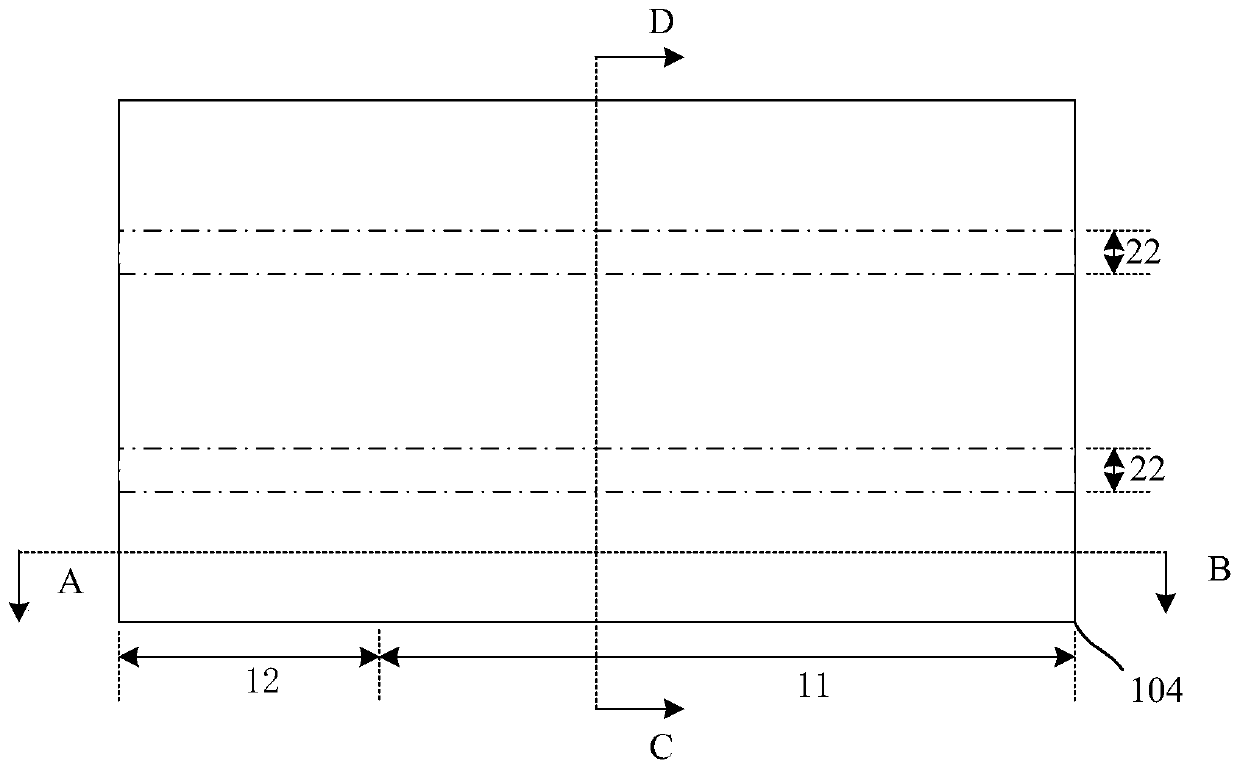

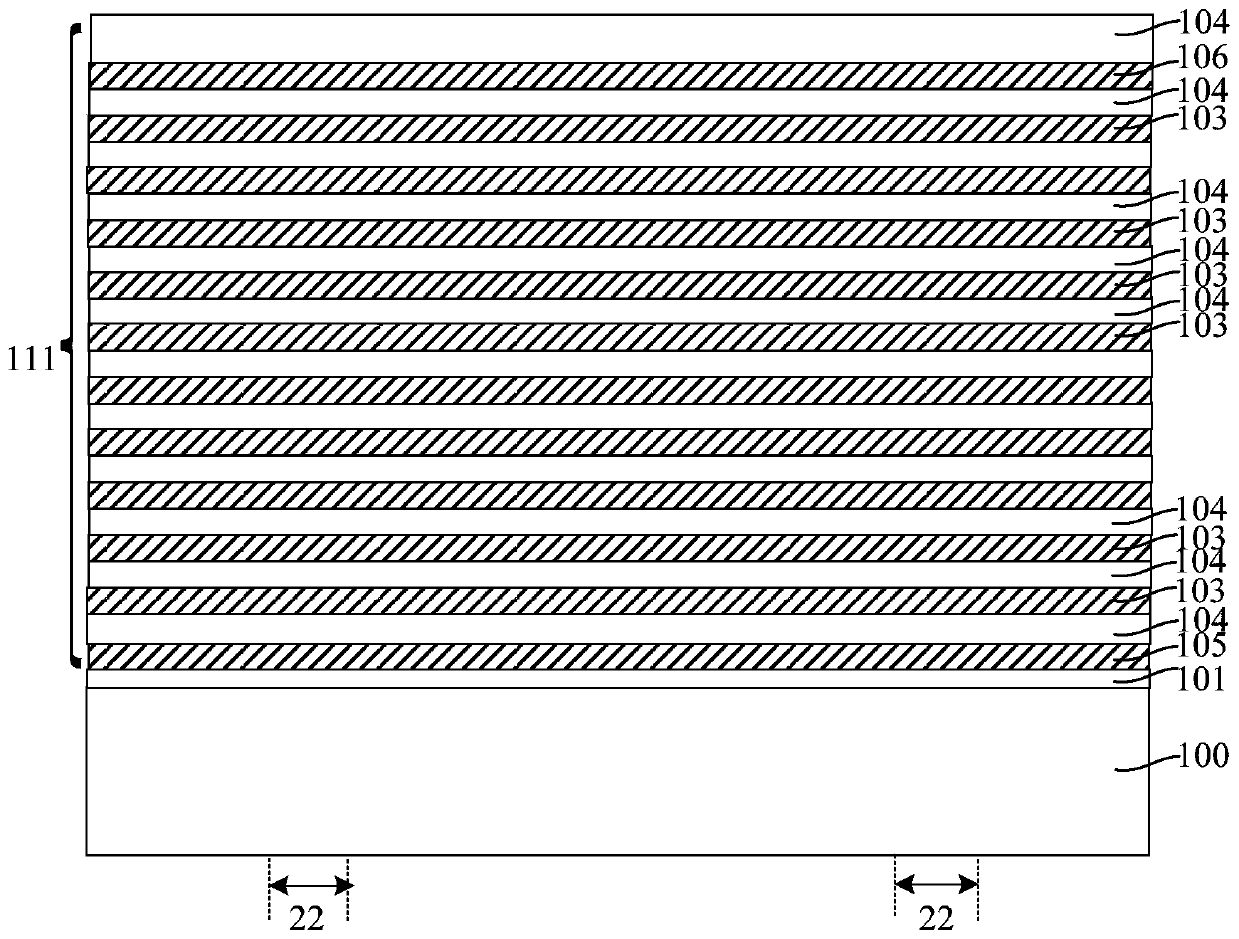

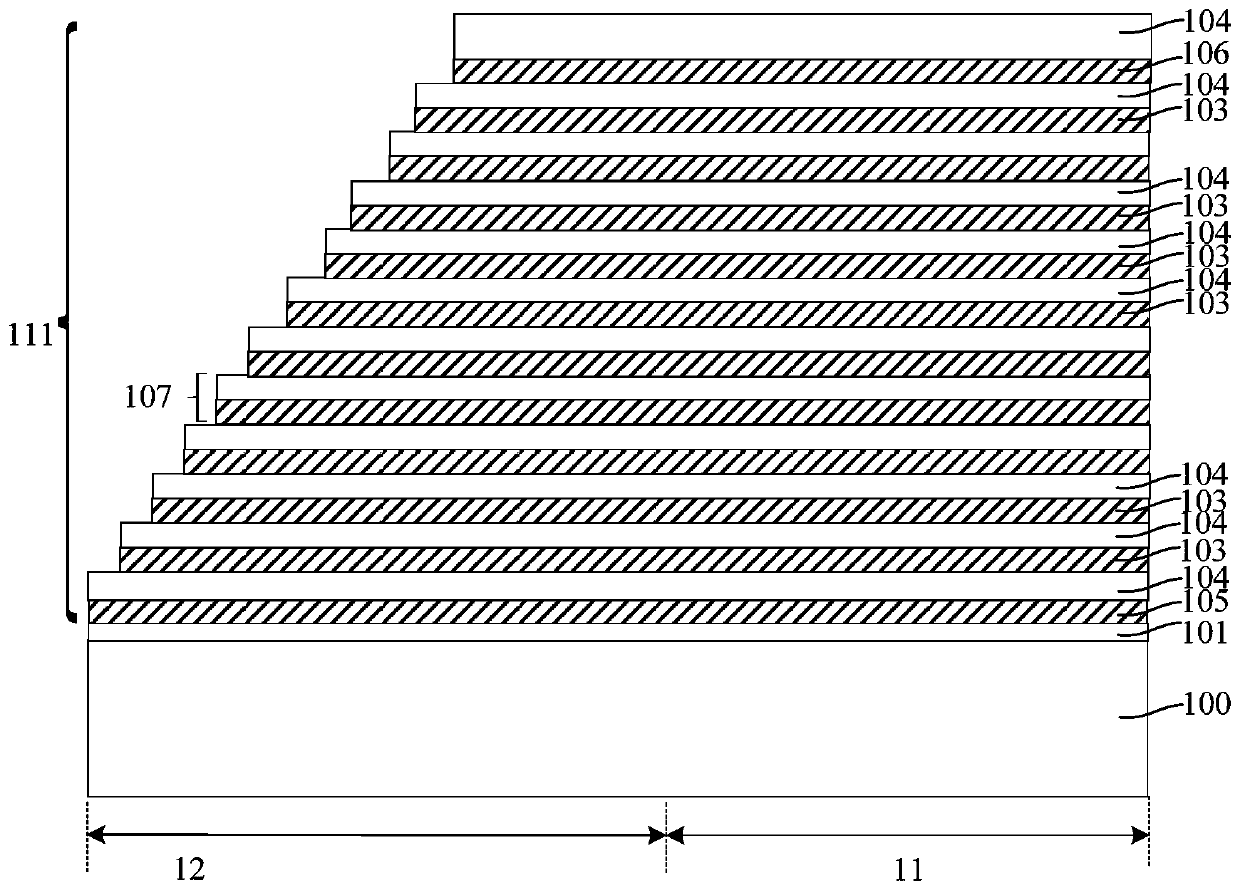

[0039] Figure 1-Figure 14 It is a structural schematic diagram of the 3D NAND formation process according to the first embodiment of the present invention.

[0040] refer to figure 1 and figure 2 , figure 2 for figure 1 A schematic diagram of a cross-sectional structure along a cutting line CD provides a semiconductor substrate 100 on which a stacked structure 111 in which sacrificial layers 103 and isolation layers 104 are alternately stacked is formed.

[0041] The material of the semiconductor substrate 100 can be single crystal silicon (Si), single crystal germanium (Ge), or silicon germanium (GeSi), silicon carbide (SiC); it can also be silicon on insulator (SOI), germanium on insulator (GOI); or other materials, such as III-V group compounds such as gallium arsenide. In this embodiment, the material of the semiconductor substrate 100 is single crystal silicon (Si).

[0042] The stacked structure 111 includes several alternately stacked sacrificial layers 103 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More