A Fault-Tolerant Routing Method for Area Fault Awareness in Wireless Network-on-Chip

A network-on-a-chip, trouble-free technology, applied in wireless communication, data exchange network, network traffic/resource management, etc., can solve the problem of unbalanced network load and not taking into account the generation of hot spots.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

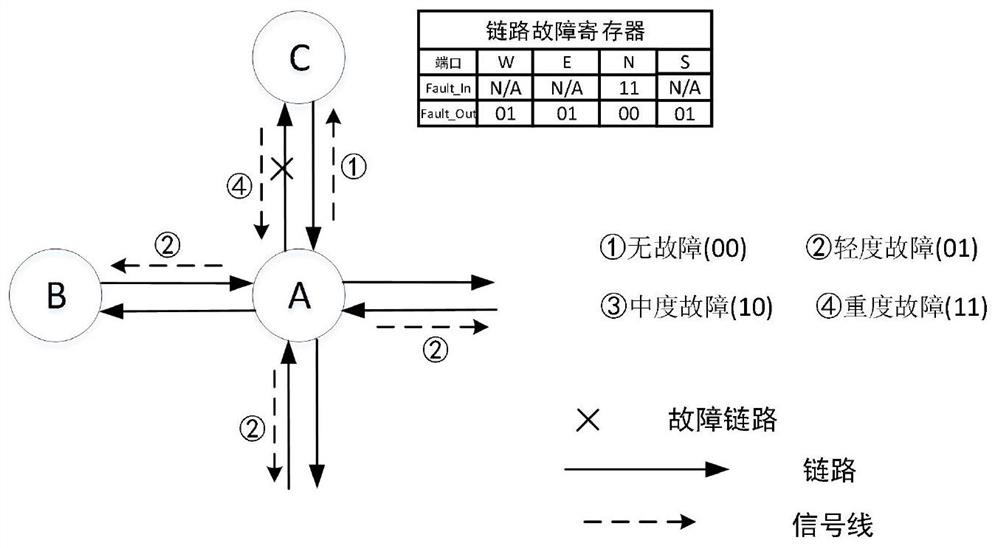

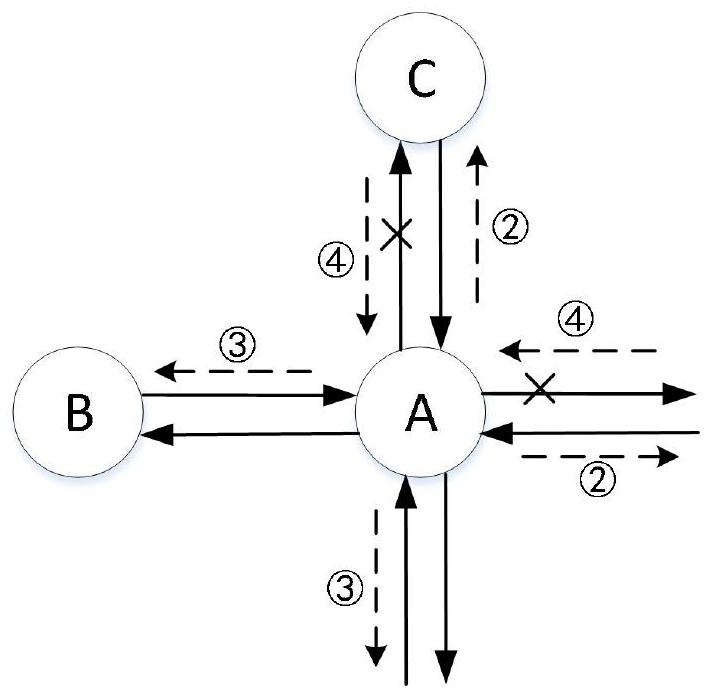

[0050] In this embodiment, a fault-tolerant routing method for regional fault awareness in wireless on-chip networks is: adjacent wired nodes adopt information exchange based on fault areas, which can make nodes perceive the fault state around them, and fill the one-hop information exchange well. Insufficient; the information of the wireless node is exchanged in a two-hop sensing way, which avoids the congestion of the surrounding routers when the wireless node fails or is congested; the proposed method does not use more wiring and area overhead, and through the clever combination of routing algorithms to improve performance.

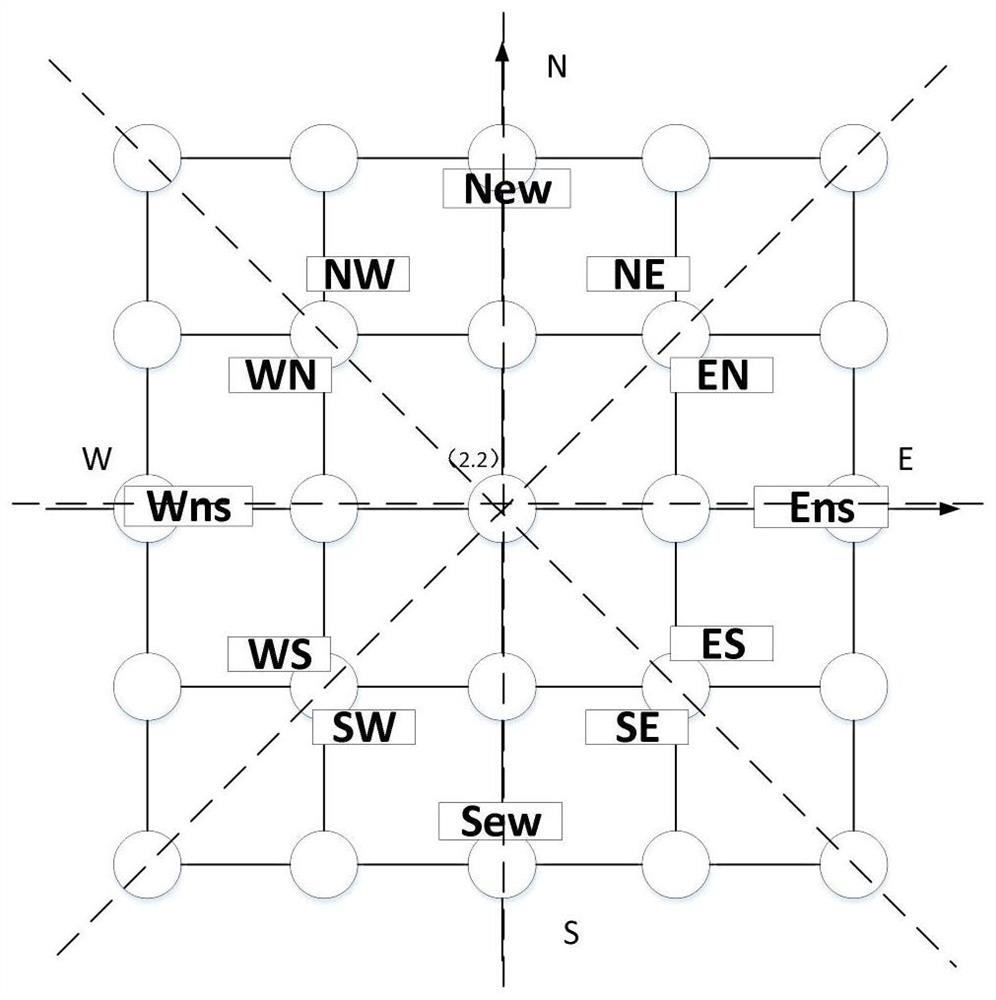

[0051] In order to simplify the position selection of the destination node relative to the current node, firstly, the area of the destination node relative to the current node is divided into four directions (New, Ens, Sew, Wns). In order to optimize the selection of output ports while also providing a high degree of adaptability to the routing algori...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More