9t TFET and MOSFET Hybrid SRAM Cell Circuit with High Write Margin

A unit circuit, write margin technology, applied in the direction of instruments, static memory, digital memory information, etc., can solve the problems of weak unit write capability, increased chip cost, increased unit area, etc., and achieve the effect of good write performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, rather than all the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative work fall within the protection scope of the present invention.

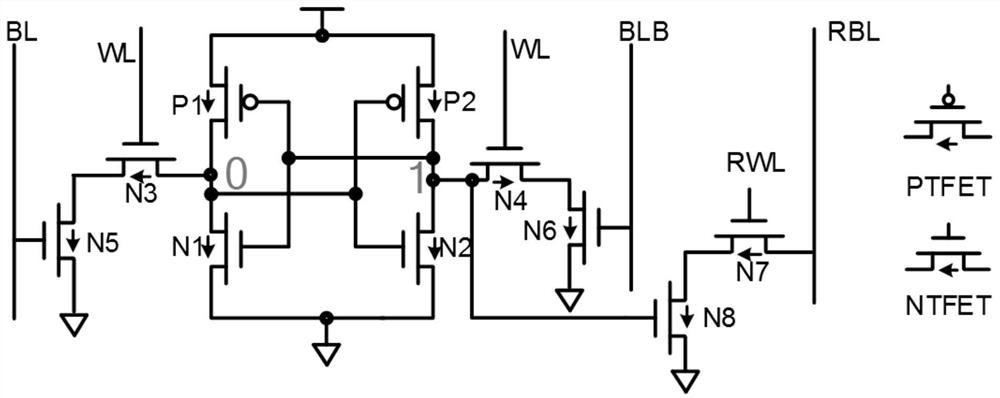

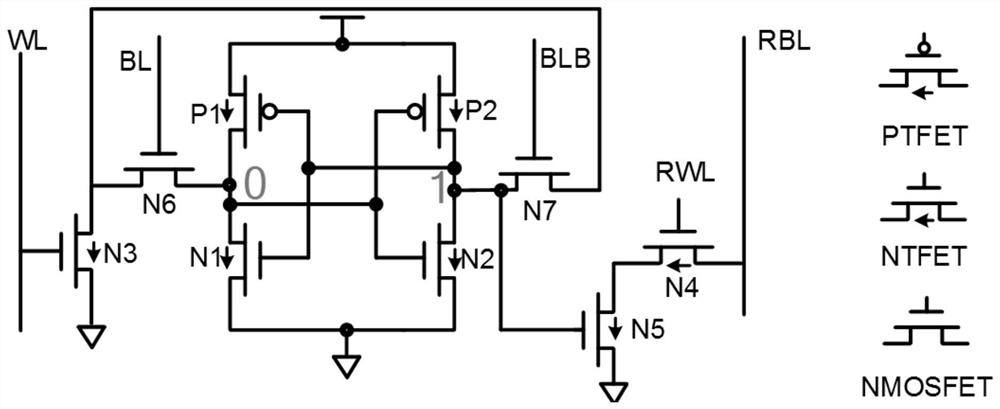

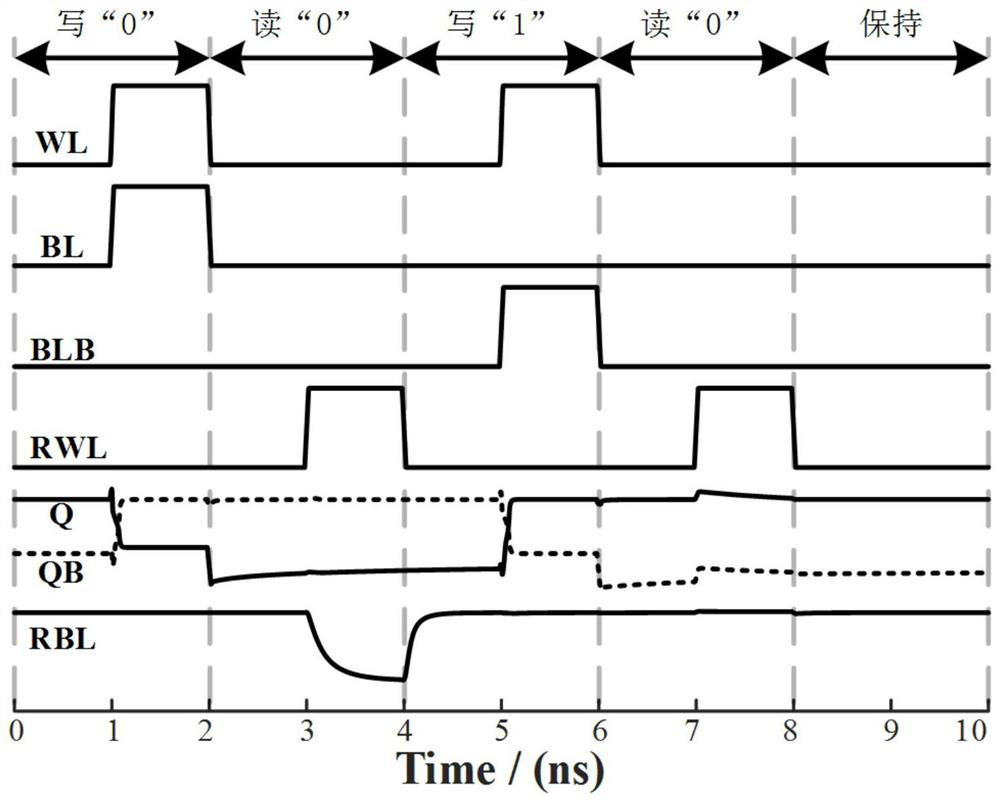

[0022] The basic device used in the traditional SRAM memory cell circuit is MOSFET, and the basic device used in the 9T TFET and MOSFET device hybrid SRAM cell circuit proposed by the present invention is a tunneling field effect transistor (TFET). Due to the shortcomings of the P-I-N forward bias current and the weak conduction capability of the stacked TFET, a method of combining the TFET and the MOSFET device for the SRAM cell transfer transistor in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com