All-digital sub-sampling phase-locked loop and frequency range locking method thereof

A sub-sampling, phase-locked loop technology, applied in the field of all-digital sub-sampling phase-locked loop and its frequency range locking, can solve the problems of small frequency locking range and large power consumption of auxiliary circuits, and achieve extended frequency locking range and hardware overhead. The effect of small, efficient loop control

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] The present invention will be further described below through specific embodiments in conjunction with the accompanying drawings. These embodiments are only used to illustrate the present invention, and are not intended to limit the protection scope of the present invention.

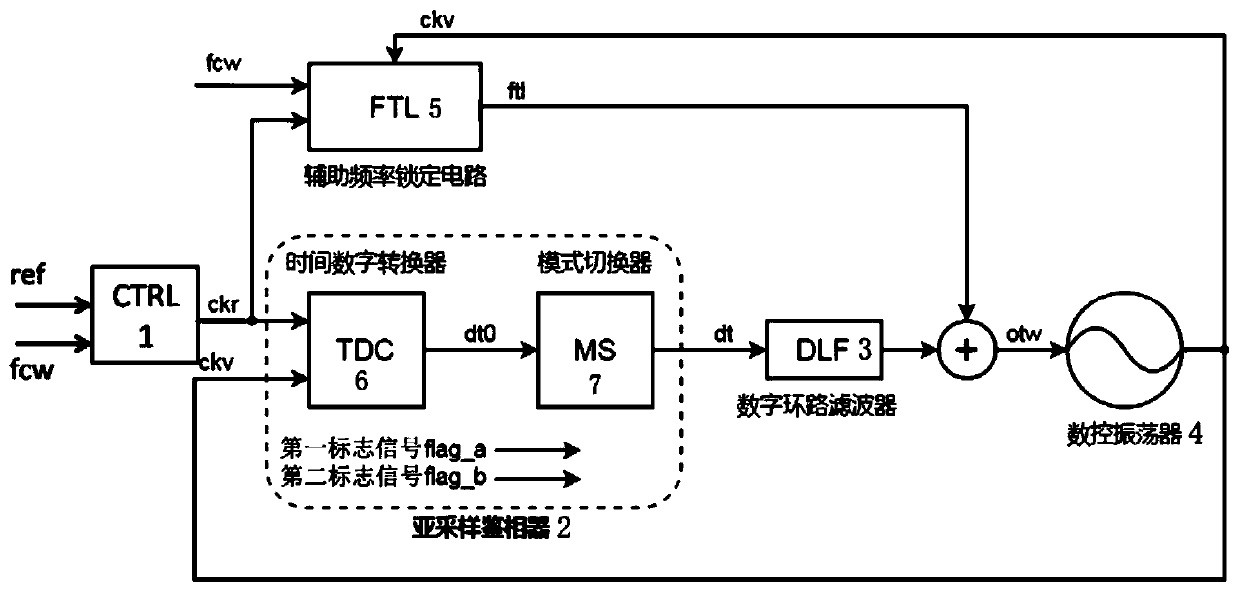

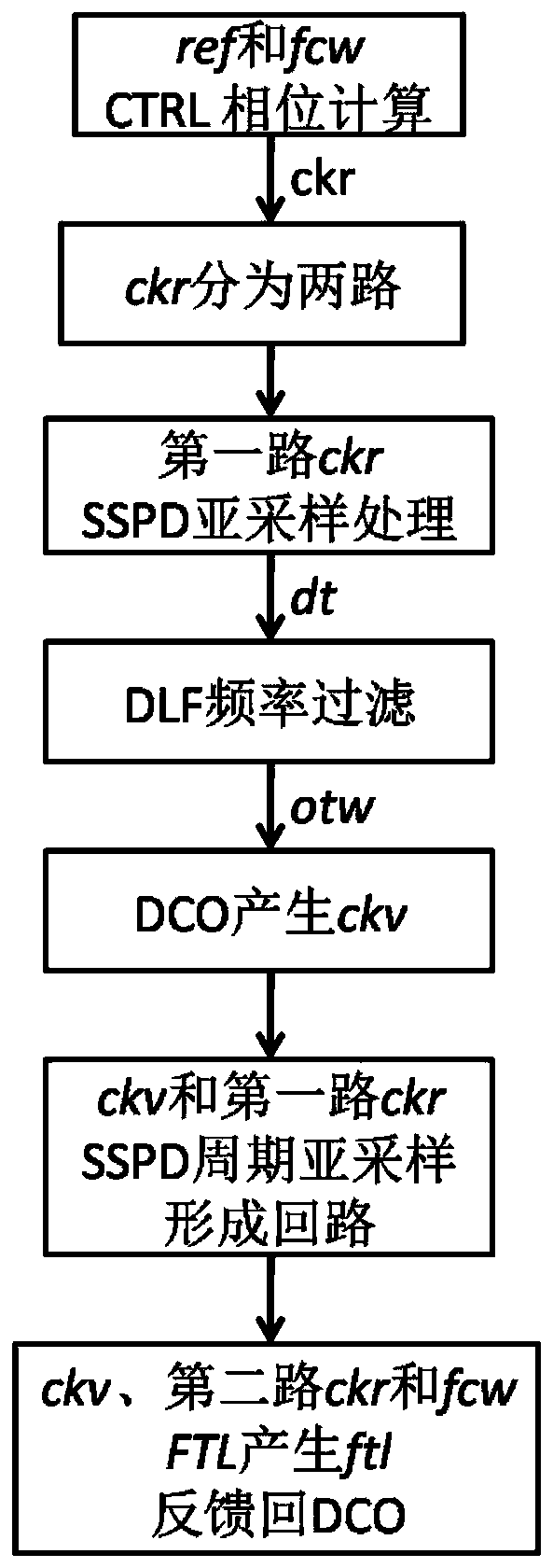

[0066] The present invention is an all-digital sub-sampling phase-locked loop, such as figure 1 As shown, including clock generation and control circuit 1 (CTRL), sub-sampling phase detector 2 (SSPD), digital loop filter 3 (DLF), numerically controlled oscillator 4 (DCO) and auxiliary frequency locking circuit 5 (FTL) .

[0067] The clock generation and control circuit 1 performs phase calculation according to the reference frequency ref set by the PLL and the control frequency signal fcw, and outputs the low frequency control signal ckr.

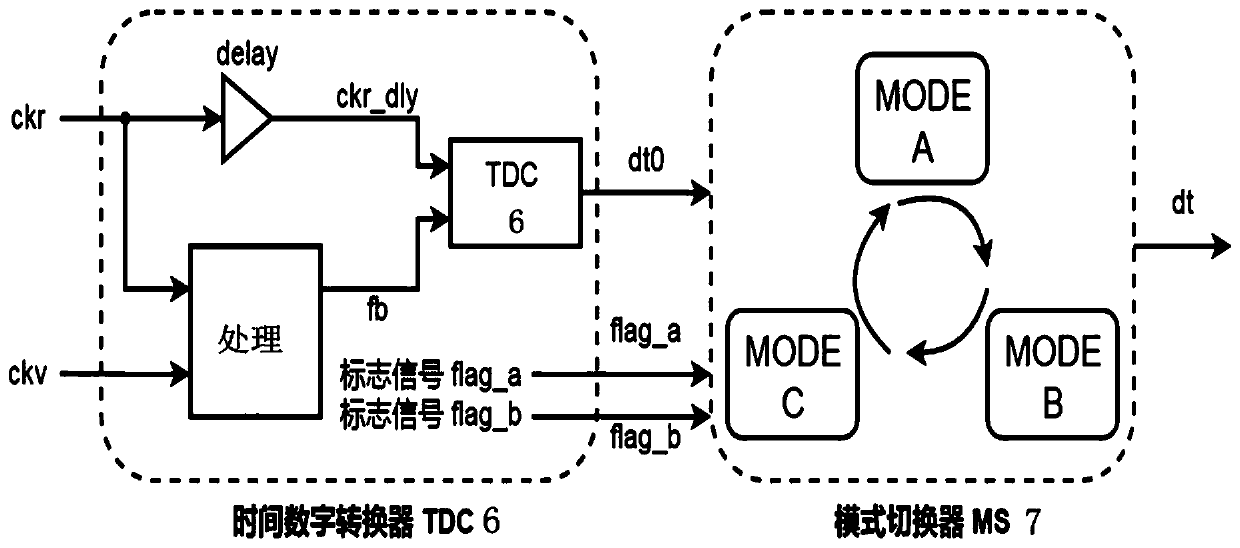

[0068] The first input end of the sub-sampling phase detector 2 is connected to the first output end of the clock generation and control circuit 1 for sub-sam...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More