Array substrate manufacturing method and array substrate

A manufacturing method and array substrate technology, applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve the problems of complex process and high production cost, and achieve the effects of saving photolithography process, protecting balance ability, and reducing process difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

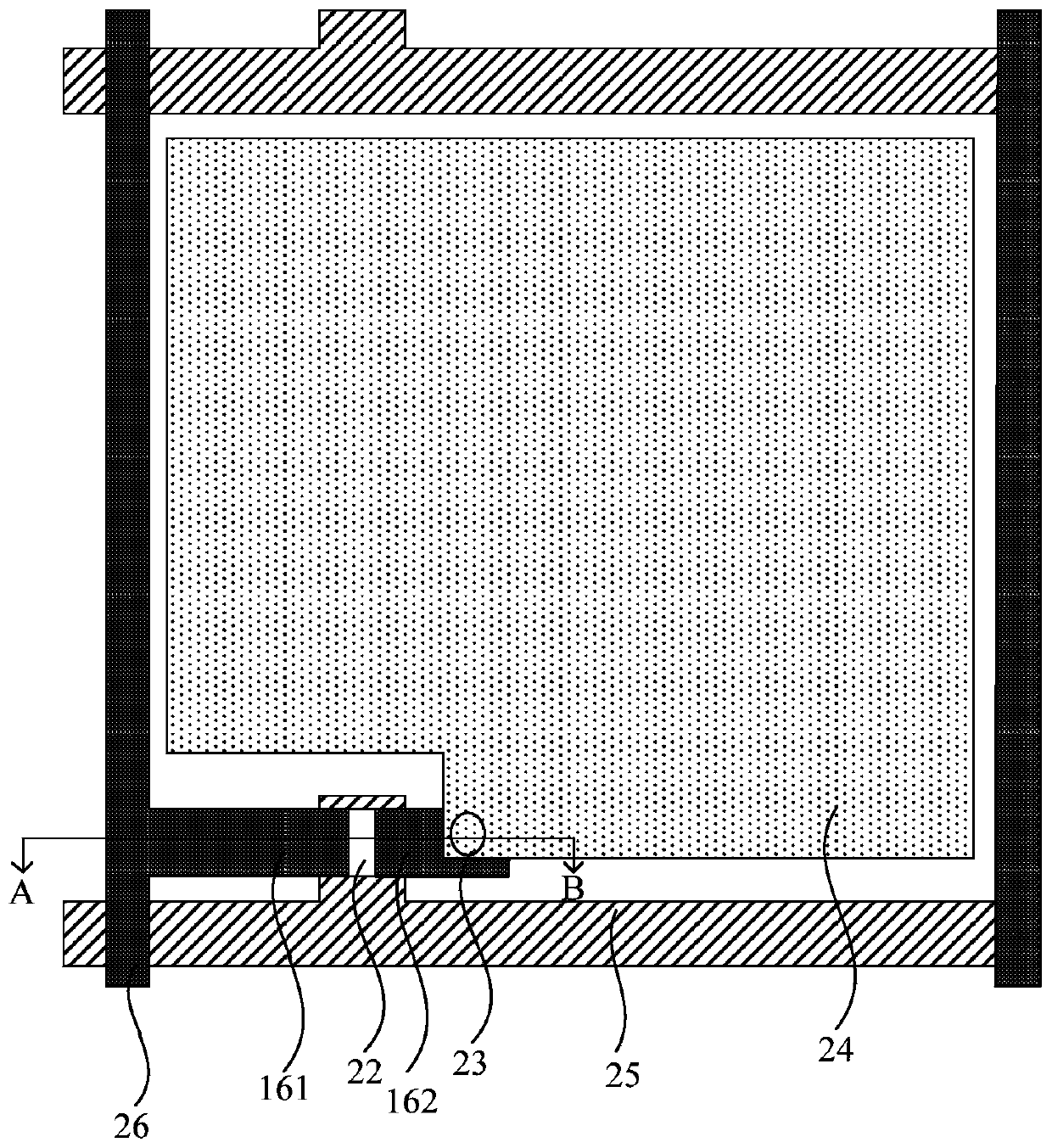

[0068] figure 1 For the plan view of the array substrate provided by the embodiment of the present invention, refer to figure 1 As shown, the array substrate provided by the embodiment of the present invention includes a source electrode 161, a drain electrode 162, a passivation layer 22, a conductive via hole 23, a pixel electrode 24, a scanning line 25 and a data line 26, wherein the pixel electrode 24 is connected through a conductive via The hole 23 communicates with the drain 162, the scan line 25 communicates with the gate 12 and both are formed in the same photolithography process, the data line 26 communicates with the source 161 and both are formed in the same photolithography process, it should be noted that , figure 1 is the plan view of the array substrate, due to the viewing angle, some structures of the array substrate are not in the figure 1 , so it is not presented here.

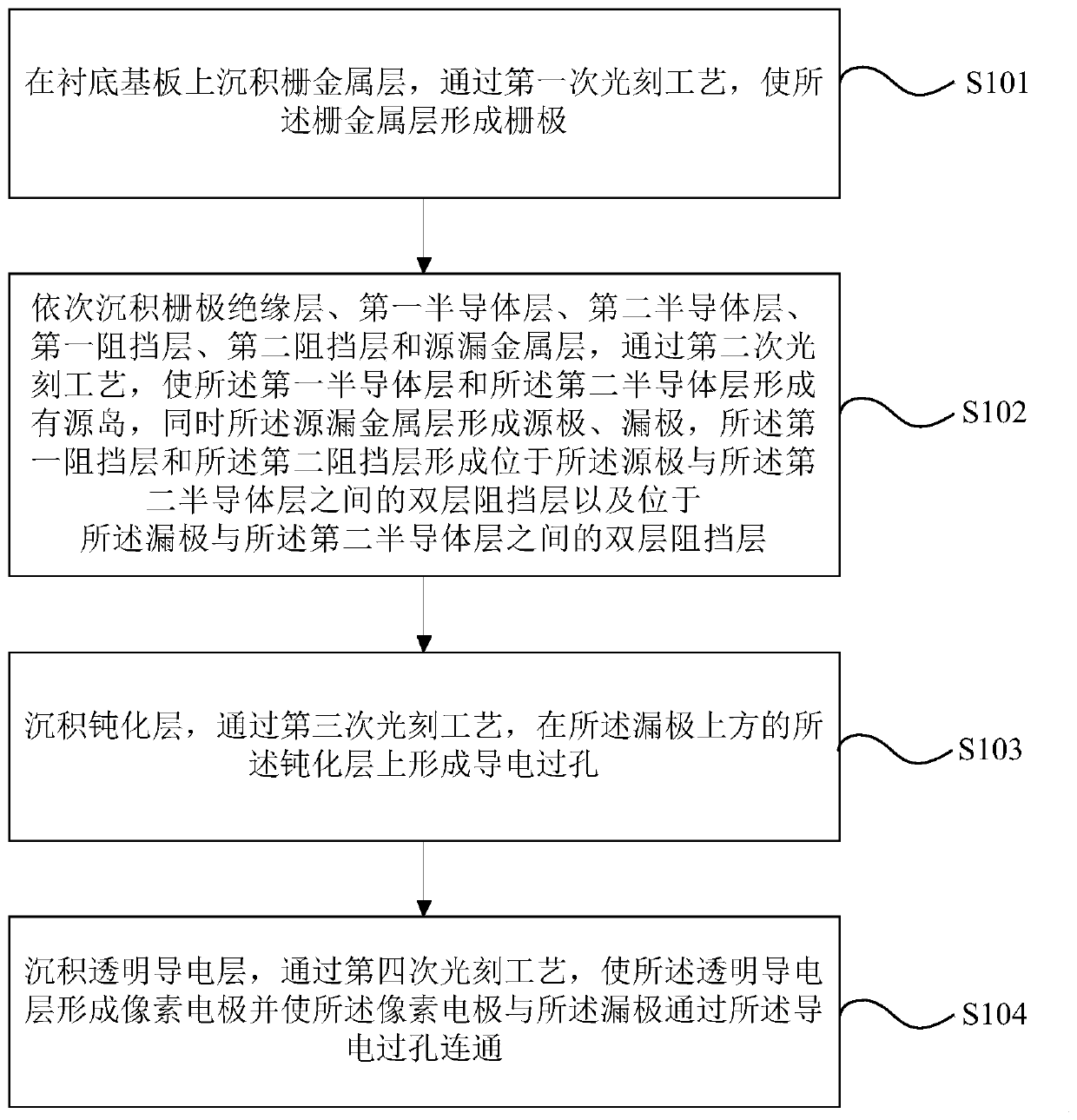

[0069] figure 2 The flow chart of the manufacturing method of the array substrate pr...

Embodiment 2

[0089] An embodiment of the present invention provides an array substrate, which is fabricated by the method described in Embodiment 1, such as figure 1 and Figure 9 As shown, the array substrate includes: a base substrate 11 and a gate 12, a gate insulating layer 13, a first semiconductor layer 141, a second semiconductor layer 142, a first barrier layer 151, The second barrier layer 152, the source-drain metal layer, the passivation layer 22 and the pixel electrode 24, the source-drain metal layer includes a source electrode 161 and a drain electrode 162, and a channel region 21 is provided between the source electrode 161 and the drain electrode 162; wherein, The first semiconductor layer 141 is a metal oxide semiconductor with low oxygen content, and the second semiconductor layer 142 is a metal oxide semiconductor with high oxygen content; the passivation layer 22 has a conductive via hole 23, and the pixel electrode 24 passes through the conductive via hole 23 and The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More