High-precision hybrid integrated circuit test frame isolation protection structure

A hybrid integrated circuit, isolation protection technology, applied in the direction of power supply test, short circuit test, electrical measuring instrument components, etc., can solve the problems of system signal instability, failure to work normally, inconvenient installation, etc., to ensure the normal operation of the whole, Prevent live plugging and unplugging from damaging the chip and ensure stable results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The isolation and protection structure of a high-precision hybrid integrated circuit test stand provided in this embodiment includes a circuit substrate, and the circuit substrate is integrated with:

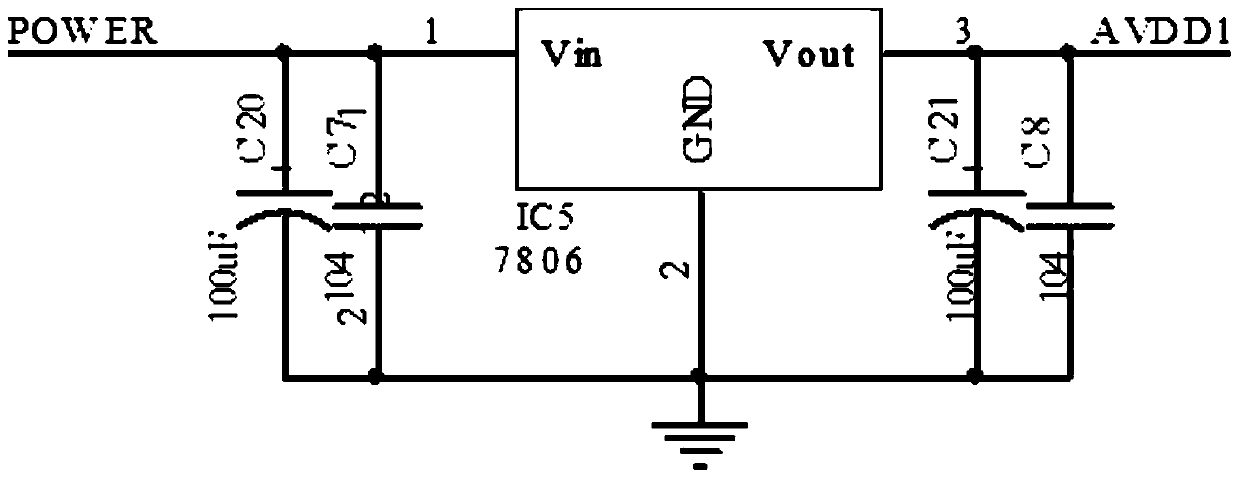

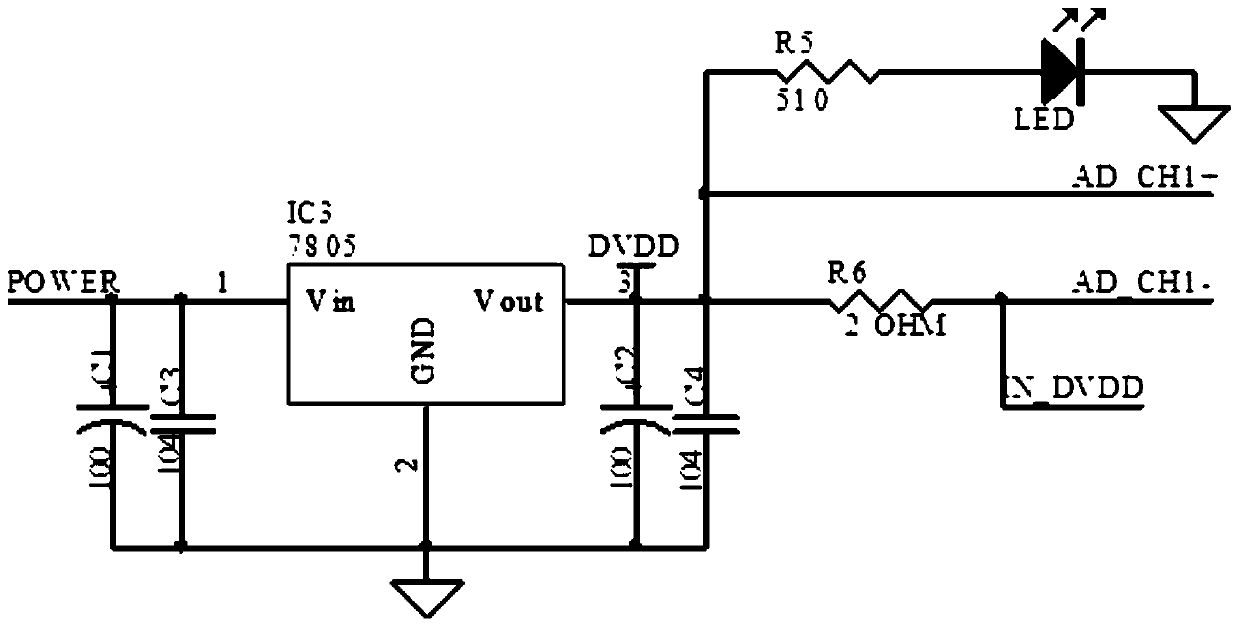

[0030] The chip socket to be tested, the power module and the single-chip microcomputer are used to supply power for the entire test frame and control and analyze the test module. The chip socket to be tested is provided with a relay, and the single-chip microcomputer controls the on-off of the relay, and the power supply module is provided with a voltage stabilizer;

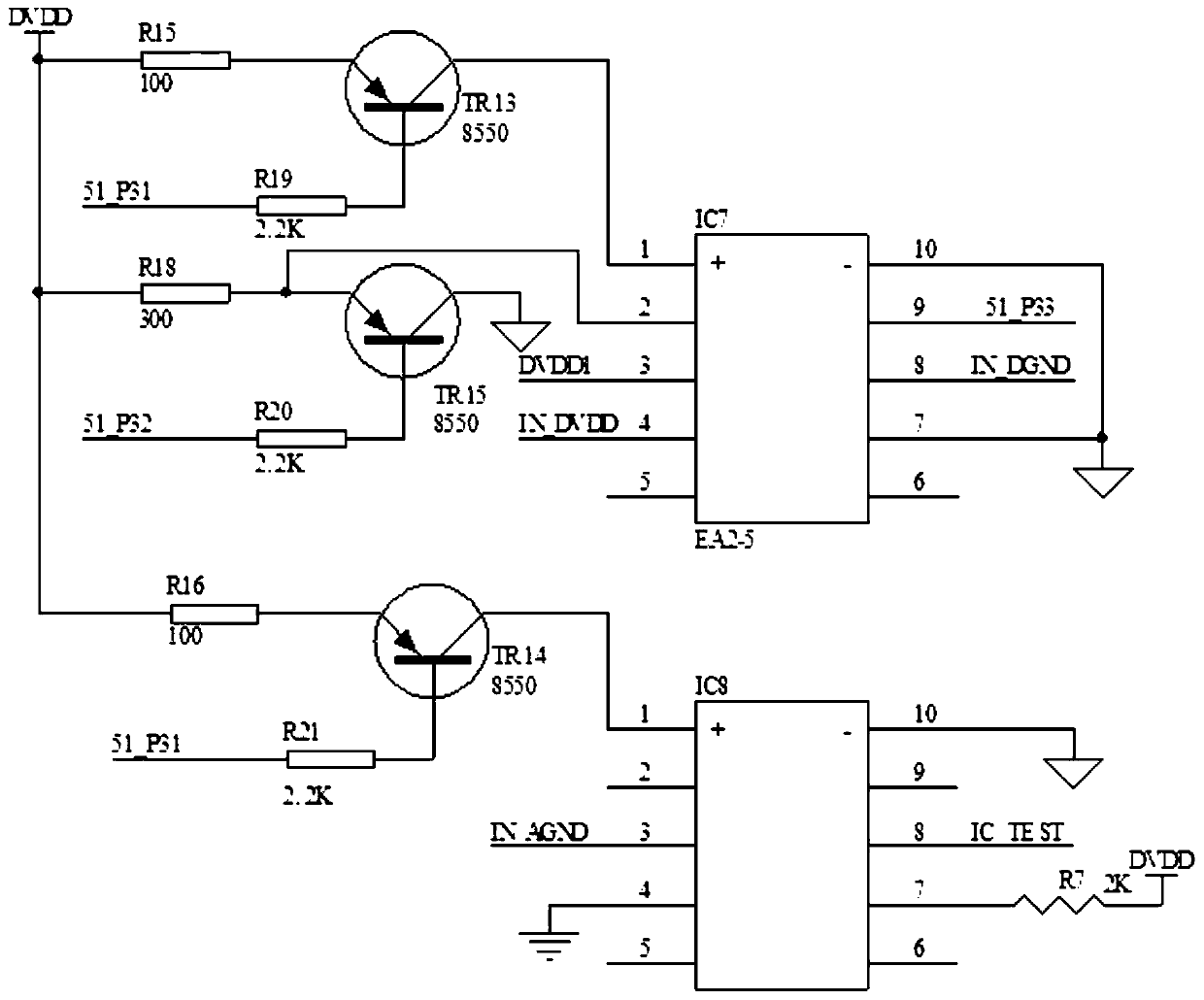

[0031] The ADC / DAC detection unit is isolated and powered by the power module. The signal line between the single-chip microcomputer and the ADC / DAC detection unit is isolated by a high-speed optocoupler HCPL2231, and a 2Ω / 2W test resistor is connected in series to the power input terminal of the single-chip function;

[0032] Handle module, the Handle module is isolated from the power module in the test fra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More