SEC verification method and device for FPGA configuration memory

A verification method and a technology of a verification device, which are applied in the field of SEC verification, can solve problems such as error detection rate and modification rate, uncorrectable errors, complicated operation, etc., to simplify circuits and control processes, and improve correctness and stability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0045] See figure 1 , figure 1 It is a flow chart of an SEC verification method for FPGA configuration memory provided by an embodiment of the present invention. After the configuration of the FPGA chip is completed, the SEC soft error checking function is started through the control signal. The SEC verification method of the present embodiment includes:

[0046] S1: Obtain and save the reference ECC check code;

[0047] S2: Perform ECC verification on the data in the FPGA configuration memory frame by frame according to the reference ECC verification code and modify the error data;

[0048] ECC is a memory error correction method. When there is only 1-bit error in a frame of data, it can locate and correct the error; when there are 2-bit errors in a frame of data, it can detect the error. ECC is realized by adding check bits to the original data bits. If the data bits are 8 bits, 5 bits need to be added for ECC error checking and correction. Every time the data bits doubl...

Embodiment 2

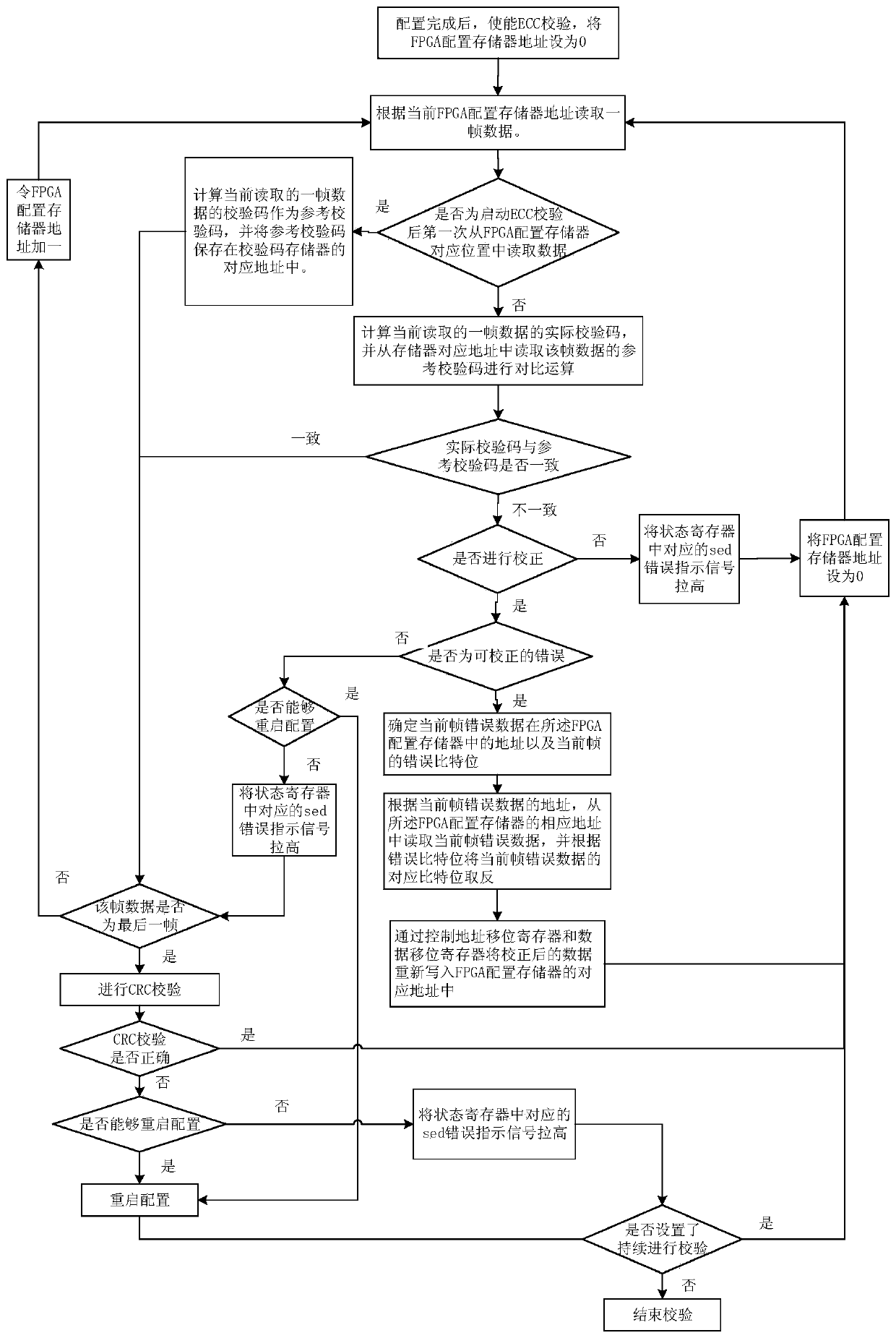

[0069] See figure 2 , figure 2 It is another flow chart of the SEC verification method for FPGA configuration memory provided by the embodiment of the present invention.

[0070] The SEC verification method of the present embodiment includes:

[0071] After the configuration of the FPGA configuration memory is completed, start the SEC verification device, and the SEC verification module will start from address 0 of the FPGA configuration memory and read the data in all addresses in sequence to determine whether it is the first time to read from the FPGA configuration memory. data, if so, then calculate the ECC check code of each frame data sequentially as the most reference ECC check code, and store in the corresponding address of the ECC check code memory, preferably, the ECC check code memory is a sram_sp_hde memory, if If it is not the first time to read data from the FPGA configuration memory, it means that the reference ECC check code has been saved in the previous st...

Embodiment 3

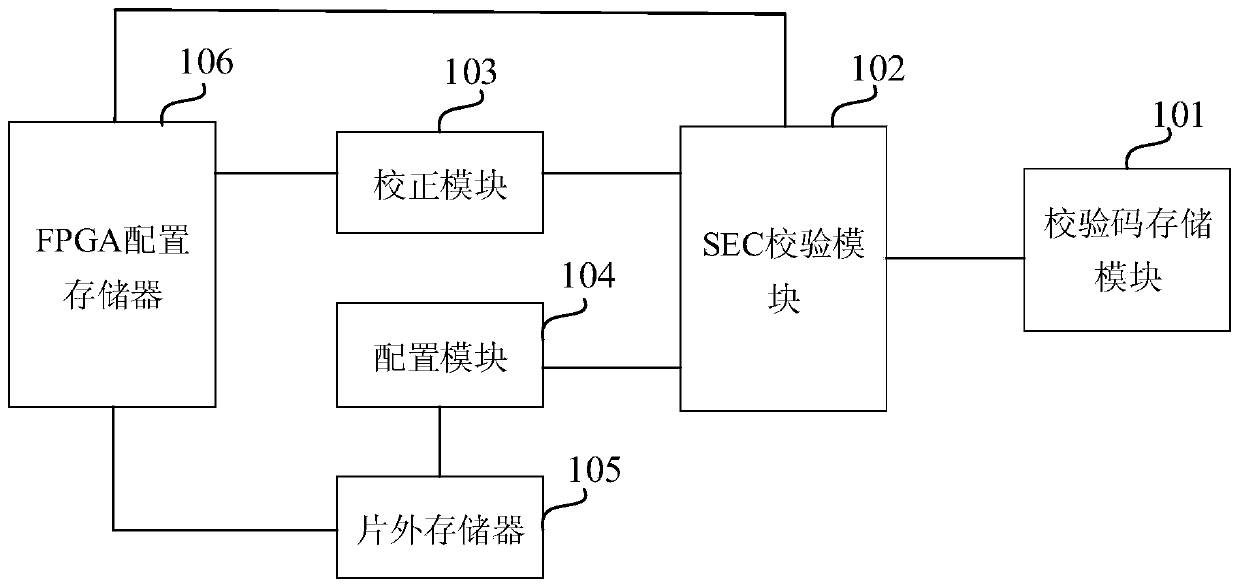

[0079] On the basis of the above embodiments, this embodiment provides a SEC verification device for FPGA configuration memory, which is used to implement the SEC verification method described in Embodiment 1.

[0080] See image 3 , image 3 It is a block diagram of an SEC verification method for FPGA configuration memory provided by an embodiment of the present invention. The SEC verification device of this embodiment includes a verification code storage module 101, an SEC verification module 102, a correction module 103, a configuration module 104, and an off-chip memory 105, wherein the verification code storage module 101 is used to obtain and save the reference ECC Check code; SEC check module 102 connects check code storage module 101, is used for carrying out CRC check and carries out ECC check to the data in FPGA configuration memory (106) according to described reference ECC check code; Calibration module 103 Connect SEC verification module 102 and FPGA configurati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More